電子設(shè)計(jì)自動(dòng)化(ElectronicDesignAutomation,EDA)技術(shù)是新興的電子設(shè)計(jì)自動(dòng)化工具,是目前世界電子設(shè)計(jì)的新技術(shù)方向和潮流[1]。在數(shù)字電路實(shí)驗(yàn)中,EDA作為一種重要的實(shí)驗(yàn)工具使傳統(tǒng)數(shù)字電路實(shí)驗(yàn)的教學(xué)模式得到了改變,實(shí)驗(yàn)的操作過(guò)程得到了一定的簡(jiǎn)化。

1EDA技術(shù)基本特征

EDA作為現(xiàn)代電子設(shè)計(jì)的核心,以大規(guī)模可編程邏輯器件(FPGA/COLD)為載體,以計(jì)算機(jī)為工作平臺(tái),在EDA軟件開(kāi)發(fā)環(huán)境下,采用硬件描述語(yǔ)言HDL(HardwareDescripTIonLanguage)編寫(xiě)設(shè)計(jì)文件,而一系列的編譯、綜合及優(yōu)化、布局布線、仿真[1],直到編程下載等工作都可自動(dòng)的完成。電路的邏輯功能與器件無(wú)關(guān),采用的是用硬件描述語(yǔ)言實(shí)現(xiàn),在整個(gè)硬件設(shè)計(jì)的過(guò)程中就像軟件設(shè)計(jì)一樣方便高效,對(duì)設(shè)計(jì)者的硬件電路方面的知識(shí)需求較低,各可編程器件之間可移植性好,因此適合多個(gè)設(shè)計(jì)者協(xié)同分工設(shè)計(jì),可縮短開(kāi)發(fā)周期。EDA技術(shù)具備采用高級(jí)硬件語(yǔ)言描述的特點(diǎn),能夠?qū)崿F(xiàn)系統(tǒng)級(jí)仿真具有較強(qiáng)的綜合性能[1]。它主要采用的是“自頂向下”和并行工程的設(shè)計(jì)方法,使設(shè)計(jì)者一開(kāi)始將產(chǎn)品生成周期、成本、質(zhì)量、開(kāi)發(fā)時(shí)間等一系列因素考慮到其中。然后系在對(duì)系統(tǒng)進(jìn)行設(shè)計(jì)的時(shí)候,需要先從整體要求入手,“自頂向下”將整個(gè)系統(tǒng)設(shè)計(jì)劃分為不同的功能。在設(shè)計(jì)中每個(gè)階段都可進(jìn)行仿真,并及時(shí)改正設(shè)計(jì)中發(fā)現(xiàn)的錯(cuò)誤。高層次系統(tǒng)采用硬件描述語(yǔ)言,具體的門(mén)級(jí)邏輯電路網(wǎng)表文件需要用邏輯綜合優(yōu)化工具來(lái)產(chǎn)生,而專用集成電路或印刷電路板的實(shí)現(xiàn)是對(duì)應(yīng)的物理級(jí)得到的。

我校EDA實(shí)驗(yàn)室主要采用的是QuartusII軟件。QuartusII是Altera公司推出的一款綜合性可編程邏輯器件開(kāi)發(fā)軟件,設(shè)計(jì)者可直接用硬件描述語(yǔ)言或原理圖進(jìn)行設(shè)計(jì),對(duì)于內(nèi)部器件不需要精通,且設(shè)計(jì)速度快。該軟件主要的特點(diǎn)為:運(yùn)行速度快、易學(xué)易用。

2EDA技術(shù)設(shè)計(jì)流程

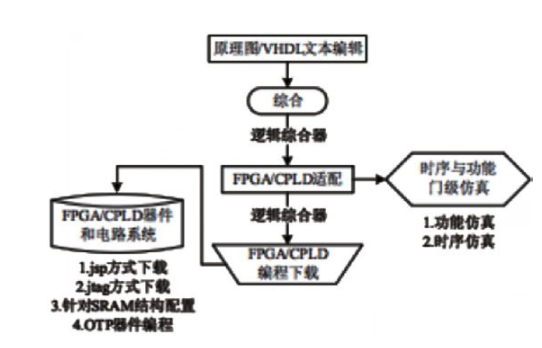

EDA技術(shù)設(shè)計(jì)流程如圖1所示。

(1)設(shè)計(jì)輸入。一個(gè)設(shè)計(jì)項(xiàng)目可由單個(gè)或多個(gè)原文件組織而成,它們可以是原理圖文件、混合輸入文件、VHDL文本文件等。

(2)綜合。綜合的關(guān)鍵是將VerilogHDL的軟件轉(zhuǎn)化為硬件電路,使兩者進(jìn)行掛鉤,完成綜合必須借助EDA軟件的綜合器。對(duì)供應(yīng)商提供的某一FPGA/CPLD產(chǎn)品可針對(duì)其源文件進(jìn)行綜合。設(shè)計(jì)人員設(shè)計(jì)的邏輯電路圖可利用EDA軟件提供的邏輯綜合和優(yōu)化功能將其自動(dòng)地轉(zhuǎn)化為門(mén)級(jí)電路,同時(shí)還會(huì)生成對(duì)應(yīng)的時(shí)序分析文件和網(wǎng)表文件。

(3)布線布局。在綜合之后的網(wǎng)表文件利用布局/布線適配器針對(duì)某一具體的器件進(jìn)行邏輯映射操作,將其映射操作(包括底層器件配置、邏輯分割、邏輯優(yōu)化、布線等操作)配置于目標(biāo)器件中。

(4)仿真。在EDA設(shè)計(jì)中重要的步驟就是仿真,即是下載編程前,利用EDA工具對(duì)適配產(chǎn)生的結(jié)果進(jìn)行模擬測(cè)試。在EDA設(shè)計(jì)過(guò)程中仿真可分為兩種不同級(jí)別的仿真測(cè)試,即時(shí)序仿真和功能仿真。其中,時(shí)序仿真是完全考慮了器件的硬件特性,并根據(jù)適配器產(chǎn)生的網(wǎng)表文件進(jìn)行仿真,仿真精度較高,因?yàn)樗咏谄骷恼鎸?shí)運(yùn)行。功能仿真不會(huì)考慮到硬件特性,對(duì)設(shè)計(jì)者所描述的邏輯功能進(jìn)行仿真,且完全滿足設(shè)計(jì)者的要求。

(5)編程下載。通過(guò)仿真驗(yàn)證設(shè)計(jì)完成后,采用Byteblaster下載電纜線以JTAG方式將適配生成的下載或配置文件下載至FPGA/CPLD器件內(nèi),方便于硬件的調(diào)試和驗(yàn)證。

上述步驟完成后,將統(tǒng)一對(duì)整個(gè)硬件系統(tǒng)進(jìn)行測(cè)試,以便發(fā)現(xiàn)設(shè)計(jì)中的問(wèn)題,得到及時(shí)的解決。

圖1EDA技術(shù)設(shè)計(jì)流程圖

3EDA技術(shù)的優(yōu)勢(shì)及在數(shù)字電路課程設(shè)計(jì)中的應(yīng)用

由于初學(xué)階段對(duì)硬件電路的功能及特性的不熟悉,導(dǎo)致在連接電路時(shí)易出錯(cuò),在檢查錯(cuò)誤過(guò)程中也會(huì)浪費(fèi)大量的時(shí)間和精力,一旦出錯(cuò),將導(dǎo)致電路出現(xiàn)一些不正常或無(wú)法預(yù)知的實(shí)驗(yàn)結(jié)果,使實(shí)驗(yàn)失敗,甚至還可能會(huì)出現(xiàn)損壞電路元器件、實(shí)驗(yàn)測(cè)試儀器及一些無(wú)法預(yù)測(cè)的安全事故。引入EDA后的數(shù)字電路實(shí)驗(yàn)可通過(guò)用硬件描述語(yǔ)言去描述電路的功能,將硬件采用“軟件”的方式去描述,大大降低了設(shè)計(jì)時(shí)間及設(shè)計(jì)難度。“自頂向下”的設(shè)計(jì)理念始終貫穿于EDA設(shè)計(jì)中,而人們也習(xí)慣于這種思維方式,因此電路設(shè)計(jì)的邏輯性較強(qiáng),同時(shí)也便于學(xué)習(xí)思維的發(fā)展和提高。

傳統(tǒng)的數(shù)字電路采用的是TTL邏輯器件進(jìn)行設(shè)計(jì)連線,由于實(shí)驗(yàn)條件受限,且隨著實(shí)驗(yàn)教學(xué)年限的增加,實(shí)驗(yàn)室設(shè)備的損壞、老化,需要定期的更新與維護(hù),才能保證正常實(shí)驗(yàn)的進(jìn)行。而電子技術(shù)的發(fā)展和更新日新月異,實(shí)驗(yàn)室的設(shè)備需要緊跟時(shí)代的步伐進(jìn)行更新?lián)Q代,多數(shù)學(xué)校設(shè)備的更新都不能緊跟技術(shù)的發(fā)展,將直接影響到學(xué)生對(duì)新知識(shí)的掌握,傳統(tǒng)實(shí)驗(yàn)的不足可由EDA仿真軟件彌補(bǔ),只需在計(jì)算機(jī)實(shí)驗(yàn)室安裝EDA軟件即可。當(dāng)學(xué)生熟練的掌握了EDA技術(shù)之后,可縮短數(shù)字電路實(shí)驗(yàn)的時(shí)間,對(duì)于所描述出的電路更容易進(jìn)行修改與調(diào)試,也能激發(fā)學(xué)生的興趣,這種將理論與實(shí)踐聯(lián)系起來(lái)的方式對(duì)于理論知識(shí)的掌握有很大的幫助。由于EDA技術(shù)十分廣博,在課堂學(xué)習(xí)之外還留給學(xué)生更多的想象空間,學(xué)生可通過(guò)自主創(chuàng)新,提高對(duì)數(shù)字電路的創(chuàng)新能力。

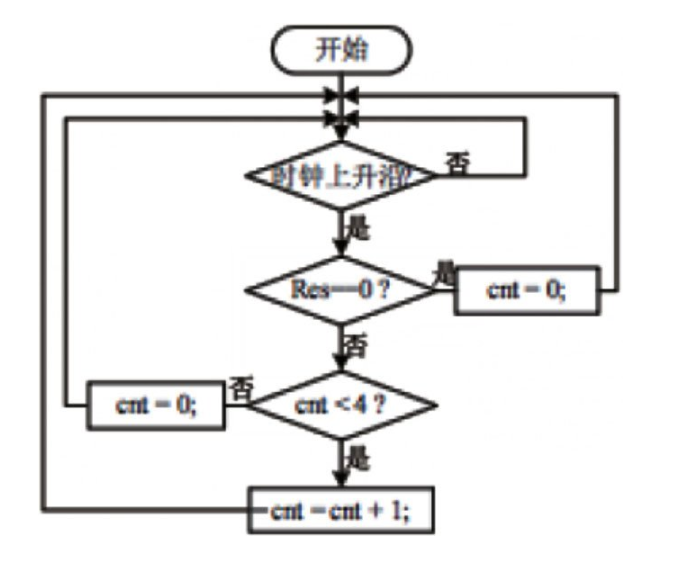

下面以設(shè)計(jì)一個(gè)五進(jìn)制加法計(jì)數(shù)器為例來(lái)討論EDA在數(shù)字邏輯電路實(shí)驗(yàn)中的具體應(yīng)用。在此設(shè)計(jì)一個(gè)帶有復(fù)位端的計(jì)數(shù)器,端口分別為:clk(時(shí)鐘,輸入端,位寬為1),res(復(fù)位,輸入端,位寬為1),cnt[2,0](計(jì)數(shù)端,輸出端,位寬為3)。時(shí)鐘clk為上升沿觸發(fā),復(fù)位res低有效,計(jì)數(shù)端cnt[2,0]有效數(shù)據(jù)范圍為3’b000~3’b100。程序流程圖如圖2所示。

圖2五進(jìn)制計(jì)數(shù)器流程圖

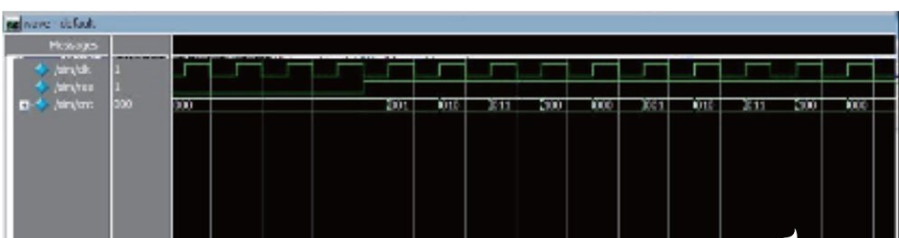

通過(guò)對(duì)五進(jìn)制計(jì)數(shù)器的分析,用VerilogHDL描述出功能后,在QuartusII11.0軟件上聯(lián)合Modelsim進(jìn)行仿真后,得到如圖3所示的仿真波形。

圖3五進(jìn)制加法計(jì)數(shù)器仿真波形

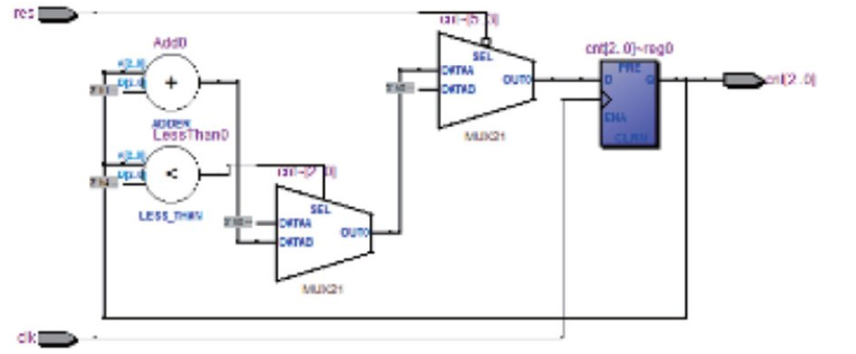

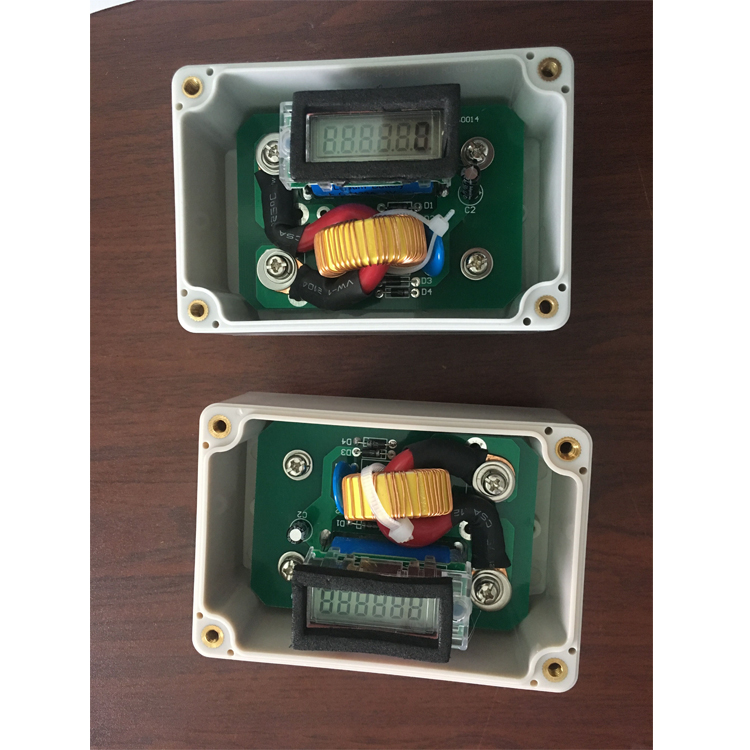

通過(guò)波形圖我們可以看出,所設(shè)計(jì)的邏輯功能和設(shè)計(jì)要求完全一致,通過(guò)QuartusII11.0綜合后的電路圖如圖4所示,我們可以觀察出五進(jìn)制計(jì)數(shù)器有哪些基本的邏輯器件所組成,將設(shè)計(jì)的項(xiàng)目通過(guò)QuartusII11.0軟件下載/配置到相對(duì)應(yīng)的實(shí)驗(yàn)箱,學(xué)生可以很直觀的觀察到計(jì)數(shù)器的邏輯功能。

圖4五進(jìn)制計(jì)數(shù)器綜合電路圖

我們必須熟悉各個(gè)邏輯器件以及要設(shè)計(jì)出的電路圖的具體的組成,才能構(gòu)造出總的電路圖,而對(duì)于EDA技術(shù)我們只要了解了它的功能,根據(jù)它的功能用硬件語(yǔ)言描述出來(lái),通過(guò)軟件的綜合后就可以得到對(duì)應(yīng)的電路圖。尤其是對(duì)于一些復(fù)雜的電路,利用EDA技術(shù)比傳統(tǒng)的實(shí)驗(yàn)教學(xué)更簡(jiǎn)單方便,更易掌握。

-

eda

+關(guān)注

關(guān)注

71文章

2886瀏覽量

176452 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2284瀏覽量

96029 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

526瀏覽量

44563

發(fā)布評(píng)論請(qǐng)先 登錄

74LV4060-Q100二進(jìn)制紋波計(jì)數(shù)器規(guī)格書(shū)

74LV4060二進(jìn)制紋波計(jì)數(shù)器規(guī)格書(shū)

74HC390;74HCT390雙十進(jìn)制波紋計(jì)數(shù)器規(guī)格書(shū)

74HC4520;74HCT4520同步二進(jìn)制計(jì)數(shù)器規(guī)格書(shū)

74LV393雙路4位二進(jìn)制紋波計(jì)數(shù)器規(guī)格書(shū)

74HC193;74HC7193二進(jìn)制加減計(jì)數(shù)器規(guī)格書(shū)

74HC191可預(yù)置同步4位二進(jìn)制加減計(jì)數(shù)器規(guī)格書(shū)

雷擊計(jì)數(shù)器的概述與應(yīng)用分析

五進(jìn)制加法計(jì)數(shù)器的EDA技術(shù)應(yīng)用

五進(jìn)制加法計(jì)數(shù)器的EDA技術(shù)應(yīng)用

評(píng)論