最近一系列事件再次表明,制約中國芯片產業發展的主要因素已集中到制造能力。如何快速提升制造能力,推動芯片產業發展?只有不斷地研發和創新。

在芯片界,摩爾定律一直占據統治地位。

摩爾定律接下來是終結還是延續,已成為過去十年芯片界熱議的話題。

摩爾定律自1965年發明以來,一直引領著世界半導體產業向實現更低的成本、更強的性能、更高的經濟效益的目標前進。然而,隨著半導體技術逐漸逼近硅工藝尺寸極限,原摩爾定律導出的“IC的集成度約每隔18個月翻一倍,而性能也將提升一倍”的規律將受到挑戰。

為此, ITRS組織針對半導體產業中遠期發展的挑戰,在技術路線制定上,提出選擇兩種發展方式(如圖1):一是繼續沿著摩爾定律按比例縮小的方向前進,專注于硅基CMOS技術;二是按“后摩爾定律”的多重技術創新應用向前發展,即在產品多功能化(功耗、帶寬等)需求下,將硅基CMOS和非硅基等技術相結合,以提供完整的解決方案來應對和滿足層出不窮的新市場發展。

· 繼續使用先進節點,邁向5納米及以下

使用先進節點的好處很多,晶體管密度更大、占用空間更少、性能更高、功率更低,但挑戰也越來越難以克服。

極小尺寸下,芯片物理瓶頸越來越難以克服。尤其在近幾年,先進節點走向10nm、7nm、5nm,問題就不再只是物理障礙了,節點越進化,微縮成本越高,能擔負巨額研發費用并實現盈利的設計公司越來越少。

根據公開報道,28nm節點設計成本約為5000萬美元,而到5nm節點,設計總成本已經飆高到逾5億美元,相當于逾35億人民幣。先進工藝如果只能提升性能,無法有效降低甚至守住成本,選擇最先進工藝的客戶將變得越來越有限。

· 以“三維集成”延續摩爾定律

幸運的是,每當摩爾定律被唱衰將走到盡頭,總會激發出科學家和工程師們創新構想,提出力挽狂瀾的突破性技術,將看似走向終結的摩爾定律以“后摩爾定律”的形式延續下去。

“后摩爾定律”的實質是,它除了會延續摩爾定律對集成度、性能的追求外,還會利用更多的技術,例如模擬/射頻、高壓功率電源、MEMS傳感器、生物芯片技術及系統級封裝(SiP)等三維集成技術,以提供具有更高附加值的系統。

ITRS指出,在“后摩爾定律”范疇,隨著新興應用不斷出現,智能化微系統芯片將會進入三維集成時代。

三維集成技術概覽和兩條主要的工藝路線

三維集成電路又稱立體集成電路,是集成電路從傳統平面集成方式向垂直方向立體集成方式延伸的產物。三維集成電路的優勢在于:多層器件重疊結構使芯片集成度成倍提高;TSV和混合鍵合工藝使芯片間互連長度大幅度縮短,提高傳輸速度并降低了功耗;多種工藝混合集成,使集成電路功能多樣化;減少封裝尺寸,降低設計和制造成本。

三維集成技術可將多層集成電路芯片或晶圓堆疊鍵合,通過三維互連實現多層之間的電信號連接。三維集成技術能實現異質芯片互連結合,發揮出最高系統性能水平,是其獨特的最大優勢。

經過十來年的發展,三維集成技術逐漸形成兩條主要的工藝路線:晶圓間三維堆疊和封裝廠主導的芯片間三維互連。

· 晶圓間三維堆疊技術

通過鍵合堆疊和連通孔工藝的持續改進滿足芯片對更大帶寬、更小功耗的要求。其工藝目前主要用于圖像傳感器的生產,近些年,隨著物聯網、人工智能和5G對更大帶寬、更小功耗和更低延時等特性產品的要求,晶圓級三維集成開始應用于大容量存儲、存算一體、高性能計算等領域。代表廠家有Intel、TSMC、Samsung、SONY等。

· 多顆芯片間三維互連技術

芯片級三維集成,主要追求芯片間凸點(Bump)連接小型化,來提高集成度和芯片性能。其技術特點依托于封裝打線(Wire bond)和凸點(bump)為基礎,把不同功能的芯片通過毫米級的封裝工藝連接。代表廠家主要為半導體制造領域的后端封裝廠,如Amkor、SPIL、ASE、長電、華進等。

二者互有優劣,晶圓間堆疊工藝精度高、互聯密度大;但相較芯片間互連,其良率相對較低、對芯片尺寸匹配度要求高。

國內晶圓級三維集成技術平臺代表:武漢新芯

從2012年起,紫光集團旗下的武漢新芯就開始研發第一代晶圓級三維集成制造工藝,并于2013年成功實現背照式影像傳感器的量產,并同步開始第二代晶圓級三維集成技術的研發,2014年硅通孔堆疊技術實現量產。

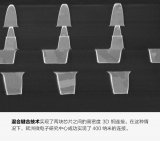

經過多年的發展和積累,武漢新芯的三維集成制造工藝水平與業界第一梯隊公司TSMC,索尼,三星等相當,產品已打入國際知名手機品牌以及國內知名品牌終端。在上兩代技術的基礎上,武漢新芯于2016年完成第三代三維集成技術的研發,成功研制出晶圓級混合鍵合技術,并成功應用于長江存儲64層3D NAND產品上,其技術能力已達到世界頂尖水平。

2018年,武漢新芯啟動第四代三維集成技術—多晶圓堆疊技術研發,并于2018年底完成工藝驗證,成功邁入多晶圓垂直整合領域。未來還將深耕三維集成領域,開發異質集成技術,目標成為國內一流的12寸三維集成技術工藝生產平臺。

通過自身半導體三維集成技術研發和產品拓展,武漢新芯將帶動上下游企業共同發展。在目前工藝條件下,提供更小的芯片面積,以及更高的集成度,力主獲得具有自主知識產權的核心技術體系和成套工藝解決方案,并將之應用于芯片的開發和生產,實現我國集成電路產業的局部突破和升級,使我國集成電路產業在三維集成技術這一領域,縮小與世界先進水平的差距。

-

集成電路

+關注

關注

5424文章

12042瀏覽量

368378 -

摩爾定律

+關注

關注

4文章

639瀏覽量

79862

發布評論請先 登錄

電力電子中的“摩爾定律”(1)

中國集成電路大全 接口集成電路

硅集成電路技術的優勢與挑戰

集成電路新思路:三維集成技術將使超越摩爾定律成為可能

集成電路新思路:三維集成技術將使超越摩爾定律成為可能

評論