上拉電阻和下拉電阻的主要作用

1. 提高電壓準(zhǔn)位

當(dāng)TTL電路驅(qū)動(dòng)CMOS電路時(shí),如果TTL電路輸出的高電平低于CMOS電路的最低高電平,這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值;OC門電路必須加上拉電阻,以提高輸出的高電平值。

2. 加大輸出引腳的驅(qū)動(dòng)能力

有的單片機(jī)引腳上也常使用上拉電阻。

3. N/A引腳(沒有連接的引腳)防靜電、防干擾

在CMOS芯片上,為了防止靜電造成損壞,不用的引腳不能懸空,一般接上拉電阻降低輸入阻抗,提供泄荷通路。同時(shí)引腳懸空就比較容易接收外界的電磁干擾。

4. 電阻匹配

抑制反射波干擾,長(zhǎng)線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻使電阻匹配,能有效的抑制反射波干擾。

5. 預(yù)設(shè)空間狀態(tài)/默認(rèn)電位

在一些CMOS輸入端接上拉或下拉電阻是為了預(yù)設(shè)默認(rèn)電位。當(dāng)不用這些引腳時(shí),這些輸入端下拉接低電平或上拉接高電平。I2C等總線上空閑時(shí)的狀態(tài)是由上下拉電阻獲得的。

6. 提高芯片輸入信號(hào)的噪聲容限

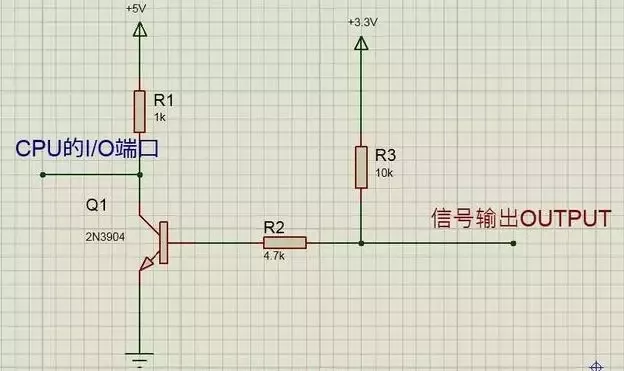

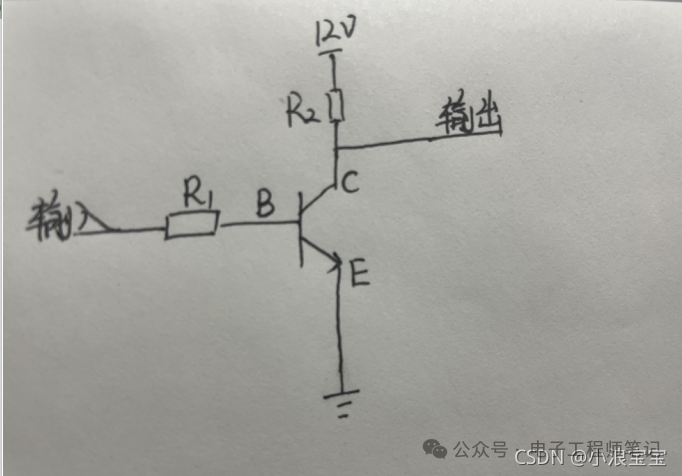

輸入端如果是高阻狀態(tài),或高阻抗輸入端處于懸空狀態(tài),此時(shí)需要加上拉或下拉電阻,以免受到隨機(jī)電平的影響,進(jìn)而影響電路工作。同樣,如果輸出端處于被動(dòng)狀態(tài),需要加上拉或下拉電阻,如輸出端僅僅是一個(gè)三極管的集電極,還可以提高芯片輸入信號(hào)的噪聲容限,增強(qiáng)抗干擾能力。 在BJT晶體三極管的基極端,上拉電阻和下拉電阻也起著至關(guān)重要的作用。在三極管的電路應(yīng)用中,串接在基極上的電阻起限制基極電流的作用,如圖1中的R2所示:

圖1

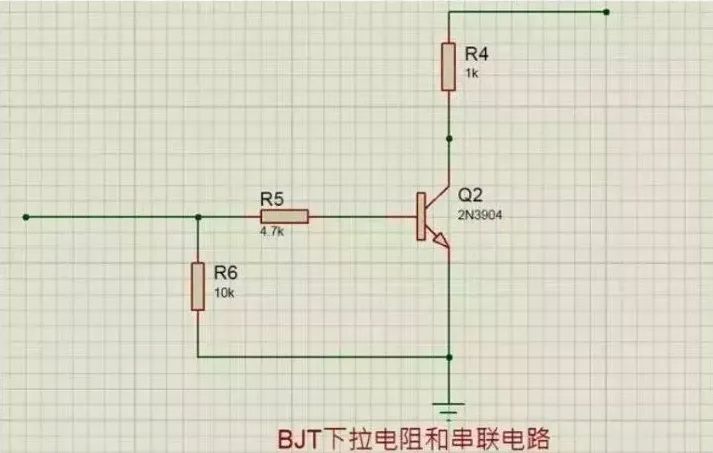

如圖2中的R5所示,上拉電阻使三極管基極的輸入電平在默認(rèn)情況下是高電平輸入,當(dāng)CPU有低電平信號(hào)輸出時(shí),外圍電路響應(yīng),下拉電阻使晶體管的基極輸入在默認(rèn)情況下拉到低電平,如圖2中的R6所示。

圖2

-

CMOS

+關(guān)注

關(guān)注

58文章

5988瀏覽量

238068 -

上拉電阻

+關(guān)注

關(guān)注

5文章

366瀏覽量

31051

原文標(biāo)題:5分鐘領(lǐng)悟上拉電阻和下拉電阻的作用!

文章出處:【微信號(hào):Mouser-Community,微信公眾號(hào):貿(mào)澤電子設(shè)計(jì)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

上拉電阻的工作原理詳解

上拉電阻阻值怎么選擇

PGA411在設(shè)計(jì)的時(shí)候必須配置上拉和下拉電阻嗎?可否直接連到電源和地上?

TLV320AIC3100原理圖,音頻輸入電路MIC的上拉電阻R1303和下拉電阻R1304是否需要?

上拉電阻和下拉電阻的主要作用

上拉電阻和下拉電阻的主要作用

評(píng)論