全加器邏輯表達(dá)式

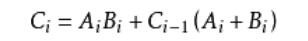

一位全加器的表達(dá)式如下:

Si=Ai⊕Bi⊕Ci-1

第二個(gè)表達(dá)式也可來用一個(gè)異或門來代替或門對(duì)其中兩個(gè)輸入信號(hào)進(jìn)行求和:

其中Ai為被加數(shù),Bi為加數(shù),相鄰低位來的進(jìn)位數(shù)為Ci-1,輸出本位和為Si。向相鄰高位進(jìn)位數(shù)為Ci。一位全加器可以處理低位進(jìn)位,并輸出本位加自法進(jìn)位。多個(gè)一位全加器進(jìn)行級(jí)聯(lián)可以得到多位全加器。常用二進(jìn)制四位全加器74LS283。

全加器的邏輯功能

當(dāng)多位數(shù)相加時(shí),半加器可用于最低位求和,并給出進(jìn)位數(shù)。第二位的相加有兩個(gè)待加數(shù)![]() 和

和![]() ,還有一個(gè)來自前面低位送來的進(jìn)位數(shù)

,還有一個(gè)來自前面低位送來的進(jìn)位數(shù)![]() .這三個(gè)數(shù)相加,得出本位和數(shù)(全加和數(shù))

.這三個(gè)數(shù)相加,得出本位和數(shù)(全加和數(shù))![]() 和進(jìn)位數(shù)

和進(jìn)位數(shù)![]() .這種就是“全加“,下表為全加器的邏輯狀態(tài)表。

.這種就是“全加“,下表為全加器的邏輯狀態(tài)表。

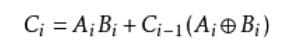

全加器可用兩個(gè)半加器和一個(gè)“或“門組成。

如上圖(a)所示。![]() 和

和![]() 在第一個(gè)半加器中相加,得出的結(jié)果再和

在第一個(gè)半加器中相加,得出的結(jié)果再和![]() 在第二個(gè)半加器中相加,即得出全加和

在第二個(gè)半加器中相加,即得出全加和![]() 。兩個(gè)半加器的進(jìn)位數(shù)通過”或“門輸出作為本位的進(jìn)位數(shù)

。兩個(gè)半加器的進(jìn)位數(shù)通過”或“門輸出作為本位的進(jìn)位數(shù)![]() 。全加器也是一種組合邏輯電路,其圖形符號(hào)如上圖(b)所示。

。全加器也是一種組合邏輯電路,其圖形符號(hào)如上圖(b)所示。

-

全加器

+關(guān)注

關(guān)注

10文章

62瀏覽量

28834

發(fā)布評(píng)論請(qǐng)先 登錄

labview如何使用VISA串口資源查找的正則表達(dá)式提取串口的資源名稱?

干貨分享 | 零基礎(chǔ)上手!TSMaster圖形信號(hào)表達(dá)式實(shí)操指南

數(shù)字電路—22、時(shí)序邏輯電路

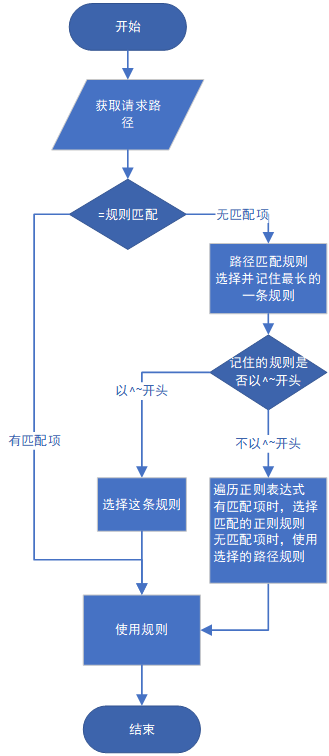

詳解nginx中的正則表達(dá)式

Verilog表達(dá)式的位寬確定規(guī)則

半加器和全加器的區(qū)別是什么

半加器和全加器的功能特點(diǎn)

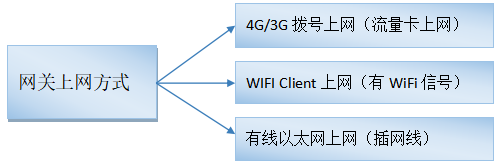

通過工業(yè)智能網(wǎng)關(guān)實(shí)現(xiàn)中間變量表達(dá)式的快速配置

nginx中的正則表達(dá)式和location路徑匹配指南

求助,以下恒流源電路Io的計(jì)算表達(dá)式怎么計(jì)算?

數(shù)字邏輯怎么把邏輯圖畫成電路圖

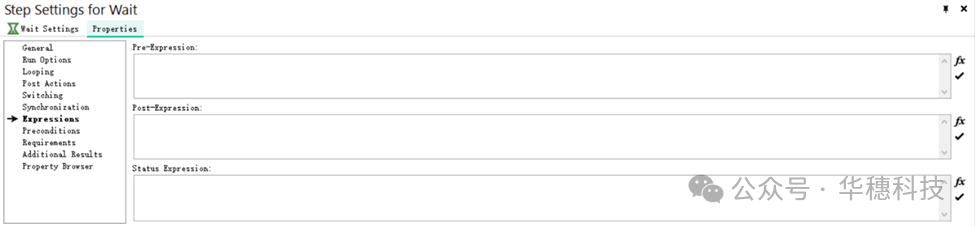

TestStand表達(dá)式中常用的語法規(guī)則和運(yùn)算符使用

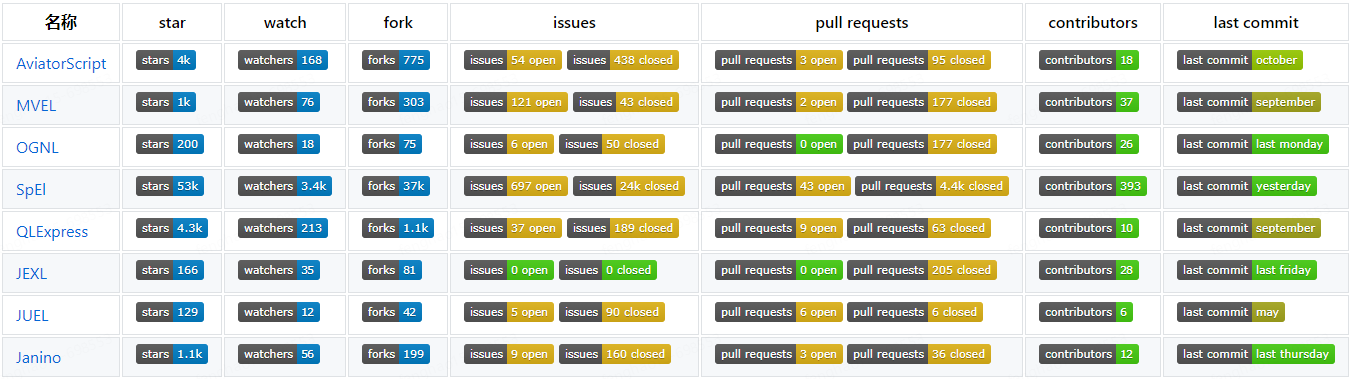

Java表達(dá)式引擎選型調(diào)研分析

全加器邏輯表達(dá)式_全加器的邏輯功能

全加器邏輯表達(dá)式_全加器的邏輯功能

評(píng)論