一切歷史都是當代史。

如果說在2019 年年中三星宣稱將在2021年推出其“環(huán)繞式柵極(GAA)”技術取代FinFET晶體管技術,F(xiàn)inFET猶可淡定;而到如今,英特爾表示其5nm制程將放棄FinFET而轉向GAA,就已有一個時代翻篇的跡象了。三大代工巨頭已有兩大廠商選擇了GAA,作為代工老大的臺積電路線雖“按兵不動”,但似乎已無懸念,F(xiàn)inFET真的走到歷史的終結了嗎?

FinFET的榮光

畢竟當FinFET以“拯救者”的形象登場時,它承載著摩爾定律持續(xù)向前攻伐的重要“使命”。

隨著制程工藝的升級,晶體管的制造愈加困難。1958年的第一個集成電路觸發(fā)器僅由兩個晶體管構建而成,而如今芯片已包含超過10億個晶體管,這一動力來自于摩爾定律指揮下的平面硅制造工藝的不斷進階。

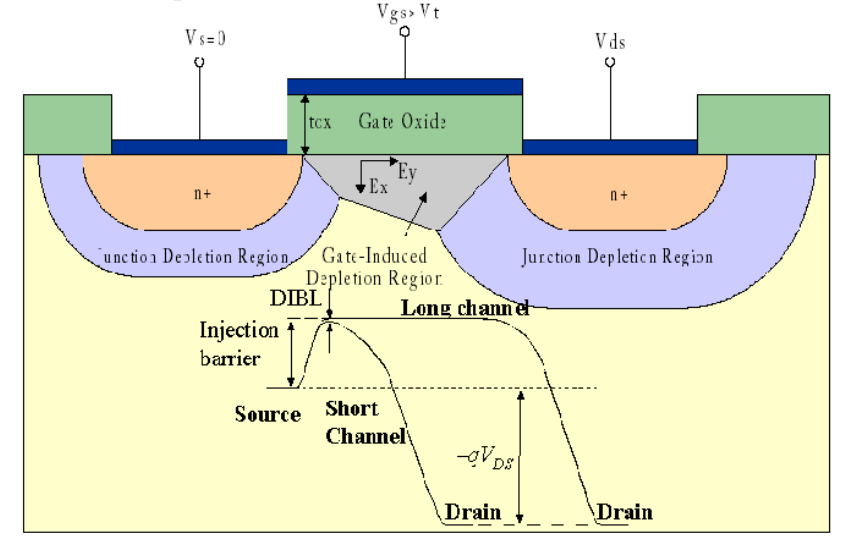

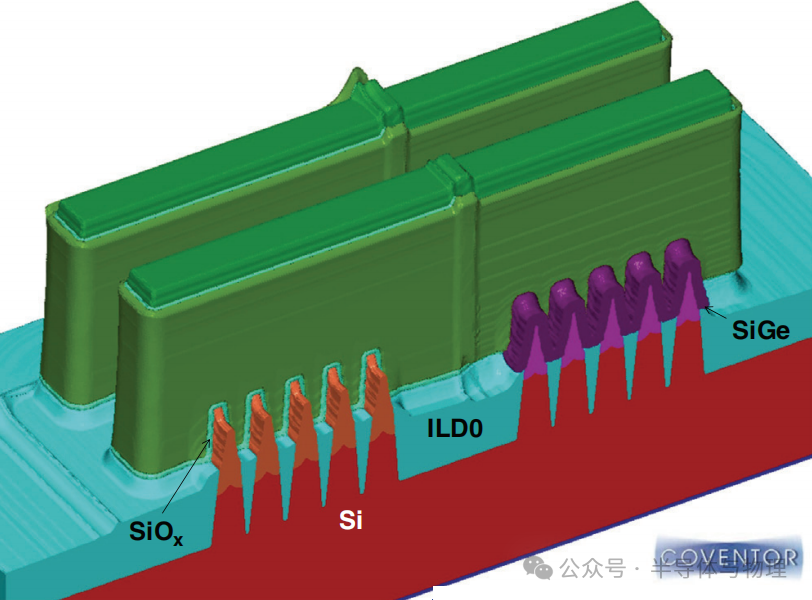

而當柵極長度逼近20nm大關時,對電流控制能力急劇下降,漏電率相應提高,傳統(tǒng)的平面MOSFET結構看似走到“盡頭”。業(yè)界大拿胡正明教授提出了兩種解決途徑:一種是立體型結構的FinFET晶體管,另一種是基于SOI的超薄絕緣層上硅體技術FD-SOI晶體管技術。

FinFET和FD-SOI使摩爾定律得以延續(xù)傳奇,之后兩者卻走出了不同的發(fā)展道路。FinFET工藝先拔頭籌,英特爾最早于2011年推出了商業(yè)化的FinFET工藝技術,顯著提高了性能并降低了功耗,之后臺積電采用 FinFET技術亦取得了巨大的成功,隨后FinFET大放異彩,成為全球主流晶圓廠的“不二”選擇。

相較之下,F(xiàn)D-SOI工藝似乎一直活在FinFET的陰影中。盡管其工藝漏電率低,功耗亦有優(yōu)勢,制成的芯片在物聯(lián)網(wǎng)、汽車、網(wǎng)絡基礎設施、消費類等領域均有用武之地,加上三星、格芯、IBM、ST等巨頭的力推,在市場業(yè)已打開了一片天地。但業(yè)內(nèi)資深人士指出,由于其襯底成本高,越往上走的尺寸越難以做小,最高水平最多走到12nm,后續(xù)難以為繼。

盡管FinFET在“二選一”的對壘中先聲奪人,但伴隨著物聯(lián)網(wǎng)、人工智能、智能駕駛等應用對IC提出了全新挑戰(zhàn),尤其是FinFET的制造、研發(fā)成本越來越高,F(xiàn)inFET雖到7nm及5nm猶能高歌猛進,但工藝歷史的流向似已然注定再次“轉向”。

為何是GAA?

隨著三星率先“垂范”,以及英特爾的跟進,GAA已儼然成為接棒FinFET的新貴。

與FinFET的不同之處在于,GAA設計通道的四個面周圍有柵極,減少漏電壓并改善了對通道的控制,這是縮小工藝節(jié)點時的基本步驟。通過使用更高效的晶體管設計,加上更小的節(jié)點,將能實現(xiàn)更好的能耗比。

資深人士對此也提及,工藝節(jié)點不斷前進的動能在于提升性能、降低功耗。而當工藝節(jié)點進階到3nm時,F(xiàn)inFET經(jīng)濟已不可行,將轉向GAA。

三星就樂觀認為,GAA技術相比7nm制程能夠提升35%的性能、降低50%的功耗以及45%的芯片面積。據(jù)悉,搭載此項技術的首批3nm三星智能手機芯片將于2021年開始批量生產(chǎn),而對于性能要求更高的芯片如圖形處理器和數(shù)據(jù)中心的AI芯片將于2022年量產(chǎn)。

值得注意的是,GAA技術也有幾種不同的路線,未來的細節(jié)有待進一步驗證。而且,轉向GAA無疑涉及架構的改變,業(yè)內(nèi)人士指出這對設備提出了不同的要求,據(jù)悉一些設備廠商已在開發(fā)特殊的刻蝕、薄膜設備在應對。

新華山論劍?

在FinFET市場,臺積電一支獨秀,三星、英特爾在奮力追趕。如今看來GAA已箭在弦上,問題是膠著的“三國殺”又會呈現(xiàn)怎樣的此消彼長?

從三星的語境來看,三星自認押注的GAA技術領先對手一兩年,將在這一領域奠定和保持其先發(fā)優(yōu)勢。

但英特爾亦是雄心勃勃,意在GAA上重奪領導地位。英特爾宣稱將在2021年推出7nm制程技術,并將在7nm制程的基礎上發(fā)展5nm。業(yè)內(nèi)估計最快2023年就能初見其5nm工藝“真容”。

盡管三星是GAA技術的領頭羊,但考慮到英特爾在工藝技術上的實力,其GAA工藝性能提升或更趨明顯,而英特爾也要自省不再走10nm工藝的“長征”之路。

以往躊躇滿志的臺積電此次反而異常低調與謹慎,盡管臺積電宣稱2020年準備量產(chǎn)的5nm制程依舊采用FinFET工藝,但預計其3nm工藝將于2023年甚至會提前至2022年量產(chǎn),只是尚未公布預計的制程方式。根據(jù)臺積電官方的說法,其3nm相關細節(jié)將在4月29日的北美技術論壇上公布。屆時,臺積電又會祭出怎樣的奇招呢?

GAA的戰(zhàn)役已然硝煙四起。

-

晶體管

+關注

關注

77文章

10019瀏覽量

141610 -

FinFET

+關注

關注

12文章

257瀏覽量

91163

發(fā)布評論請先 登錄

體硅FinFET和SOI FinFET的差異

FRED的光路和光路歷史記錄

FinFet Process Flow-源漏極是怎樣形成的

FinFet Process Flow—啞柵極的形成

機智云歷史數(shù)據(jù)導出與排查指南

FormFactor發(fā)布2024財年第三季度財報,收入創(chuàng)歷史新高

你認為嵌入式軟件開發(fā)的盡頭是什么?

FinFET到了歷史的盡頭?

FinFET到了歷史的盡頭?

評論