文章來源:老虎說芯

原文作者:老虎說芯

本文通過介紹傳統平面晶體管的局限性,從而引入FinFET技術的原理、工藝和優勢。

FinFET技術在晶圓制造中引入了一種創新的三維晶體管結構,通過增強柵極控制和降低漏電流,實現了更高效的晶體管性能。這對于實現更小、更快、更節能的半導體器件是至關重要的。隨著半導體工藝節點的不斷縮小,FinFET技術的應用也變得越來越普遍和重要。

背景:傳統平面晶體管的局限性

在傳統的平面金屬氧化物半導體場效應晶體管(MOSFET)中,隨著工藝節點的縮小(比如從90nm到65nm再到更小的節點),我們遇到了以下技術挑戰:

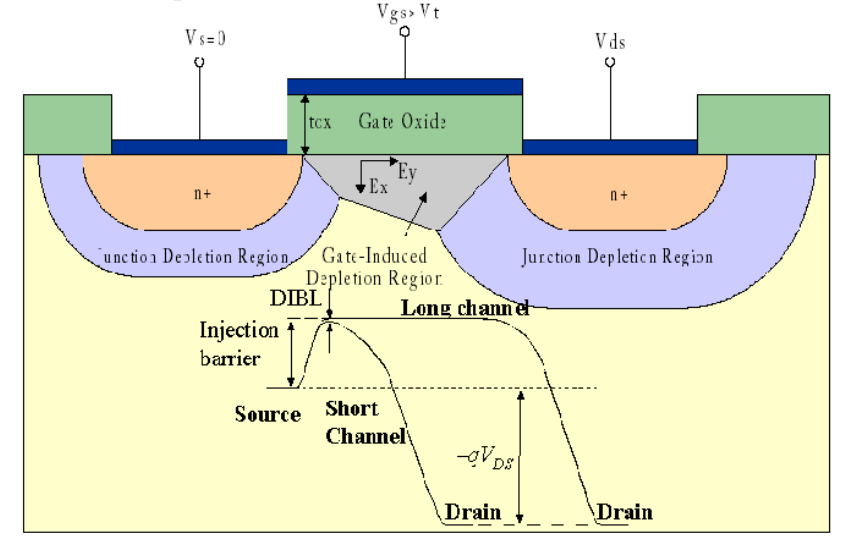

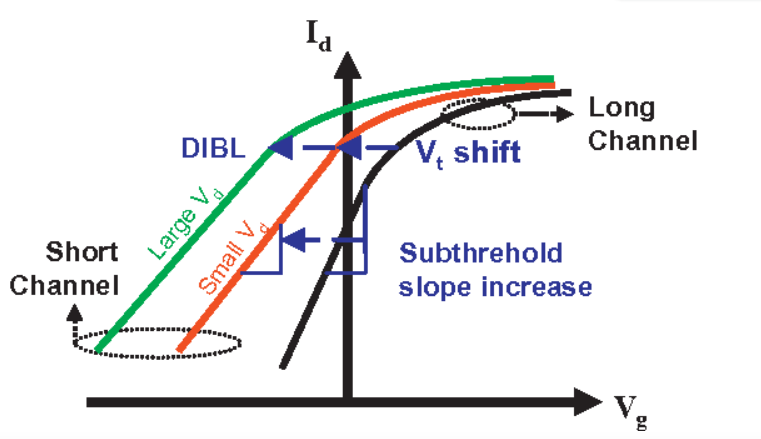

短溝道效應:隨著晶體管的柵極長度縮短,柵極對溝道的控制能力減弱,導致漏電流增加和開關速度降低。

漏電流增加:漏電流(off-state leakage current)增加,會導致靜態功耗顯著上升。

亞閾值擺幅問題:傳統MOSFET的亞閾值擺幅(Subthreshold Slope)受限于60 mV/decade,這限制了其在低功耗操作下的開關效率。

FinFET技術的引入

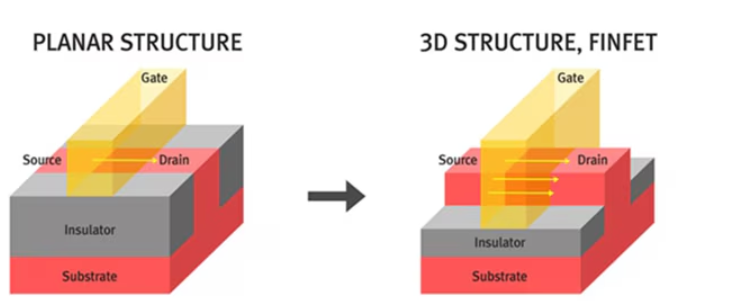

FinFET(鰭式場效應晶體管)是一種三維結構的晶體管技術,通過以下幾個方面改善了傳統MOSFET的性能:

增強的電流驅動能力:FinFET通過立體結構,允許更大的驅動電流。這是因為FinFET的溝道是垂直于基板表面立起來的“鰭”,使得在同樣的占地面積上可以獲得更大的有效寬度。

更好的柵極控制:在FinFET中,柵極可以從三面包圍“鰭”狀的溝道,這大大增強了柵極對溝道的電場控制能力,從而顯著降低短溝道效應。

降低漏電流:通過更好的柵極控制和較短的有效溝道長度,FinFET能夠顯著降低漏電流。這對于實現低功耗電路至關重要。

FinFET的制造工藝挑戰

盡管FinFET具有明顯的技術優勢,但其制造工藝也帶來了新的挑戰:

更復雜的工藝流程:制造FinFET需要更復雜的工藝步驟,包括多個光刻和刻蝕步驟,以形成精確的三維結構。

設備和工藝的升級:需要先進的設備和工藝,比如高精度的光刻技術(EUV光刻)和高選擇性的刻蝕工藝。

良率控制:三維結構的復雜性增加了缺陷的可能性,需要更嚴格的良率控制和檢測技術。

FinFET的優勢驗證

隨著制程工藝向10nm及以下節點推進,FinFET技術的優勢變得愈加明顯:

提高性能和降低功耗:通過更好的控制能力和更低的漏電流,FinFET能夠在保持性能的同時,顯著降低功耗。

提高集成度:更小的單元尺寸和更高的電流密度使得芯片可以集成更多的功能和電路。

-

MOSFET

+關注

關注

150文章

8242瀏覽量

218447 -

晶圓

+關注

關注

52文章

5115瀏覽量

129158 -

晶體管

+關注

關注

77文章

9977瀏覽量

140632 -

FinFET

+關注

關注

12文章

255瀏覽量

90934 -

晶圓制造

+關注

關注

7文章

292瀏覽量

24429

原文標題:為什么晶圓先進制程需要FinFET?

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FinFET技術在晶圓制造中的優勢

FinFET技術在晶圓制造中的優勢

評論