今年ISSCC的議題涵蓋毫米波、機器學習、量子等熱門關鍵技術。

摩爾定律逼近極限以及越來越昂貴的先進半導體制程工藝,讓整個芯片產業都面臨困境。此前,業界通過將多個功能集成到單一芯片中來滿足需求,比如手機SoC。但是,SoC集成的復雜度和成本越來越高,讓這種方式面臨挑戰。

在這樣的背景下,有一些先進的處理器通過先進的封裝和高帶寬連接技術,將不同的小芯片(Chiplet)封裝成一顆芯片,讓芯片性能夠持續增加的同時保持成本的可控性,英特爾和AMD就是這種技術的重要推動力。

在ISSCC 2020上,英特爾在2月18日的SESSION 8中介紹了10nm與22FFL混合封裝的Lakefield處理器,采用的是英特爾的Foveros 3D封裝技術,封裝尺寸為12 X 12 X 1毫米。Lakefield作為英特爾首款采用了Foveros技術的產品,能夠在指甲大小的封裝中取得性能、能效的優化平衡。

圖1:Foveros 3D封裝技術,來源英特爾。

Foveros封裝技術改變了以往將不同IP模塊放置在同一2D平面上的做法,改為3D立體式堆疊。做個類比,傳統的方式是將芯片設計為一張煎餅,而新的設計則是將芯片設計成1毫米厚的夾心蛋糕。這樣可以提升靈活性,并且不需要整個芯片都采用最先進的工藝,成本也可以更低。

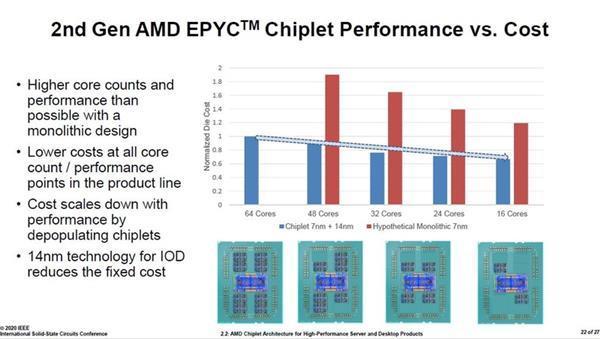

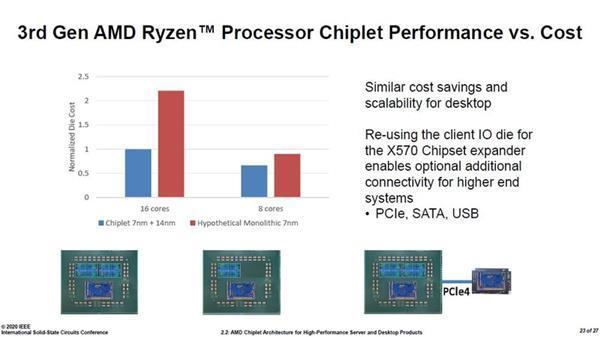

AMD大獲成功的Epyc同樣使用類似的思路,在此次的ISSCC上,AMD在SESSION 2中介紹了使用小芯片架構的高性能服務器產品及性價比的優勢。

兩者的不同點在于,Epyc使用的是2.5D架構的封裝,英特爾使用的是3D堆疊封裝。

在ISSCC 2020會議上,法國公司Leti也發表了一篇論文,介紹了他們使用3D堆棧、有源中介層等技術制造的96核芯片。

根據他們的論文,這個96核芯片有6組CPU單元組成,每組有16個核心,不過Leti沒提到CPU內核使用的是ARM還是RISC-V,亦或者是其他,但肯定會是低功耗小核心,使用的也是28nm FD-SOI工藝。

CEA-Leti的科學主管Pascal Vivet表示,如果要允許不同技術的多個小芯片供應商集成到系統中,有源插入器是小芯片技術的最佳選擇。

“如果要將接口不兼容的A供應商的小芯片與供應商B的小芯片集成在一起,需要一種將它們‘粘合’在一起的方法。” Pascal Vivet 說,“并且將它們‘粘合’在一起的唯一方法是使用插入器中的有源電路。”

這6組CPU核心使用了3D堆棧技術面對面配置,通過20um微凸點連接到有源中介層上,后者又是通過65nm工藝制造的TSV(硅通孔)技術連接。

在這個96核芯片上,除了CPU及TSV、中介層之外,還集成了調壓模塊、彈性拓撲總線、3D插件、內存-IO主控及物理層等。

據悉,該系統每平方毫米的傳輸速率可以達到3 TB/s,延遲僅為0.6納秒。

圖:CEA-Leti 96核芯片

總之,這款96核芯片集成了大量不同工藝、不同用途的核心,電壓管理、IO等外圍單元也集成進來了,是異構芯片的一次重要突破。

通過靈活高效、可擴展的緩存一致性架構,這個芯片最終可能擴展到512核,在高性能計算及其他領域有望得到推廣應用。

-

處理器

+關注

關注

68文章

19811瀏覽量

233605 -

英特爾

+關注

關注

61文章

10169瀏覽量

173963

發布評論請先 登錄

如何用一顆SOP8芯片實現色溫+亮度精準控制?

【「芯片通識課:一本書讀懂芯片技術」閱讀體驗】了解芯片怎樣制造

【「大話芯片制造」閱讀體驗】+ 芯片制造過程和生產工藝

用一顆5G的204B接口DA芯片,DA芯片的輸入時鐘大小和輸入數據的速率是怎么樣的關系?

【「大話芯片制造」閱讀體驗】+芯片制造過程工藝面面觀

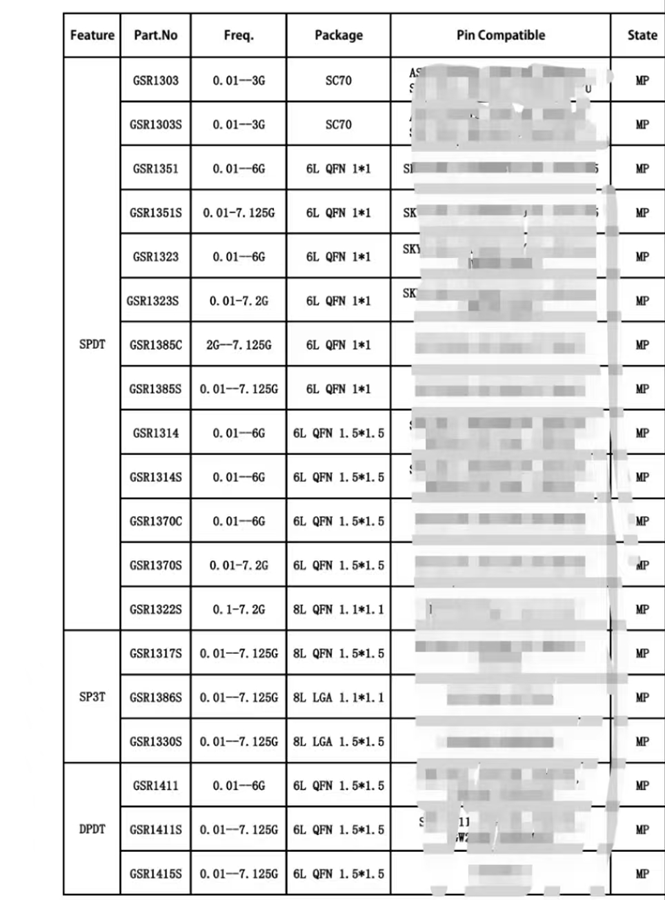

一顆射頻開關的獨白

神奇的“小芯片”設計,可在一顆芯片上使用不同工藝進行制造

神奇的“小芯片”設計,可在一顆芯片上使用不同工藝進行制造

評論