AMD近日正式發布了銳龍4000U、銳龍4000H系列移動APU(代號Renoir),采用7nm工藝、Zen 2架構,最多八個CPU核心、八個GPU計算單元(512SP),熱設計功耗15/45W。

發布會后,AnandTech參觀了AMD的展臺,驚喜地發現了銳龍4000 APU的裸片,旁邊還擺著64核心128線程撕裂者3990X的裸片,于是測量了一下它們的核心面積。

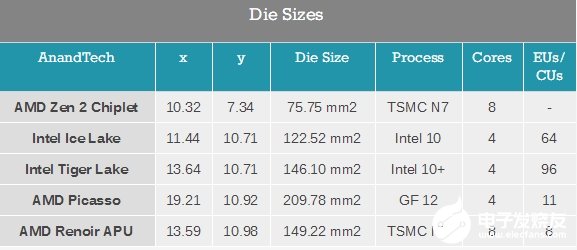

三代銳龍和三代撕裂者都采用了chiplet小芯片設計,每顆CPU Die內有八個核心,實測面積為10.32×7.24=75.75平方毫米(官方內核面積74平方毫米加一些額外填充)。

銳龍4000 APU內核實測長度13.59毫米、寬度10.98平方毫米,面積為149.27平方毫米。

這樣的面積下,結合臺積電7nm工藝每平方厘米0.09的缺陷指標,銳龍4000 APU的良品率就是90%左右,盡管這并未考慮制造良率,也是相當可觀的。

另外,銳龍4000 APU發布之前,就有猜測AMD會如何設計,是四個CPU核心加更多GPU核心,還是八個CPU核心加較少GPU核心。

結果,AMD不但塞進去八個CPU核心、15W熱設計功耗下加速頻率達到4.3GHz的同時,還放入了八個GPU計算單元并號稱性能比上代提升56%,非常精妙,也非常不容易。

順帶一提,GF 12nm工藝制造的銳龍3000 APU面積為209.78平方毫米,有四個CPU核心、11個GPU單元。

10nm+工藝的Intel Tiger Lake面積為146.10平方毫米,有四個CPU核心、96個GPU單元(當然AMD/Intel GPU單元沒有直接可比性)。

責任編輯:wv

-

amd

+關注

關注

25文章

5555瀏覽量

135753 -

APU

+關注

關注

0文章

142瀏覽量

23997

發布評論請先 登錄

40kw用多大電纜

BergStak HS? 0.50毫米平行扣卡連接器AMPHENOL

避雷接地線可以和室內接地線一起接嗎?避雷接地線用多大平方?

德州儀器MSPM0C1104 世界最小MCU 僅1.38平方毫米售價20美分

ALN4000-10-3530毫米波低噪聲放大器WENTEQ

ALN3750-13-3335毫米波低噪聲放大器WENTEQ

16管能穿幾根六類網線

用菊花鏈連接4片/8片/16片ADS1299,菊花鏈的前八個通道會出現雜波,怎么解決?

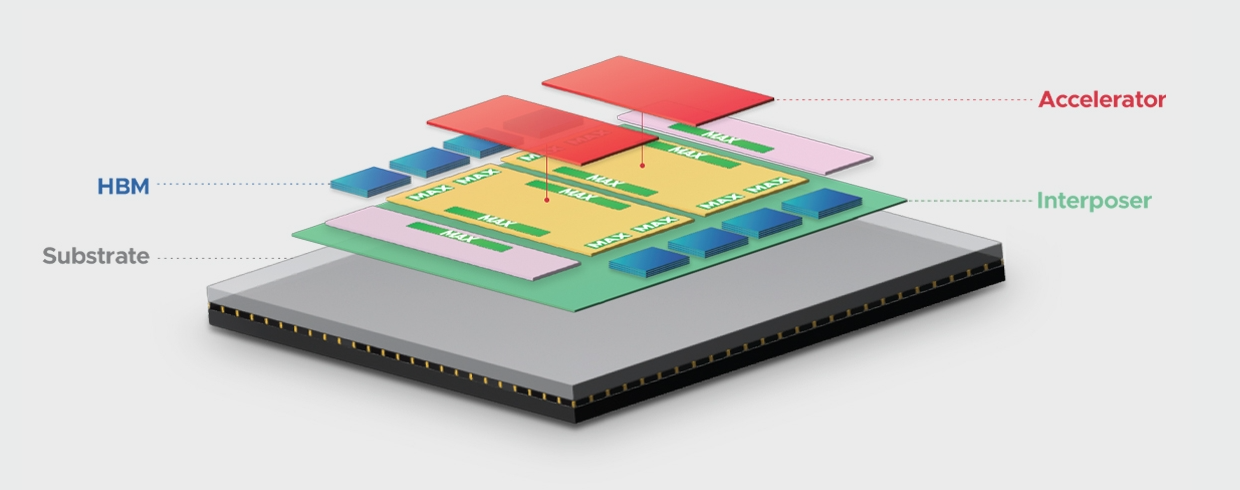

技術前沿探索:玻璃基板嵌入技術(GPE)與玻璃基板扇出封裝(eGFO)

銳龍4000 APU裸片到底有多大 149.27平方毫米面積竟塞下八個CPU核心

銳龍4000 APU裸片到底有多大 149.27平方毫米面積竟塞下八個CPU核心

評論