Silicon Lab公司的Si5372/71是單個PLL抖動衰減時鐘,集成了兩個外部(A級)和內部(J級)基準和該公司最新第四代DSPLL技術,以提供下一代相干光學應用的所需的性能.集成的基準不易受聲發射影響,從而消除了外接晶振,從而節省了空間和成本.多達4個輸出,滿足高速整數模式,在相位抖動45fs-rms(1MHz-40MHz)高達2.75GHz.每個輸出還可以配置成multiSynth模式任何頻率輸出,只要所增加頻率靈活性是需要的,比如時鐘正向誤差修正(FEC)還能提供90 fs-rms典型的相位抖動(12 kHz-20 MHz).Si5372/71還具有低到0.001ppb步控制的DCO控制,并能鎖住間隙時鐘輸入.輸入頻率范圍,差分為8 kHz- 750 MHz, LVCMOS為8 kHz - 250 MHz,高速整數模式的最大輸出頻率2.75GHz,典型抖動45 fs-rms(1 MHz–40 MHz);Multisynth模式的最大輸出頻率717.5 MHz,典型抖動為90 fs RMS(12 kHz–20 MHz).器件滿足以下規范ITU-T G.8262 (SyncE) EEC Options 1 and 2和ITU-T G.8262.1 (Enhanced SyncE) eEEC.主要用在相干光線路卡和模塊(100G/400G/600G)以及高速數據轉換器時鐘.本文介紹了Si5372/71主要特性,功能框圖,以及評估板Si5372 -EVB主要特性,功能框圖,電路圖和材料清單.

The Si5372/71 are single-PLL jitter attenuating clocks with both external (Grade A)and internal (Grade J) reference and Silicon Labs’ latest 4th generation DSPLL technologyto deliver the performance requirements of next generation coherent opticalapplications. The integrated reference is less susceptible to acoustic emissions andeliminates the need for external crystals that take up extra space and cost.

Up to four outputs can be assigned to high-speed integer mode capable of up to2.75 GHz at 45 fs-rms typical phase jitter (1 MHz–40 MHz). Each output may also beconfigured as multiSynth mode any-frequency outputs when added frequency flexibilityis required, such as clocking Forward Error Correction (FEC) while still delivering90 fs-rms typical phase jitter (12 kHz-20 MHz). The Si5372/71 also feature DCOcontrol with as low as 0.001 ppb step control and is able to lock to gapped clock inputs.

These devices are available with factory programming or can be programmedvia a serial interface with in-circuit programmable non-volatile memory (NVM) so thatthey always power up with a known frequency configuration. The loop filter is fullyintegrated on-chip eliminating the risk of potential noise coupling associated with discretesolutions. Programming the Si5372/71 is made easy with Silicon Labs’ Clock-Builder Pro?.

The Si5371 has two outputs, and the Si5372 has four outputs, with external crystal versions (Grade A) available in 7 mm x 7 mm 44-QFN packages and internal reference versions (Grade J) available in 7 mm x 7 mm 44-LGA packages.

Si5372主要特性:

? Supports High-speed line side clocks up to2.75 GHz

? Generates any output frequency in any formatfrom any input frequency

? Integrated reference (Grade J)

? Better acoustic emissions immunity

? Significantly smaller board area

? Enhanced hitless switching minimizes outputphase transients (0.2 ns typ)

? Input frequency range

? Differential: 8 kHz to 750 MHz

? LVCMOS: 8 kHz to 250 MHz

? High-speed Integer mode

? 45 fs-rmsTyp Jitter (1 MHz–40 MHz)

? Maximum output Frequency of 2.75 GHz

? Multisynth mode

? 90 fs RMS Typ Jitter (12 kHz–20 MHz)

? Maximum output Frequency of 717.5 MHz

? Meets requirements of:

? ITU-T G.8262 (SyncE) EEC Options 1 and 2

? ITU-T G.8262.1 (Enhanced SyncE) eEEC

? Status monitoring

? Si5372: 4 input, 4 output

? Si5371: 4 input, 2 output

? Drop-in compatible with Si5344H/42H

Si5372應用:

? Coherent optical line cards and modules (100G/400G/600G)

? High-speed data converter clocking

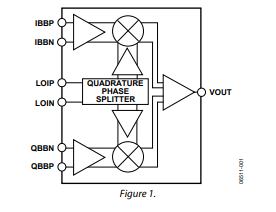

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/160002CB_0.jpg)

圖1.Si5372框圖表

評估板Si5372 –EVB

The Si5372-EVB is used for evaluating the Si5372 Any-Frequency, Any-Output, Jitter Attenuating Clock Multiplier. The Si5372 combines 4th generation DSPLL and Multisynth ? technologies to enable any-frequency clock generation for applications that require the highest level of jitter performance. There are two different EVBs for theSi5372. There is an A grade which uses an external XTAL reference and there is a Jgrade which has an internal XTAL reference. This user guide is intended for all versionsof the Si5372 EVB.

The device grade and revision is distinguished by a white 1inch x 0.187 inch label installed in the lower left hand corner of the board. In the examplebelow, the label "SI5372J-A-EB" indicates the evaluation board has been assembledwith an Si5372 device, Grade J, Revision A, installed. (For ordering purposes only,the terms “EB” and “EVB” refer to the board and the kit respectively. For the purposeof this document, the terms are synonymous in context.)The device The Si5372-EVBhas two independent input clocks and four independent output clocks. The Si5372-EVBcan be controlled and configured using the ClockBuilderPro? (CBPro) software tool.

評估板Si5372 -EVB主要特性:

? Si5372A-A-EB for evaluating externalXTAL version Si5372A

? Onboard 48 MHz XTAL or ReferenceSMA Inputs allow holdover mode ofoperation on the Si5372.

? Si5372J-A-EB for evaluating internal XTALversion Si5372J

? Powered from USB port or external powersupply.

? CBPro? GUI-programmable VDD supplyallows the device to operate from 3.3, 2.5,or 1.8 V.

? CBPro GUI-programmable VDDO suppliesallow each of the ten outputs to have itsown supply voltage, selectable from 3.3,2.5, or 1.8 V.

? CBPro GUI-controlled voltage, current,and power measurements of VDD and allVDDO supplies.

? Status LEDs for power supplies andcontrol/status signals of Si5372.

? SMA connectors for input clocks, outputclocks, and optional external timingreference clock.

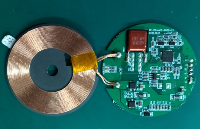

圖2.評估板Si5372 -EVB外形圖

評估板包括:

Seamless download from ClockBuilder Pro to EVB

SMA connectors for high quality measurements

No external clocks are required for free-run evaluation

Real-time power and junction temperature measurements

Access all registers, LED indicators and I/O

Most configurations can be powered by USB

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/1602016050_0.jpg)

圖3.評估板Si5372 -EVB功能框圖

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/16030131V_0.jpg)

圖4.評估板Si5372 -EVB電路圖(1)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/160402a10_0.jpg)

圖5.評估板Si5372 -EVB電路圖(2)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/160502U23_0.jpg)

圖6.評估板Si5372 -EVB電路圖(3)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/160602UT_0.jpg)

圖7.評估板Si5372 -EVB電路圖(4)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/160F2b95_0.jpg)

圖8.評估板Si5372 -EVB電路圖(5)

評估板Si5372 -EVB材料清單:

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/160P1bD_0.jpg)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/160Z2L23_0.jpg)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/16100350C_0.jpg)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/161102IE_0.jpg)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/1612014118_0.jpg)

圖9.評估板Si5372A-A-EVB電路圖(1)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/161302DL_0.jpg)

圖10.評估板Si5372A-A-EVB電路圖(2)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/1614024F1_0.jpg)

圖11.評估板Si5372A-A-EVB電路圖(3)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/1615035I0_0.jpg)

圖12.評估板Si5372A-A-EVB電路圖(4)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/1616024241_0.jpg)

圖13.評估板Si5372A-A-EVB電路圖(5)

評估板Si5372A-A-EVB材料清單:

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/161F25503_0.jpg)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/161P16401_0.jpg)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/161Z12050_0.jpg)

![[原創] Silicon Lab Si5372抖動衰減集成基準單PLL相干光學時鐘解決方案](/uploads/allimg/190926/1620015929_0.jpg)

-

dsp

+關注

關注

555文章

8142瀏覽量

355230 -

Silicon

+關注

關注

0文章

135瀏覽量

39116 -

數據轉換器

+關注

關注

1文章

374瀏覽量

28742

發布評論請先 登錄

每周推薦!電子工程師自學資料及各種電路解析

MDD整流二極管的伏安特性曲線解析及應用影響

ADL5372 1500MHz至2500MHz正交調制器技術手冊

華為通過BSI全球首批漏洞管理體系認證

電源負載主要特性和參數是什么?

滑動變阻器的主要特性和參數有哪些?

MLCC直流偏壓特性解析

半導體PN結的形成原理和主要特性

放大電路的頻率特性包括

解析 MEMS 車載與高溫振蕩器 SiT8920 系列 1 to 110 MHz 的卓越特性

傳感器電路圖解析

Silicon Lab bSi5372/71主要特性及電路圖解析

Silicon Lab bSi5372/71主要特性及電路圖解析

評論