第1步:規范

這些是我們要執行的 Cache Controller 的主要規范設計:

直接映射。

單銀行阻止緩存。

“寫入”匹配的直通策略。

在寫未命中時不寫分配或在周圍寫策略。

無寫緩沖區或其他優化。

標記數組已合并。

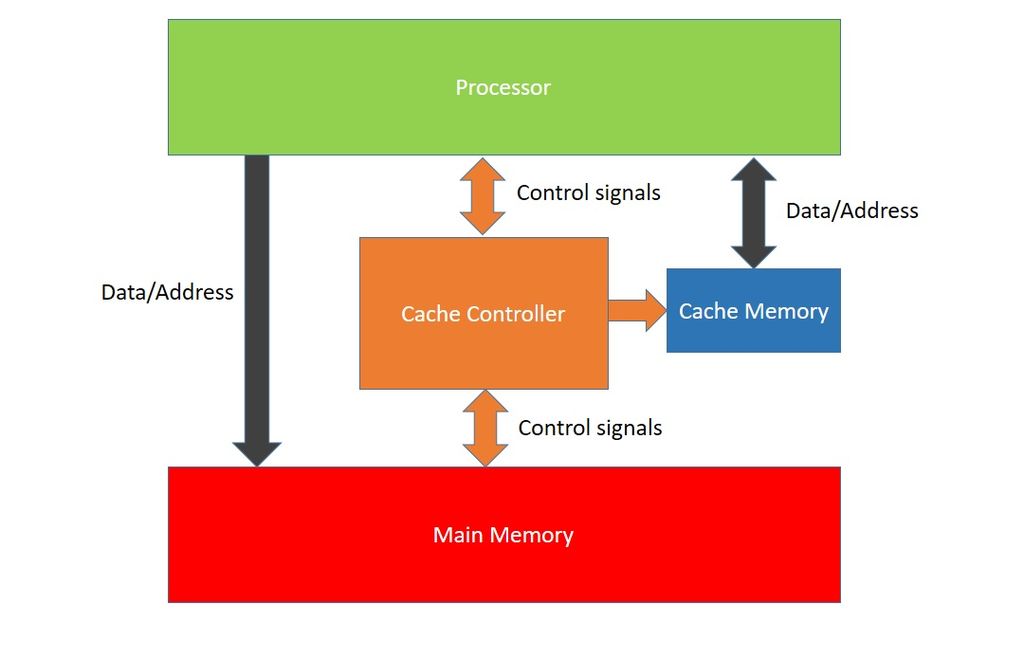

此外,我們將設計一個緩存和一個主存儲系統

高速緩存的默認(可配置)規格:

256字節單存儲高速緩存。

16個緩存行,每個緩存行(塊)= 16字節。

主內存的規格:

同步讀/寫內存。

多存儲區交錯存儲-四個存儲區。

每個存儲區大小= 1 kB。因此,總大小= 4 kB。

具有10位地址總線的字(4字節)可尋址存儲器。

更高的讀取帶寬。在一個時鐘周期內讀取數據寬度= 16字節。

寫入數據寬度= 4字節。

注意:如果您正在尋找4路關聯高速緩存控制器設計,請檢查我的較新版本

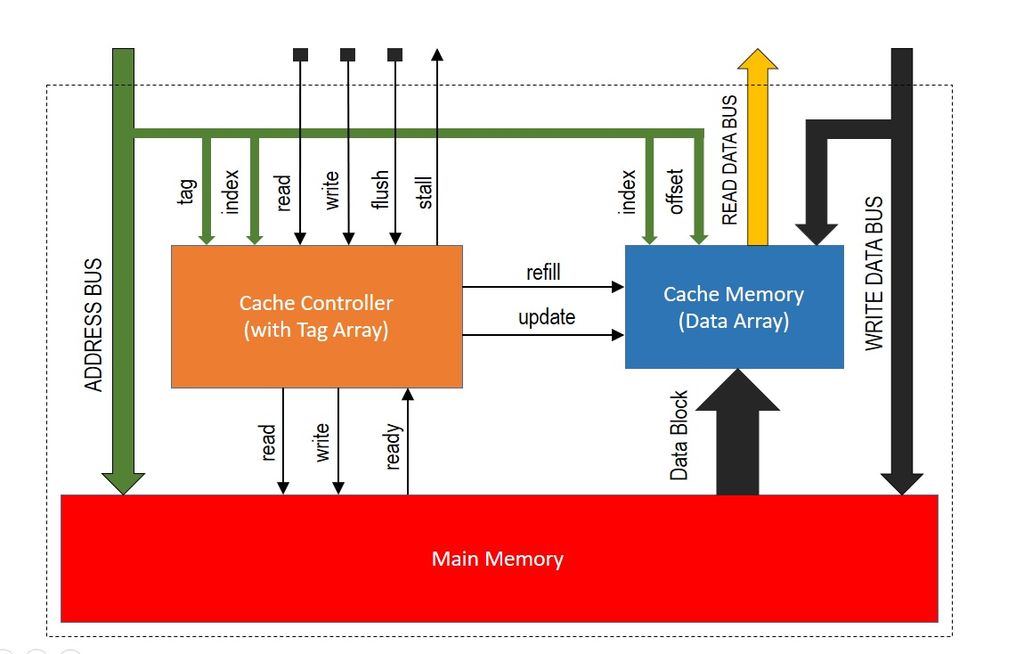

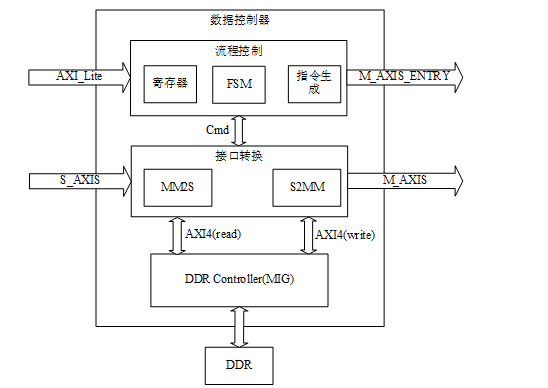

步驟2:整個系統的RTL視圖

頂部模塊的完整RTL表示形式如圖所示(不包括處理器)。總線的默認規格為:

所有數據總線均為32位總線。

地址總線= 32位總線(但是內存在這里只能尋址10位)。

數據塊= 128位(用于讀取的寬帶寬總線)。

所有組件均由同一時鐘驅動。

步驟3:測試環境

頂部模塊是使用測試臺進行測試,該測試臺僅對非流水線處理器進行建模(因為設計整個處理器絕非易事!)。測試臺經常向存儲器生成讀/寫數據請求。這模擬了處理器執行的所有程序中常見的典型“加載”和“存儲”指令。測試結果成功驗證了緩存控制器的功能。以下是觀察到的測試統計信息:

所有讀/寫未命中和命中信號均正確生成。

所有讀取/寫入數據操作均成功。

未檢測到數據不一致/不一致問題。

該設計已成功通過時序驗證了Maxm。 Xilinx Virtex-4 ML-403板(整個系統)的工作時鐘頻率= 110 MHz,僅高速緩存控制器為195 MHz。

為主存儲器推斷出Block RAM。其他所有數組都在LUT上實現。

步驟4:附加文件

以下博客隨此文件附在此處:

.VHD文件。

測試平臺。

有關Cache Controller的文檔。

注意:

通讀該文檔以全面了解此處介紹的緩存控制器的規格。

代碼中的任何更改都依賴于其他模塊。因此,應明智地進行更改。注意我給的所有評論和標題。

如果出于某種原因,無法為主內存推斷出Block RAM,請減小內存的大小,然后更改文件中的地址總線寬度,依此類推。這樣就可以在LUT或分布式RAM上實現相同的內存。這樣可以節省路由時間和資源。或者,轉到特定的FPGA文檔,找到與Block RAM兼容的代碼,并相應地編輯代碼,并使用相同的地址總線寬度規范。

責任編輯:wv

-

控制器

+關注

關注

114文章

17105瀏覽量

184249

發布評論請先 登錄

電機控制器出現的一種偶發故障排查與分析

一種新型直流電機控制器

一種可堆疊和交錯的多相高壓反相降壓-升壓控制器設計

一種簡易緩存控制器的設計

一種簡易緩存控制器的設計

評論