賽靈思(Xilinx)今天宣布推出世界最大的FPGA芯片“Virtex UltraScale+ VU19P”,擁有多達(dá)350億個(gè)晶體管,密度在同類(lèi)產(chǎn)品中也是最大的,相比上代Virtex UltraScale VU440增大了1.6倍,而功耗降低了60%。

雖然具體面積沒(méi)有公布,和日前那個(gè)1.2萬(wàn)億晶體管、46225平方毫米、AI計(jì)算專(zhuān)用的世界最大芯片不在一個(gè)數(shù)量級(jí),但在FPGA的世界里,絕對(duì)是個(gè)超級(jí)龐然大物,從官方圖看已經(jīng)可以蓋住一個(gè)馬克杯的杯口。

相比之下,AMD 64核心的二代霄龍為320億個(gè)晶體管,NVIDIA GV100核心則是211億個(gè)晶體管。

VU19P FPGA采用臺(tái)積電16nm工藝制造(上代為20nm),基于ARM架構(gòu),集成了16個(gè)Cortex-A9 CPU核心、893.8萬(wàn)個(gè)系統(tǒng)邏輯單元、2072個(gè)用戶I/O接口、224Mb(28MB)內(nèi)存,DDR4內(nèi)存帶寬最高1.5Tbps(192GB/s),80個(gè)28G收發(fā)器帶寬最高4.5Tbps(576GB/s),支持PCIe 3.0 x16、PCIe 4.0 x8、CCIX。

該芯片采用Lidless無(wú)頂蓋封裝,優(yōu)化散熱,可讓設(shè)計(jì)者發(fā)揮最極致的性能。

這是一顆“Chip Maker‘s Chip”(芯片廠商的芯片),主要面向最頂級(jí)ASIC、SoC芯片的仿真和原型設(shè)計(jì),以及測(cè)試、測(cè)量、計(jì)算、網(wǎng)絡(luò)、航空、國(guó)防等應(yīng)用領(lǐng)域。

它還支持各種復(fù)雜的新興算法,包括人工智能、機(jī)器學(xué)習(xí)、視頻處理、傳感器融合等。

VU19P FPGA將在2020年秋季批量供貨。

-

賽靈思

+關(guān)注

關(guān)注

33文章

1795瀏覽量

132105 -

晶體管

+關(guān)注

關(guān)注

77文章

9977瀏覽量

140606 -

FPGA芯片

+關(guān)注

關(guān)注

3文章

248瀏覽量

40207

發(fā)布評(píng)論請(qǐng)先 登錄

無(wú)結(jié)場(chǎng)效應(yīng)晶體管詳解

多值電場(chǎng)型電壓選擇晶體管結(jié)構(gòu)

國(guó)產(chǎn)EDA億靈思?接入DeepSeek

賽靈思低溫失效的原因,有沒(méi)有別的方法或者一些見(jiàn)解?

意法半導(dǎo)體推出40V STripFET F8 MOSFET晶體管

晶體管與場(chǎng)效應(yīng)管的區(qū)別 晶體管的封裝類(lèi)型及其特點(diǎn)

達(dá)林頓晶體管概述和作用

NMOS晶體管和PMOS晶體管的區(qū)別

CMOS晶體管和MOSFET晶體管的區(qū)別

晶體管處于放大狀態(tài)的條件是什么

芯片晶體管的深度和寬度有關(guān)系嗎

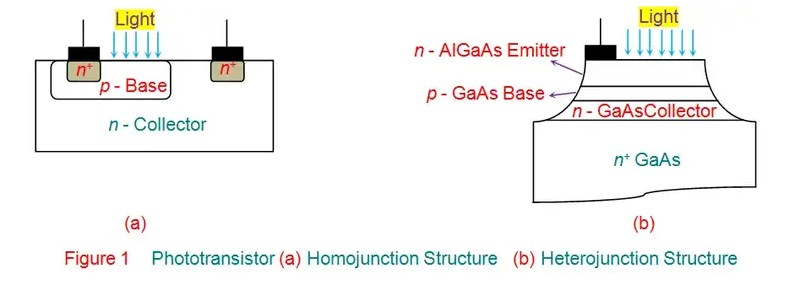

什么是光電晶體管?光電晶體管的工作原理和結(jié)構(gòu)

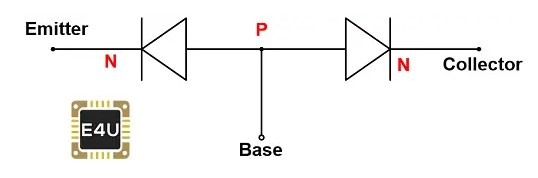

什么是NPN晶體管?NPN晶體管的工作原理和結(jié)構(gòu)

PNP晶體管符號(hào)和結(jié)構(gòu) 晶體管測(cè)試儀電路圖

賽靈思推出世界最大FPGA芯片 擁有多達(dá)350億個(gè)晶體管

賽靈思推出世界最大FPGA芯片 擁有多達(dá)350億個(gè)晶體管

評(píng)論