為了提高其100nm以下SOC的參數產量,東芝公司已聘請Synopsys公司和KLA-Tencor開發緊湊的良率分析和建模系統,用于預測工藝變化對最終設備的影響在LSI生產過程中發生的性能。

該項目的目標是改善東芝IC設計和工藝工程師之間的信息共享,以加速公司的先進工藝開發和產量提升工作。 。東芝計劃在其位于日本大分的300mm SOC制造工廠安裝新的建模系統。

“獲得成功的IC生產必不可少的參數產量,”首席知識和基礎設施官Shigeru Komatsu表示。東芝半導體公司在一份聲明中表示。

“由于SOC產品生命周期通常比其他設備短,因此可以收集更少的過程數據來優化制造過程,這使我們更加迫切需要第一次正確處理。能夠根據實時參數化產量數據對設備性能進行建模,這將使我們能夠在生產過程中快速做出決策,以微調我們的流程并優化我們的產量,并確保我們繼續滿足我們的產品上市時間要求,“他進一步說道。”

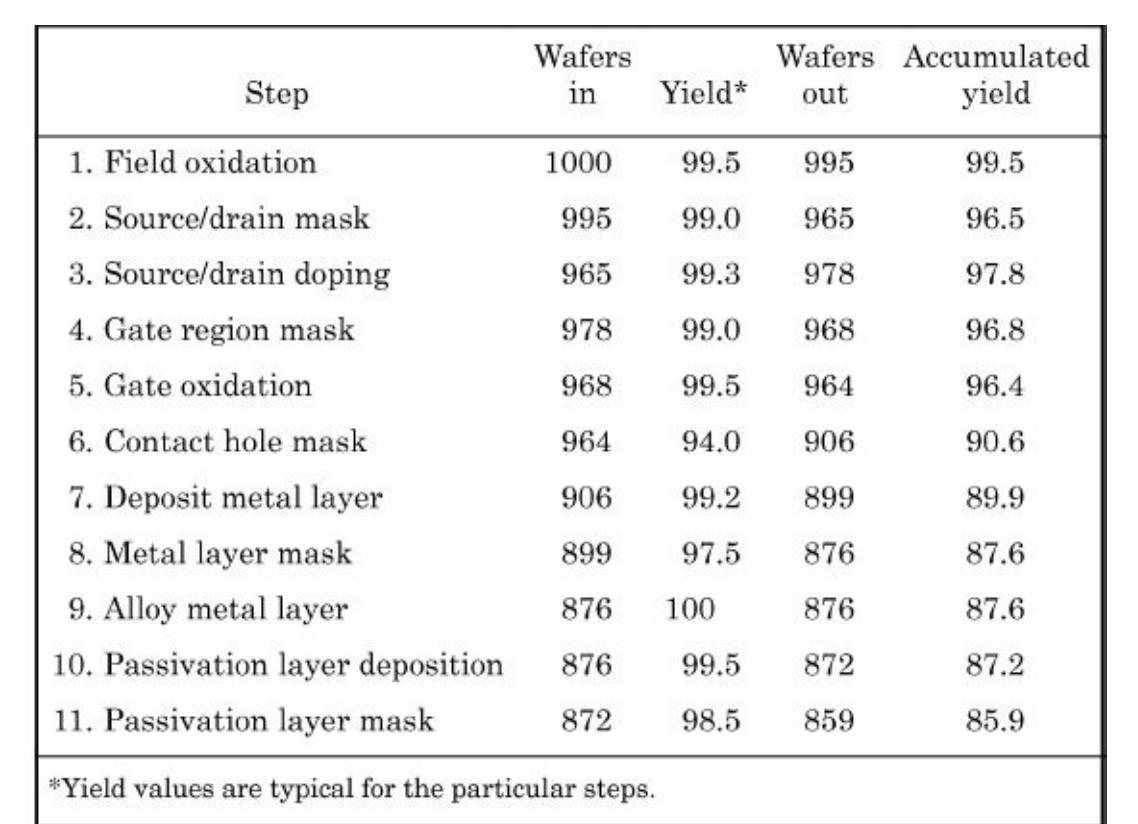

由于設備擴展,工藝容差越來越嚴格,而微小的工藝波動對設備性能的影響越來越大。為了解決這些問題,必須識別和控制這些過程變化的來源,以最小化參數產量損失。對于生產短生產設備的高混合設備的公司而言,錯過流程上的標記可能意味著完全錯過新產品設計的市場窗口。

為解決這些問題,TCAD系統傳統上用于模擬,開發和優化工藝技術,但它們既復雜又耗時。

東芝認為,Synopsys的TCAD模型和KLA的產量分析和報告系統的結合使得流程建模的優勢得以實現。在故障估計,根本原因分析,樣本規劃和設備表征的日增產任務中實現。

建模系統采用KLA的Klarity ACE XP軟件識別參數產量的癥狀這個問題旨在幫助芯片制造商快速解決晶圓廠的產量問題,并加速提高產量。 Synopsys的TCAD多變量非線性模型將用于通過工藝變化和晶體管器件性能特征的鏈接來識別潛在的根本原因。

-

東芝

+關注

關注

6文章

1434瀏覽量

122334 -

TCAD

+關注

關注

2文章

18瀏覽量

10685

發布評論請先 登錄

三星在4nm邏輯芯片上實現40%以上的測試良率

VirtualLab Fusion應用:漸變折射率(GRIN)鏡頭的建模

三星電子1c nm內存開發良率里程碑推遲

三星1c nm DRAM開發良率里程碑延期

盛美臨港研發與制造中心首臺量測設備KLA-Tencor Surfscan SP7入駐

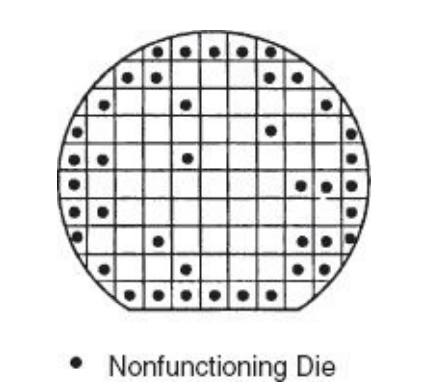

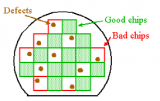

淺談影響晶圓分選良率的因素(2)

半導體工藝之生產力和工藝良率

東芝聘請Synopsys公司和KLA-Tencor開發緊湊的良率分析和建模系統

東芝聘請Synopsys公司和KLA-Tencor開發緊湊的良率分析和建模系統

評論