設(shè)計(jì)人員在前沿片上系統(tǒng)(SoC)設(shè)計(jì)中平衡功耗和性能方面面臨著持續(xù)的困難。更高的電源電壓意味著更快的設(shè)備,但代價(jià)是更高的功耗—在90nm及以下的先進(jìn)納米工藝節(jié)點(diǎn)發(fā)現(xiàn)的高電流泄漏加劇了這個(gè)問題。

直到最近,部署有效的低功耗設(shè)計(jì)策略仍然遠(yuǎn)遠(yuǎn)超出主流設(shè)計(jì)師的范圍。然而,通過知識(shí)產(chǎn)權(quán)(IP)供應(yīng)商,EDA提供商和獨(dú)立代工廠的廣泛合作,新的低功耗設(shè)計(jì)方法增強(qiáng)了熟悉的RTL到GDSII流程,使每個(gè)設(shè)計(jì)人員能夠優(yōu)化其功耗和性能的SoC設(shè)計(jì)。

為了追求市場(chǎng)對(duì)復(fù)雜移動(dòng)應(yīng)用的廣泛興趣,半導(dǎo)體設(shè)計(jì)人員利用日益先進(jìn)的CMOS技術(shù)提供集成電路(IC),為每一代產(chǎn)品設(shè)定尺寸,性能和復(fù)雜性的新里程碑。然而,即使新的工藝技術(shù)使晶體管密度每18個(gè)月翻一番,電池技術(shù)仍然顯著滯后,需要五年多才能實(shí)現(xiàn)相當(dāng)于兩倍的能力。

與此同時(shí),由于與納米技術(shù)相關(guān)的泄漏電流增加,每次工藝生成后,先進(jìn)器件的功耗仍在顯著上升。高級(jí)微處理器的功耗要求通常超過100W,并且隨著設(shè)計(jì)人員轉(zhuǎn)向更先進(jìn)的技術(shù)節(jié)點(diǎn)和更高的時(shí)鐘速率,威脅增長(zhǎng)甚至更高。因此,隨著系統(tǒng)制造商面臨從較小封裝消散更多熱量的新要求,增加的功耗已經(jīng)成為有線和無線系統(tǒng)中系統(tǒng)級(jí)的主要問題。

一旦主要關(guān)注便攜式消費(fèi)產(chǎn)品,在最小化功耗的同時(shí)最大限度地提高性能的需求現(xiàn)已成為包括有線嵌入式產(chǎn)品和高端計(jì)算平臺(tái)在內(nèi)的更廣泛市場(chǎng)領(lǐng)域的關(guān)鍵問題。過去,低功耗設(shè)計(jì)專家已經(jīng)能夠采用專門的架構(gòu)方法或特定的電路設(shè)計(jì)方法,包括時(shí)鐘門控,頻率調(diào)整和特殊工藝選項(xiàng)。然而,即使這些方法在很大程度上仍然是最大的半導(dǎo)體公司的專屬領(lǐng)域,并且通常僅適用于容量最大的設(shè)備。

有效的低功耗設(shè)計(jì)需要一套兼容的專業(yè)功能,可以跨越整個(gè)設(shè)計(jì)鏈。包括知識(shí)產(chǎn)權(quán)(IP)模型,圖書館,設(shè)計(jì)工具和制造能力。反過來,主流低功耗設(shè)計(jì)的有效解決方案需要IP供應(yīng)商,圖書館提供商,EDA工具開發(fā)人員和代工廠的共同努力。

因此,Silicon Design Chain Initiative的成員最近合作創(chuàng)建了一個(gè)跨行業(yè)的電源管理解決方案,并在測(cè)試設(shè)計(jì)上驗(yàn)證了該解決方案。這項(xiàng)工作最終成功實(shí)現(xiàn)了基于ARM1136JF-S核心模塊的芯片的成功實(shí)施和芯片驗(yàn)證,該芯片將在ARM參考板中提供。該器件針對(duì)移動(dòng)和無線應(yīng)用,功耗降低了40%以上。

低功耗設(shè)計(jì)

器件的功耗來自兩個(gè)主要來源:基于器件開關(guān)活動(dòng)的動(dòng)態(tài)功耗,以及由于先進(jìn)的納米工藝技術(shù)降低晶體管閾值電壓而增加的漏電流引起的靜態(tài)功耗。

Silicon Design Chain團(tuán)隊(duì)開始證明其低功耗設(shè)計(jì)系統(tǒng)可以顯著降低ARM1136JF-S測(cè)試設(shè)計(jì)中漏電流引起的動(dòng)態(tài)和靜態(tài)功耗。作為通過系統(tǒng)級(jí)電源管理方法提出潛在節(jié)省的替代方法的補(bǔ)充,這種低功耗設(shè)計(jì)方法采用電路級(jí)方法來實(shí)現(xiàn)這些節(jié)省,而無需高度專業(yè)化的核心功能。

為了驗(yàn)證這種方法的廣泛適用性,該測(cè)試芯片開發(fā)工作采用了典型工藝,TSMC 90nm G硅工藝和ARM Artisan通用物理IP,包括SAGE-X標(biāo)準(zhǔn)單元庫(kù)和內(nèi)存生成器。如下所述,標(biāo)準(zhǔn)單元庫(kù)增加了擴(kuò)展電壓范圍表征,并且單元旨在實(shí)現(xiàn)功率降低設(shè)計(jì)技術(shù)。 Cadence Design Systems使用Encounter數(shù)字IC設(shè)計(jì)平臺(tái)的4.1版開發(fā)了一種低功耗設(shè)計(jì)方法。

動(dòng)態(tài)功耗降低

在這個(gè)項(xiàng)目中,設(shè)計(jì)團(tuán)隊(duì)首先解決了動(dòng)態(tài)功耗問題,可以用以下公式表示:/p》

P = KCV 2 F

其中

K 是切換率(晶體管切換的時(shí)間分?jǐn)?shù)) C 是電路電容,包括互連和晶體管電容

V 是晶體管的電源電壓

F 是工作頻率

如該等式所示,功率與電源電壓的平方成比例。因此,設(shè)計(jì)人員只需降低電壓即可節(jié)省大量的動(dòng)態(tài)功耗。稱為電壓縮放的方法。

另一方面,降低電源電壓會(huì)降低晶體管的開關(guān)速度。由于此設(shè)計(jì)需要達(dá)到350 MHz以滿足ARM開發(fā)合作伙伴的要求,因此團(tuán)隊(duì)必須有選擇地確定設(shè)計(jì)的哪些部分可以使用電壓縮放技術(shù)。

在這種情況下,該團(tuán)隊(duì)創(chuàng)建了一種多電源電壓(MSV)設(shè)計(jì),將設(shè)計(jì)劃分為單獨(dú)的“電壓島”或“電壓域”,其中每個(gè)域在不同的電源電壓下工作,具體取決于其時(shí)序要求(圖1)。在這里,該團(tuán)隊(duì)在一個(gè)域中保留了時(shí)序關(guān)鍵模塊,工作在1.0V的標(biāo)準(zhǔn)90nm電源電壓下。具有較少關(guān)鍵時(shí)序路徑的塊被聚合到第二域中,其中電壓縮小到0.8V—該部分設(shè)計(jì)的動(dòng)態(tài)功耗降低了36%。

圖1—單獨(dú)的電壓域優(yōu)化功率和性能

過去,電壓域方法在物理設(shè)計(jì)中引入了額外的復(fù)雜性,特別是用于連接適當(dāng)?shù)碾娫春碗娫淳W(wǎng)絡(luò)。設(shè)計(jì)人員通常需要手動(dòng)插入稱為電壓電平轉(zhuǎn)換器的特殊轉(zhuǎn)換單元,以在不同電壓域之間轉(zhuǎn)換信號(hào),以及鉗位單元以提供隔離。

實(shí)施這些翻譯單元對(duì)插入,放置和電源連接提出了挑戰(zhàn)。此外,分析不同電壓島上的MSV設(shè)計(jì)也是一個(gè)挑戰(zhàn),因?yàn)槊總€(gè)島的傳統(tǒng)分層建模方法對(duì)于先進(jìn)技術(shù)節(jié)點(diǎn)可能不夠準(zhǔn)確。

ARM1136核心設(shè)計(jì)有3400個(gè)信號(hào),從0.8V到1.0V域,需要3400個(gè)電平移位器。在此流程中,Cadence Encounter設(shè)計(jì)系統(tǒng)自動(dòng)將電平移位器插入到設(shè)計(jì)中,借助提供電壓電平移位器和鉗位單元的ARM Artisan庫(kù)。在此過程中,設(shè)計(jì)系統(tǒng)將這些單元連接到兩個(gè)電源軌并優(yōu)化其放置時(shí)序,信號(hào)完整性對(duì)時(shí)序和電源布線的影響。

此外,Cadence和ARM合作創(chuàng)建了優(yōu)化用于Cadence Encounter NanoRoute路由引擎的電平轉(zhuǎn)換器。電平轉(zhuǎn)換器的設(shè)計(jì)以及它們?cè)贏RM1136JF-S內(nèi)核設(shè)計(jì)中實(shí)現(xiàn)的自動(dòng)化是實(shí)現(xiàn)顯著動(dòng)態(tài)功耗降低的關(guān)鍵因素,同時(shí)仍能滿足激進(jìn)的時(shí)序要求。

為了進(jìn)一步降低動(dòng)態(tài)功耗要求,這個(gè)低功率設(shè)計(jì)方法也使用時(shí)鐘門控技術(shù)。在典型設(shè)計(jì)中,各個(gè)寄存器相對(duì)不頻繁地加載數(shù)據(jù),但時(shí)鐘信號(hào)在每個(gè)時(shí)鐘周期繼續(xù)切換,從而驅(qū)動(dòng)容性負(fù)載。利用這種技術(shù),門控電路關(guān)閉那些不需要加載的寄存器的時(shí)鐘。通常可以實(shí)現(xiàn)動(dòng)態(tài)功耗節(jié)省10%到20%的方法。

對(duì)于這個(gè)測(cè)試芯片,Silicon Design Chain團(tuán)隊(duì)使用Encounter RTL Compiler執(zhí)行自動(dòng)時(shí)鐘門控,使用Artisan庫(kù)中集成的時(shí)鐘門控單元。在這種情況下,自動(dòng)時(shí)鐘門控功能使設(shè)計(jì)團(tuán)隊(duì)能夠在低功耗芯片中選通85%的寄存器。

整體性能的關(guān)鍵還在于低功耗時(shí)鐘樹綜合和高性能時(shí)鐘樹實(shí)現(xiàn)。此外,優(yōu)化兩個(gè)電壓域設(shè)計(jì)的能力減輕了電壓調(diào)節(jié)放大的困難時(shí)序收斂挑戰(zhàn)。

使用這種專用電池組合,自動(dòng)電壓調(diào)節(jié)和時(shí)鐘門控方法,Silicon Design連鎖團(tuán)隊(duì)將芯片的動(dòng)態(tài)功耗降低了37.9%。

靜態(tài)功耗降低

隨著設(shè)計(jì)人員轉(zhuǎn)向更先進(jìn)的技術(shù)節(jié)點(diǎn),他們必須應(yīng)對(duì)急劇增加的漏電流。對(duì)于具有0.7V閾值電壓(Vt)的130nm工藝,每個(gè)晶體管的漏電流約為10-20pA。在0.3V Vt時(shí),每個(gè)晶體管的漏電流可達(dá)10-20 nA,在較小的幾何結(jié)構(gòu)中呈指數(shù)增長(zhǎng)。總體而言,泄漏功率從《5%=“”= =“”power =“”budget =“”at =“”0.25 =“”micron =“”to =“”20-25 =“”percent =“” at =“”130nm =“”and =“”as =“”much =“”as =“”40-50 =“”percent =“”at =“”90nm。=“”》 5》

在這種低功耗方法中,設(shè)計(jì)人員通過使用包含一組匹配邏輯單元的庫(kù)來管理泄漏功耗,這些邏輯單元具有不同的閾值電壓(Vt)和相同的物理占用空間。具有較高Vt的電池比具有較低Vt的對(duì)應(yīng)電池表現(xiàn)出較小的漏電流。

然而,較高的閾值電池也表現(xiàn)出較高的電池延遲,降低了整體性能(圖2)。因此,設(shè)計(jì)工具需要能夠提供滿足最低漏電流性能的網(wǎng)表實(shí)現(xiàn),并同時(shí)優(yōu)化功耗,性能和面積。

圖2—電池延遲隨著電池閾值電壓的降低而增加

對(duì)于這個(gè)測(cè)試芯片,設(shè)計(jì)團(tuán)隊(duì)使用了ARM Artisan庫(kù),它為電池提供不同的電壓閾值。該團(tuán)隊(duì)首先使用Encounter RTL Compiler在綜合期間優(yōu)化設(shè)計(jì),以滿足350MHz的性能目標(biāo),同時(shí)最大限度地降低總漏電流。

在布局和布線可獲得更準(zhǔn)確的寄生信息后,設(shè)計(jì)然后使用SOC Encounter的路由后泄漏優(yōu)化來微調(diào)泄漏功率和性能。具有不同電壓閾值的電池組合以及自動(dòng)化和一致的設(shè)計(jì)能力使Silicon Design Chain設(shè)計(jì)團(tuán)隊(duì)能夠?qū)崿F(xiàn)46.7%的泄漏功率節(jié)省。

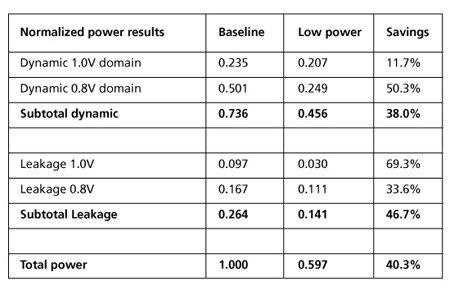

通過降低動(dòng)態(tài)功耗和降低靜態(tài)功耗的總體節(jié)省,可以節(jié)省超過40%的總功耗(表1)。

表1—使用低壓設(shè)計(jì)方法測(cè)試芯片功耗

功耗分析

以及一組合格的IP組件這種低功耗設(shè)計(jì)方法依賴于一個(gè)實(shí)現(xiàn)平臺(tái),可以在各種電壓電平和工作條件下準(zhǔn)確預(yù)測(cè)和優(yōu)化性能。在單一設(shè)計(jì)中使用多個(gè)電源會(huì)引入時(shí)序分析的復(fù)雜性,因?yàn)榫_的延遲計(jì)算需要針對(duì)每個(gè)工作電壓的精確延遲模型。

此外,還必須對(duì)電平移位器和鉗位單元進(jìn)行適當(dāng)建模,以正確計(jì)算聚合延遲。通過他們的共同努力,Cadence和ARM通過使用有效電流源模型(ECSM)表征這些組件來克服這一挑戰(zhàn),以確保跨多個(gè)電壓域的準(zhǔn)確性。

ECSM模擬晶體管吸收的電流,而不是傳統(tǒng)建模方法中的電壓。使用傳統(tǒng)方法,將特定電壓電平的單元延遲精確建模到Spice的幾個(gè)百分點(diǎn)內(nèi),需要為該電壓電平創(chuàng)建特征化的時(shí)序視圖 - 這是一個(gè)廣泛而昂貴的過程。例如,要在三個(gè)不同的工藝/溫度拐角處使用六個(gè)不同的電壓電平,需要18個(gè)獨(dú)立的時(shí)序庫(kù)特征。

此外,大多數(shù)延遲計(jì)算器和行業(yè)標(biāo)準(zhǔn)時(shí)序分析儀僅支持單個(gè)標(biāo)稱電壓電平的精確延遲計(jì)算。使用標(biāo)稱以外的電壓會(huì)引起過多的誤差,因?yàn)榫€性降額通常超過Spice的20%,特別是對(duì)于速度較慢的低功率電池。

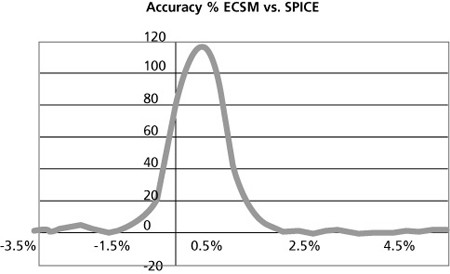

相比之下,MSV設(shè)計(jì)中的不同工作電壓可以覆蓋ECSM型號(hào)的特點(diǎn)是電壓范圍內(nèi)只有三個(gè)點(diǎn)。硅設(shè)計(jì)鏈芯片中使用的基于ECSM的標(biāo)準(zhǔn)單元模型實(shí)現(xiàn)了延遲預(yù)測(cè),平均與Spice仿真的2%相關(guān)(圖3)。對(duì)于這個(gè)測(cè)試芯片,Artisan通過提供lib_ecsm庫(kù)視圖來表征其90-nm庫(kù)以支持ECSM延遲預(yù)測(cè)。

圖3 - ECSM在Spice模擬的2%范圍內(nèi)達(dá)到準(zhǔn)確度

設(shè)計(jì)簽收

與任何設(shè)計(jì)一樣,準(zhǔn)確性是簽核過程中的主要問題。隨著多個(gè)電壓域的復(fù)雜性增加,這種類型的低功耗設(shè)計(jì)可能給簽核分析帶來額外的困難。對(duì)于此測(cè)試芯片,Silicon Design Chain使用VoltageStorm和CeltIC NDC來提供所需的精度。

VoltageStorm分析了1.0V和0.8V電網(wǎng)的IR壓降,證實(shí)設(shè)計(jì)中的每個(gè)晶體管都在必要的電源電壓下工作。反過來,這些電壓被用作CeltIC NDC(SignalStorm)中基于ECSM的延遲計(jì)算器的輸入,在兩個(gè)電源電壓域上提供接近Spice精確的時(shí)序。在這種類型的設(shè)計(jì)中,這種精度水平尤其重要,因?yàn)樵贛SV設(shè)計(jì)中使用的較低電源電壓下,IR時(shí)序?qū)r(shí)序的影響更為明顯。

結(jié)論

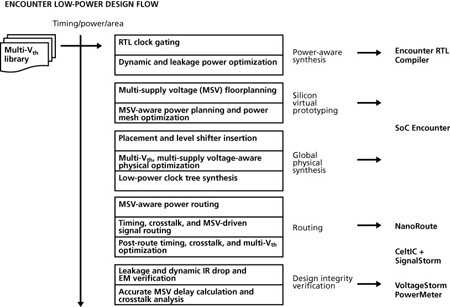

隨著半導(dǎo)體公司尋求利用新興市場(chǎng)機(jī)遇,解決新興納米設(shè)計(jì)挑戰(zhàn)的需求變得至關(guān)重要。通過其協(xié)作努力,硅設(shè)計(jì)鏈成員公司正在解決這些棘手的跨行業(yè)問題。通過創(chuàng)建全面的低功耗設(shè)計(jì)流程(圖4),成員公司為主流SoC設(shè)計(jì)人員提供了曾經(jīng)只有最大的半導(dǎo)體公司才能使用的功能。

圖4—低功耗設(shè)計(jì)流程

Silicon Design Chain工程團(tuán)隊(duì)在基于ARM1136JF-S處理器的高性能器件中驗(yàn)證了這種硅片中的低功耗設(shè)計(jì)方法。該測(cè)試設(shè)備采用TSMC的90G工藝制造,采用了低功耗設(shè)計(jì)系統(tǒng),包括ARM精細(xì)調(diào)諧的物理IP產(chǎn)品和建模方法,以及Cadence的Encounter低功耗設(shè)計(jì)流程。這種低功耗解決方案將共同降低與主流電子產(chǎn)品開發(fā)人員轉(zhuǎn)向高級(jí)工藝節(jié)點(diǎn)相關(guān)的風(fēng)險(xiǎn)。

Robert Aitken是ARM物理IP產(chǎn)品技術(shù)的高級(jí)架構(gòu)師,負(fù)責(zé)內(nèi)存架構(gòu),可制造性設(shè)計(jì)和可測(cè)試性解決方案設(shè)計(jì)。

George Kuo是Cadence設(shè)計(jì)鏈計(jì)劃的技術(shù)總監(jiān),負(fù)責(zé)與戰(zhàn)略合作伙伴一起領(lǐng)導(dǎo)技術(shù)項(xiàng)目。在加入Cadence之前,他曾在Hughes Aircraft Company和Synopsys擔(dān)任高性能信號(hào)處理器ASIC設(shè)計(jì)和流程開發(fā)的高級(jí)職位。

Edward Wan是臺(tái)積電北美設(shè)計(jì)服務(wù)營(yíng)銷高級(jí)總監(jiān)。在加入臺(tái)積電之前,萬(wàn)先生是加利福尼亞州米爾皮塔斯領(lǐng)先的芯片設(shè)計(jì)服務(wù)公司Spike Technologies的首席執(zhí)行官。

-

soc

+關(guān)注

關(guān)注

38文章

4386瀏覽量

222682 -

低功耗設(shè)計(jì)

+關(guān)注

關(guān)注

0文章

83瀏覽量

16443

發(fā)布評(píng)論請(qǐng)先 登錄

器件的低功耗設(shè)計(jì)可實(shí)現(xiàn)多元化IC

器件的低功耗設(shè)計(jì)可實(shí)現(xiàn)多元化IC

評(píng)論