光纖通道或異步傳輸模式(ATM)數據速率等新技術,如實時視頻處理,醫療成像和電信,正在對當今CISCμP的功耗造成負擔。 Windows NT的多用戶多任務應用程序的預期增長將進一步加劇這一問題。隨著處理需求的增加,似乎只有提供RISC性能數據的μP才能集中力量來滿足這些任務。在過去幾年中,已經有許多能夠執行這些新技術任務的μP。

理解這些高性能μP中的所有特殊功能是一項艱巨的任務,然而。這些芯片提供了創新,以克服前幾代產品中的缺點,因此包含x486 CISC式μP或更早版本中未提供的許多功能。超標量和超流水線架構是當今的口號。這些架構將μP性能方程擴展到極限。 μP執行任務的經典性能等式由下式給出:

執行時間=(無指令)×(循環/指令的平均數)×(循環時間)。

由于周期時間達到物理約束并且RISCμP平均有一個周期來執行指令,因此克服執行時間障礙的一種方法是并行執行多個指令。超標量μP具有指令調度器,其將未執行的指令饋送到可訪問通用寄存器文件和片上高速緩存和總線的片上執行單元池。調度程序必須確定正在使用哪些寄存器,并選擇非沖突指令以在每個時鐘周期進行調度。從理論上講,調度指令的數量沒有限制,但是當前的技術水平是三個或更少。

Superpipeline架構通過在一個指令中執行一個以上的指令來實現性能提升時鐘周期。任何指令的整體執行都是一個順序過程,您可以分解為幾個步驟。今天所有重型打擊者都使用與步驟重疊的流水線架構,例如預取指令和數據的時間,指令解碼時間,執行時間以及數據的寫回時間。通過將CPU時鐘周期分成子循環并在每個子循環中發出新指令來實現每個時鐘周期執行多個指令步驟。雖然一些超標量體系結構也允許每個時鐘周期執行多個指令步驟,但這些指令步驟通常不會像超流水線架構那樣交錯。

很多doodads

今天的所有高性能產品至少具有64位外部數據總線,片上浮點單元(FPU),一個或多個ALU,片上高速緩存,存儲器管理單元(MMU)以及轉換旁視緩沖區(TLB)將虛擬內存地址轉換為物理內存地址。這些μP還具有存儲緩沖區的優勢,這使得流水線可以無延遲地繼續執行,并最大限度地減少與使用外部緩存的數據填充片上緩存相關的延遲。硬件的設計考慮了軟件程序員的風俗習慣。檢測指令流中的條件或無條件分支語句的分支預測單元試圖預測哪條指令和數據應放在管道中。準確的預測不會產生處理延遲,而不準確的預測可能會導致管道刷新。

此外,這些設備提供多處理功能,可實現總線仲裁,緩存一致性協議和總線偵聽。這里提到的所有μP都運行Microsoft的Windows NT和其他流行的操作系統,例如Unix。為了與x86兼容計算機的流行軟件的廣泛基礎保持二進制兼容,大多數μP依靠仿真技術的突破,讓RISC計算機運行x86軟件,其性能水平可與66-MHz Intel486DX2μP相媲美。

MIPS技術R4400是超流水線架構的一個很好的例子。 R4400于1992年10月推出,接受外部75 MHz時鐘,并在內部將時鐘乘以2,以驅動150 MHz 8級流水線,每個CPU周期執行兩條指令。 R4400的三個版本包括具有片上高速緩存的版本,這些高速緩存不需要外部二級高速緩存(R4400PC和R4400-SC)用于成本敏感的應用,而高端版本(R4400MC)用于包含on的多處理系統-chip二級緩存控制器。片上指令和數據高速緩存各為16 KB,外部二級高速緩存有128位數據總線。

R4400是真正的64位架構,提供64位FPU,ALU,整數寄存器和系統總線的位數據路徑。整數單元可以執行背靠背ALU或加載/存儲操作,而不受調度程序的任何問題限制。該芯片可執行32位和64位應用程序。虛擬地址空間可以是32位或64位寬,48入口片上TLB轉換為36位物理地址空間。芯片的字節排序數據格式可以配置為大端或小端。

您可以使用第三方芯片組將芯片的64位多路復用地址和數據主機總線連接到標準系統總線 - 派對供應商。 NEC和東芝制造的三個ARC-set ASIC將R4400主機總線轉換為i386兼容系統總線,以便與標準PC外設芯片進行通信。 ASIC還提供到視頻內存的64位數據路徑和到主內存的128位數據路徑。

64位架構可擴展

Alpha系列的第一個成員Digital Equipment Corp的21064μP是另一個真正的64位架構。該架構具有64位虛擬地址空間,片內寄存器,整數和浮點數均為64位寬。 32項TLB將64位虛擬地址轉換為34位物理地址,單獨的8 KB片上指令和數據高速緩存為7級整數流水線和10級浮點流水線提供數據。 Alpha的超標量和超流水線架構的第一個實現可以在每個時鐘周期向四個獨立的執行單元發出兩條指令。數字聲稱Alpha架構可擴展,每個周期可實現10條指令。

21064接受單個ECL兼容時鐘輸入,內部除以2,運行速度為150或200 MHz。該芯片采用3.3V電源供電,但所有I/O端口均兼容TTL。雖然Alpha內部運行的CPU時鐘速率是輸入時鐘頻率的一半,但芯片進一步劃分CPU時鐘,以便在18.75和75 MHz之間的可選總線速度下與其外部128位主機總線通信。四個或六個ASIC芯片組充當Alpha主機總線和外圍組件互連(PCI)總線之間的橋梁。芯片組還為8到256 MB的系統DRAM和系統邏輯提供錯誤檢查和糾正(ECC),以控制外部輔助50-MHz緩存系統,Digital調用Bcache。

最新版本Alpha(21066)于1993年9月推出,它將ASIC芯片組集成到μP芯片上。因此,$ 385(5000)21066提供了與外部Bcache,DRAM內存和PCI總線的直接連接,無需外部系統邏輯。為了節省引腳數,21066將其存儲器總線限制為64位。該芯片還通過集成片上PPL乘法器簡化了設計,該乘法器可以將輸入時鐘乘以2和9之間,以生成其內部166 MHz時鐘。此外,Alpha架構實現了一層軟件,它位于用戶的應用軟件和系統硬件之間。機器碼編寫的軟件稱為PALcode(特權架構庫代碼),它實現了低級硬件支持功能,這些功能通常由操作系統(如VAX)中的微碼提供。通過提供TLB未完成例程,上下文切換,中斷確認和異常調度等功能,PALcode使Alpha的架構獨立于操作系統。

越來越多的SPARCμP是由于SPARC International的開放標準政策。該聯盟的200多名成員正在為SPARC International開放式規范設計μP或計算機系統。高性能版本8規范的一個μP實現是SuperSPARC,它由Sun Microsystems Computer Corp和Texas Instruments共同開發。 TI制造該器件。 32位超標量μP具有指令獲取和發出邏輯,其為三個獨立的ALU,FPU和單獨的加載/存儲單元預取和調度指令。每個時鐘周期可以發出多達三條指令。檢查三個指令的數據依賴性和資源沖突,以確定執行的執行次數。指令始終按順序發出。

40,60或60 MHz SuperSPARC可與兩個主機總線接口,2級Mbus或Vbus一起運行。您可以通過驅動其中一個μP引腳激活來選擇主機總線。 40-MHz leve-2l Mbus是64位數據和36位地址多路復用同步總線。 SuperSPARC可以以比Mbus更高的時鐘速率運行,與Mbus時序要求異步運行。 Mbus支持少量多處理器的MESI協議,并使用兼容TTL的電壓電平與標準CMOS器件兼容。

為了實現更高性能,Vbus支持TI外部高速緩存控制器,并且2 MB外部緩存SRAM。高速緩存控制器與主機側的高速緩存SRAM和Vbus以及系統側的Mbus或Xbus連接。 Xbus最多支持四個外部總線觀察器,可與多個系統總線一起使用以增加可用帶寬。 Cray Research在其最近發布的S-MP超級服務器系統上修改了Xbus以支持多達64個SPARCμP。

SuperSPARC架構使用Wabi(Windows應用程序二進制接口)在Unix平臺上運行Windows 3.1軟件的PC應用程序。 Wabi由Sun Microsystems子公司Sun Select開發。模擬器將x86指令轉換為相關的RISC指令,執行它們,并向Windows應用程序返回適當的值。

賽普拉斯Ross Technology子公司的HyperSPARC是版本8開放標準的另一個實現性能SPARCμPs。 HyperSPARC是使用磁帶自動綁定(TAB)在Mbus模塊上實現的芯片組。每個模塊包含一個或兩個CY7C620 CPU:CY7C625高速緩存控制器,MMU和標簽單元;和兩個或四個CY7C627緩存數據單元,分別用于128或256千字節的二級緩存。 55或66 MHz超標量CPU具有四個執行單元,每個時鐘周期讀取兩條指令,如果沒有數據依賴性,可以單獨執行。與SuperSPARC一樣,HyperSPARC架構與現有SPARC軟件100%二進制兼容,但提供比上一代SPARCμP更高的性能。

PowerPC 601是RISCμP系列中的第一個Apple,IBM和摩托羅拉計劃開發。第一個實現是32位超標量μP,每個時鐘周期可以發出多達三條指令,三條獨立執行流水線中的每一條都有一條指令。 8階段指令隊列預取來自32k字節統一高速緩存的指令,并且可以向執行單元發出無序指令以提高性能。指令隊列的低四個階段試圖始終保持管道填充,而隊列的上半部分就像一個指令緩沖區。

當指令隊列中的較低階段遇到分支指令時,分支處理單元(BPU)將指令拉出隊列以解決它。單元上方的指令在隊列中向下移動以取代被移除的分支 - 一種稱為分支折疊的技術。分支折疊可以將流量控制開銷減少到零,因為執行過程就好像分支從不存在一樣。 BPU可以在一個時鐘周期內解碼和執行分支指令。如果采用分支,則BPU從緩存中的新目標地址請求指令,該指令在氣泡發生之前填充指令隊列。

PowerPC 601實現靜態分支預測,其中編譯器給出提示關于是否應該采取分支。指令操作碼中的單個位提供提示。編譯器總是預測后向分支,例如在程序循環中使用的分支,而不是前向分支。當分支指令遇到數據依賴性時,BPU等待分支條件代碼變得可用。同時,μP不是停止指令隊列,而是獲取預期分支的指令。如果預測正確,則程序流程繼續。否則必須刷新指令隊列。

PowerPC 601使用基于Motorola的MC88110RISCμP同步總線的外部主機總線 - 盡管它不兼容插件。該總線具有64位數據和32位地址路徑,并具有用于多處理功能的總線仲裁和高速緩存一致性功能。目前,如果要將PowerPC 601設計到系統中,則必須將其與μP的MC88110總線連接。摩托羅拉正在與第三方芯片組供應商談判開發芯片組,這些芯片組將充當MC88110主機總線和PCI總線之間的橋梁。

從技術上講,PentiumμP不是RISC處理器,因為它實現了現在標準的復雜x86指令集。然而,32位PentiumμP在66 MHz工作時達到了基準數據,遠高于第一代CISCμP。原因是Pentium借用了RISC架構中使用的許多思想。超標量Pentium包含三個管道執行單元,兩個整數和一個浮點。 μP可以在一個時鐘周期內發出兩個整數指令或一個浮點指令。

Pentium的8 KB數據和指令緩存是用于共享存儲器多處理器系統的回寫緩存。數據高速緩存支持MESI(修改的,獨占的,共享的,無效的)協議,該協議通過總線監聽來維護高速緩存一致性。此外,Pentium使用動態分支預測方案來猜測分支語句將采用哪種方式。分支目標緩沖區會記住每個分支的目標地址和每個分支的方向,并根據分支的歷史記錄動態預測未來的分支。動態預測方案比PowerPC 601中的靜態預測方案需要更少的編譯器支持。

英特爾提供82430 PCI芯片組來開發用于PentiumμP的臺式PC。芯片組由82434LX高速緩存和主存儲器控制器以及82433LX本地總線加速器組成,該加速器管理主機總線和PCI總線之間的協議。 PCI總線允許多個總線主控器與Pentium CPU傳輸同時傳輸數據。該芯片組支持多達512千字節的外部二級緩存SRAM。然而,66 MHz系統中組件之間的時鐘偏差要求非常嚴格。

所有這些高速時鐘和數據線都在抖動,獲得高性能的μP以便在印刷電路板上有效運行有時可能是一件苦差事。 MicroModule Systems提供了一種在多芯片模塊(MCM)上放置高速設計關鍵區域的模具的方法。該公司擁有自己的潔凈室設施,致力于為MCM上的多個裸片制造受控阻抗布局。 MCM近年來名聲不好,因為低產量已經產生了過高成本的設備。然而,MicroModule Systems董事長Bill Robinette Jr認為,經過全面測試的“已知良好”芯片和用于Mentor Graphics開發的MCM的CAD程序可以將開發受控阻抗MCM的增值成本保持在最低水平。 。

-

CISC

+關注

關注

1文章

31瀏覽量

19823 -

PCB打樣

+關注

關注

17文章

2977瀏覽量

22557 -

華強PCB

+關注

關注

8文章

1831瀏覽量

28593 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43911

發布評論請先 登錄

單片機的一些特殊功能寄存器定義

單片機的一些特殊功能寄存器

電源管理特殊功能寄存器PCON介紹

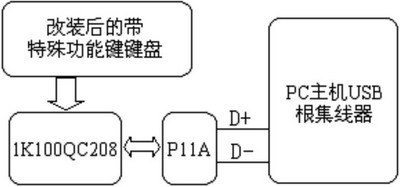

USB鍵盤特殊功能鍵的實現

第二章(1) 初識P0,P1并口 數據類型,常量定義方法,特殊功能寄存器定義

高性能μP中的特殊功能介紹

高性能μP中的特殊功能介紹

評論