基于VHDL的數(shù)字時(shí)鐘設(shè)計(jì)

推薦 + 挑錯(cuò) + 收藏(0) + 用戶評(píng)論(0)

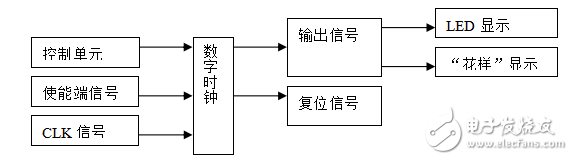

1)時(shí)鐘計(jì)數(shù):完成時(shí)、分、秒的正確計(jì)時(shí)并且顯示所計(jì)的數(shù)字;對(duì)秒、分

——60進(jìn)制計(jì)數(shù),即從0到59循環(huán)計(jì)數(shù),時(shí)鐘——24進(jìn)制計(jì)數(shù),即從0到23循環(huán)計(jì)數(shù),并且在數(shù)碼管上顯示數(shù)值。

2)時(shí)間設(shè)置:手動(dòng)調(diào)節(jié)分鐘、小時(shí),可以對(duì)所設(shè)計(jì)的時(shí)鐘任意調(diào)時(shí)間,這樣使數(shù)字鐘真正具有使用功能。我們可以通過實(shí)驗(yàn)板上的鍵7和鍵4進(jìn)行任意的調(diào)整,因?yàn)槲覀冇玫臅r(shí)鐘信號(hào)均是1HZ的,所以每LED燈變化一次就來一個(gè)脈沖,即計(jì)數(shù)一次。

3)清零功能:reset為復(fù)位鍵,低電平時(shí)實(shí)現(xiàn)清零功能,高電平時(shí)正常計(jì)數(shù)。可以根據(jù)我們自己任意時(shí)間的復(fù)位。

4)蜂鳴器在整點(diǎn)時(shí)有報(bào)時(shí)信號(hào)產(chǎn)生,蜂鳴器報(bào)警。產(chǎn)生“滴答。滴答”的報(bào)警聲音。

5)LED燈在時(shí)鐘顯示時(shí)有花樣顯示信號(hào)產(chǎn)生。即根據(jù)進(jìn)位情況,LED不停的閃爍,從而產(chǎn)生“花樣”信號(hào)。

非常好我支持^.^

(0) 0%

不好我反對(duì)

(0) 0%

下載地址

基于VHDL的數(shù)字時(shí)鐘設(shè)計(jì)下載

相關(guān)電子資料下載

- fpga的開發(fā)流程有哪些步驟?fpga和嵌入式系統(tǒng)的區(qū)別在哪里? 146

- 用VHDL語言創(chuàng)建一個(gè)8位算術(shù)邏輯單元(ALU) 50

- FPGA協(xié)處理的優(yōu)勢(shì)有哪些?如何去使用FPGA協(xié)處理? 887

- 基于VHDL語言用FPGA制作SPI-ASI接口轉(zhuǎn)換器 677

- FPGA開發(fā)語言的選擇 62

- 什么是DFX技術(shù)?DFX設(shè)計(jì)一定要執(zhí)行設(shè)計(jì)規(guī)則檢查嗎? 884

- 模型機(jī)控制信號(hào)產(chǎn)生邏輯VHDL 92

- eda技術(shù)與vhdl基礎(chǔ) eda的主要功能優(yōu)點(diǎn) 268

- 請(qǐng)問如何將C語言算法移植到FPGA上? 321

- 強(qiáng)大的JTAG邊界掃描2-BSDL文件 179