外接低噪聲放大器設計 - UHF頻段無線收發信機前端設計

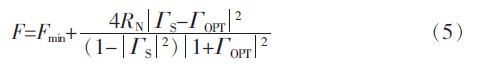

由前面的分析可知,要減小系統的噪聲就需要在濾波器前加入一級高增益、低噪聲的放大器。在對器件的選擇上,選擇了安華高的HEMT器件ATF-54143,它具有超低的噪聲系數和較高的線性增益。

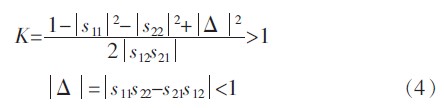

設計放大器的第一步就是使器件在整個工作帶寬內及鄰近區域內穩定。將放大器等效為二端口網絡,則二端口穩定的必要條件可表示為:

?

只要滿足上述條件,LNA就無條件穩定。一般LNA不會在全頻段內都穩定,因此需要添加外部電路使其穩定,最常用的穩定措施是加入負反饋。本設計中就是通過在源級加入電感反饋使器件穩定,偏置點的選擇采用了手冊推薦的Vds=3 V,Id=60 mA。LNA設計的要點是找到最佳噪聲點并進行匹配。對于單級LNA而言,等效為二端口網絡其噪聲系數可表達為:

?

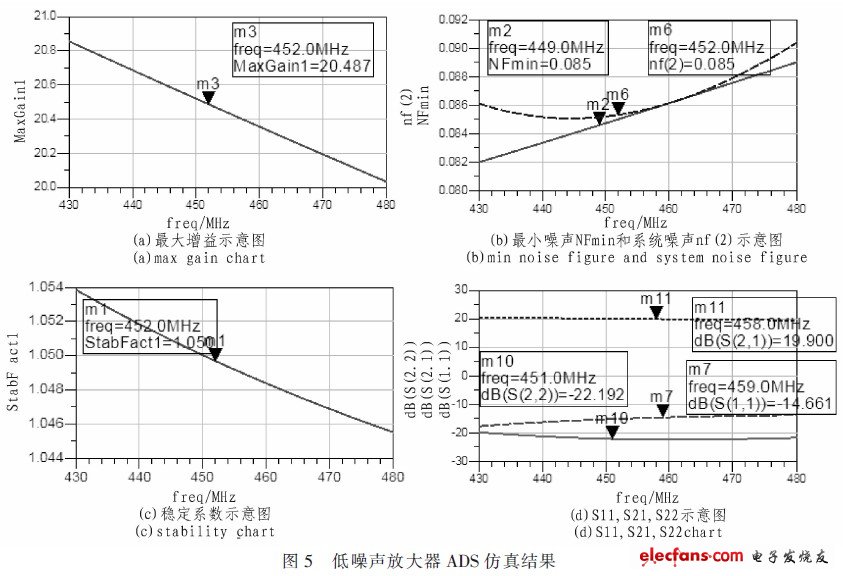

Fmin為LNA管的最小噪聲系數,Гs為源反射系數,Гopt和RN分別為最佳噪聲反射系數和等效噪聲電阻。在LNA設計時就是要將輸入端匹配至最佳噪聲點,但有時為了兼顧駐波,增益指標也要進行適當的平衡選擇,在寬帶設計中為了保證增益平坦度,往往還要加入負反饋等。實際設計在ADS中仿真如圖4所示,輸入和輸出中都是用π型匹配,仿真結果如圖5所示,增益在20 dB,噪聲<0.1 dB,實際調試中由于匹配元件Q值,以及電路布線等原因都對噪聲產生巨大影響,調試結果在全頻段內噪聲<1.1 dB。

?

?

2.3 鎖相環及混頻解調部分設計

TH7122內部集成一個整數分頻PLL電路,PLL電路是通過一個負反饋回路進行頻率合成,其輸出頻率fVCO是鑒相頻率fRO的整數倍N,fR由參考晶振頻率R分頻所得。鑒相器將fVCO的N分頻信號fN與fR的相位差值轉變為電信號經過環路濾波控制VCO產生想要的頻率。本設計中參考頻率采用10 MHz無源晶振,根據不同接收或發射頻率向N和R寄存器中寫入分頻值。

?

混頻部分根據芯片設定為下變頻,中頻設為10.7 MHz。為達到鏡像抑制40 dB和較好的信道選擇性,設計了一個四頻段PIN開關濾波器。該濾波器采用四級電容耦合切比雪夫方式實現,由PIN開關控制接入四級諧振單元的電容變換濾波器的通頻帶。每個通頻帶寬為10 MHz,帶外20 M抑制40 dB。4個通頻帶中心分別為440 MHz,450 MHz,460MHz,470MHz。中頻濾波器采用村田公司的CDSCB10M7GA,中心頻率10.7 MHz。信號經過中頻濾波器后進入芯片內部的中頻放大部分,經放大后進入鑒頻單元,鑒頻器同樣選用村田公司的SFECF10M7HAOO,經過鑒頻輸出后,將中頻信號轉換為音頻信號,經過Salley-Key濾波后經音頻放大器放大輸出。

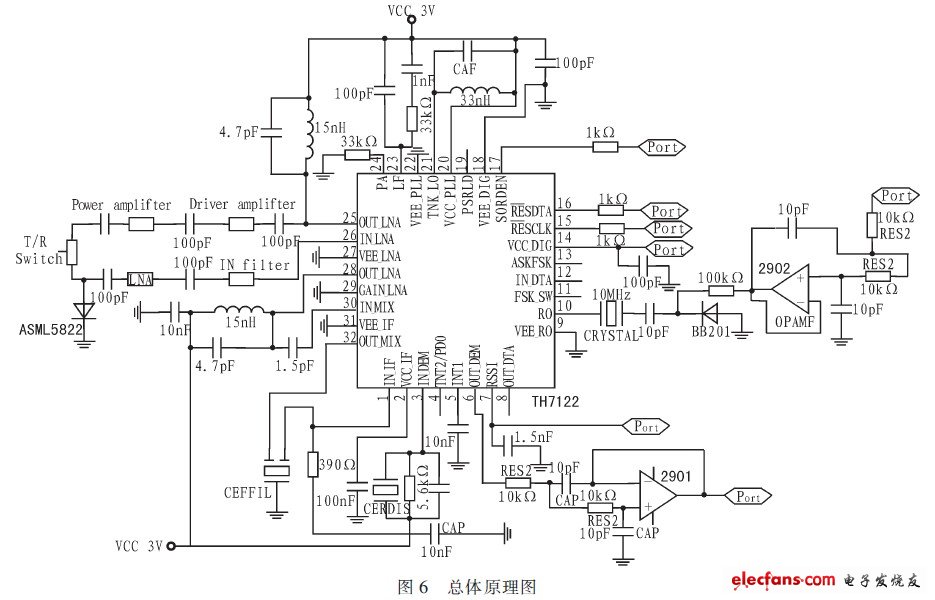

發射信號的調制由于無論是語音信號還是MSK調制信號最終都是在音頻范圍內的模擬信號,經過實驗采用了簡單易行的模擬信號經過Sal-ley-Key濾波后去調制PLL電路使載波產生偏移,實現調制。因為無源晶振需要外接1個負載電容接地工作,電容的變化會引起晶振工作頻率的偏移,故將晶振負載電容分為固定電容C和變容二極管Dc串聯兩部分,模擬信號接入C與Dc之間,讓模擬電壓調制信號控制變容二極管電容,拉動晶振工作頻率偏移,從而引起fR變化,最終間接調制fVCO,實現調制功能。VCO輸出經過芯片內部放大器輸出5~10 mW。為達到發射功率為5 W,設計中采取由BFG540W匹配設計的驅動放大器和π型衰減結合將功率驅動到50mW,再經過功率放大器RA07M4047將功率放大為5 W以上,經過低通諧波濾波器濾除諧波后發射,圖6是總體的原理圖。

?

3 結束語

由于該系統主要應用于音頻及低速率MSK通信,對交調和動態范圍等指標要求不高。在設計中基于TH7122內部已集成整個收發系統的基礎上,為了擴展通信帶寬,提高靈敏度和鏡像抑制以及輸出功率的要求,增加了外接LNA,鏡像抑制濾波器和功率提升電路。TH7122芯片的資料可直接參考手冊,在繪制整個系統的PCB時,參考手冊的電路連接和PCB板標準,根據基板厚度和材質計算好50 Ω微帶線的寬度,走線盡量避免回型和相互的串擾,加大接地面和上下地的穿孔連接等射頻PCB板的基本原則。經過仿真和調試。基本滿足了系統需求。

- 第 1 頁:UHF頻段無線收發信機前端設計

- 第 2 頁:外接低噪聲放大器設計

本文導航

非常好我支持^.^

(1) 100%

不好我反對

(0) 0%

相關閱讀:

- [EDA/IC設計] 數字芯片設計流程 2023-09-19

- [電子說] 芯片的前端設計包括哪些 2023-09-14

- [電子說] 思爾芯亮相第十屆中國-中亞合作論壇暨中國與中亞國家成果展,全方位EDA解決 2023-09-12

- [電子說] 國芯思辰|2.4GHz頻段GC1103可用于RFID標簽芯片模擬射頻前端設計 2023-06-12

- [電子說] 芯片設計包含哪些內容 芯片設計流程詳解 2023-07-19

- [電子說] 高速比較器應用于ToF激光雷達前端設計——HA1007應用指南1 2023-07-01

- [電子說] ASIC數字設計:前端設計、驗證、后端實現 2023-07-02

- [EDA/IC設計] 數字IC前端設計流程及工具 2023-06-25

( 發表人:簡單幸福 )