采樣保持電路圖設計(四)

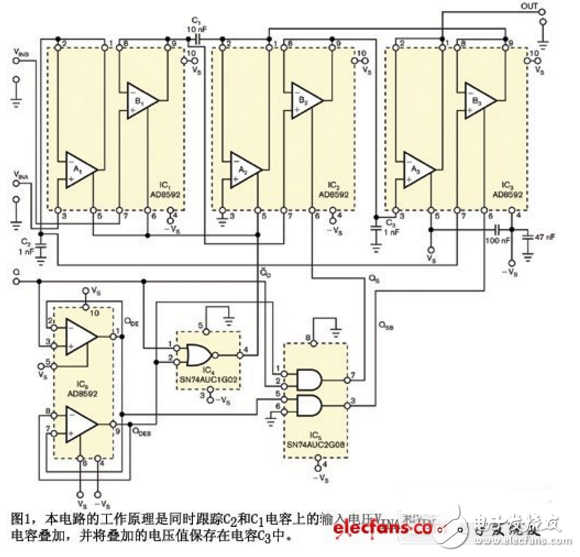

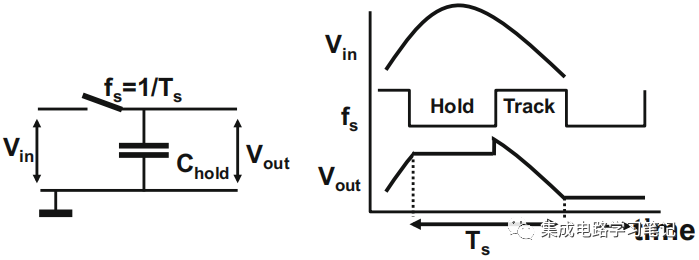

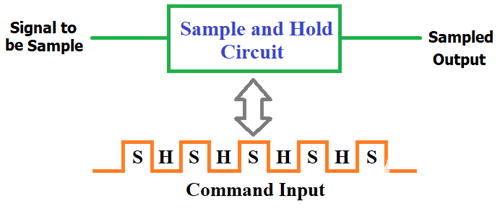

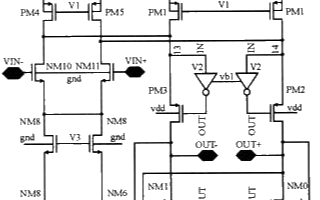

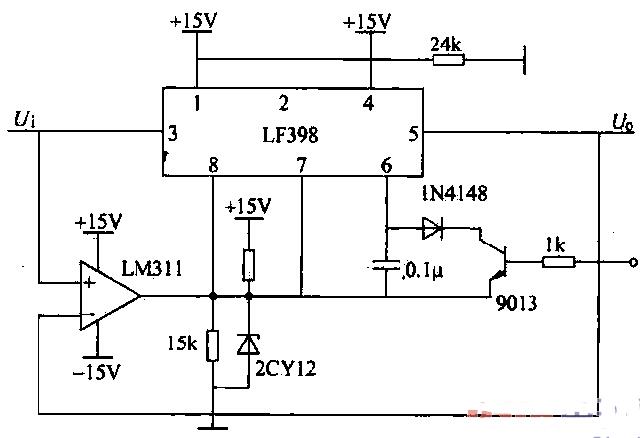

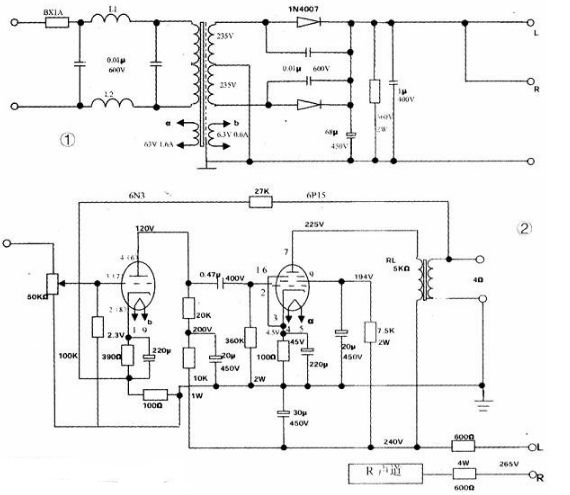

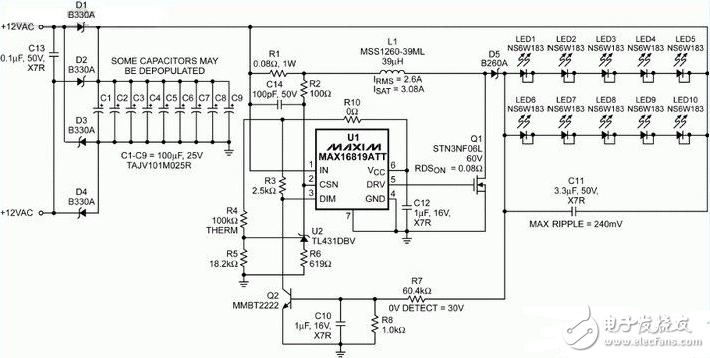

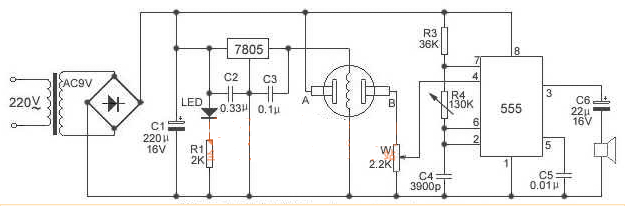

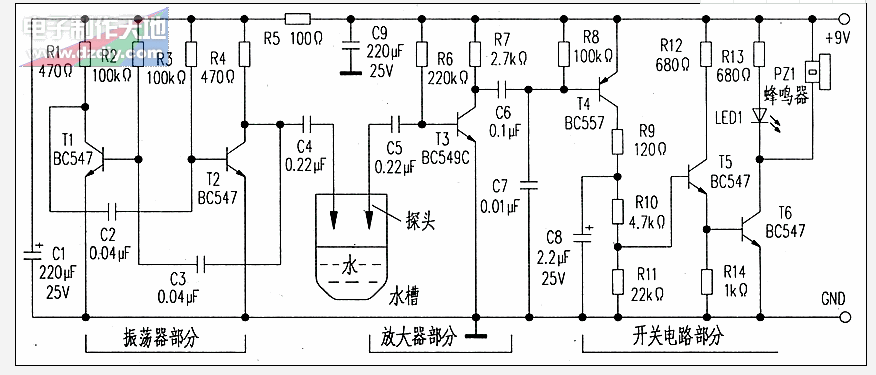

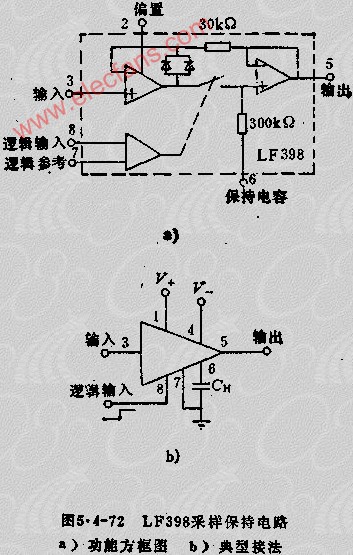

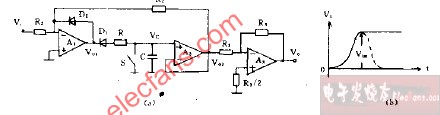

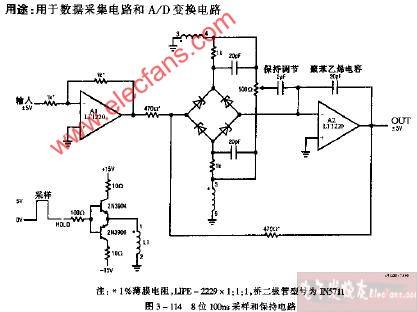

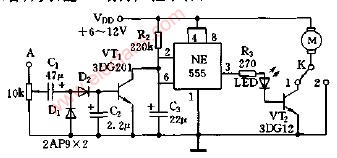

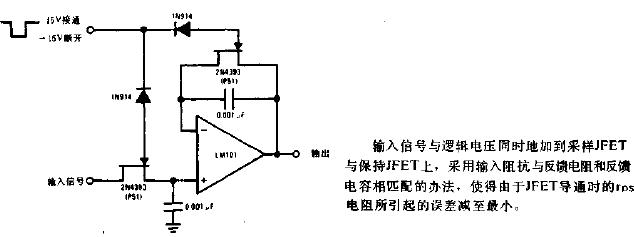

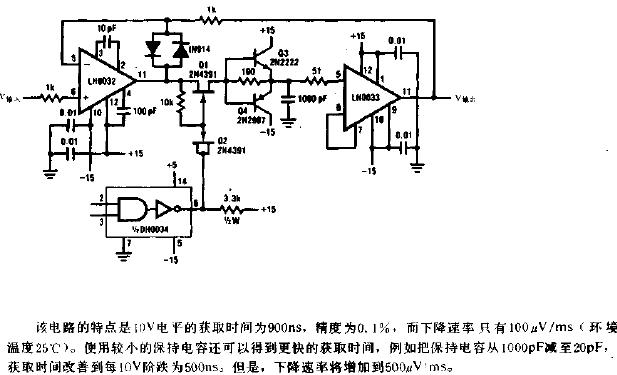

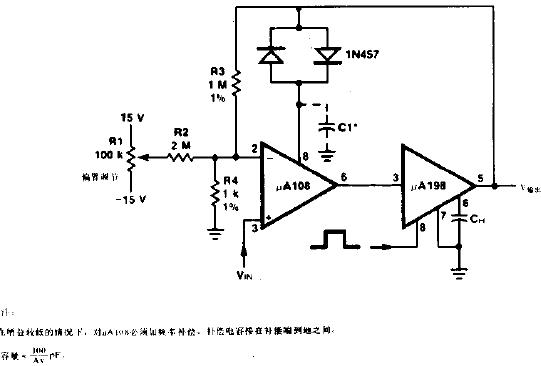

將一個經典的模擬累加器與一個采樣保持放大器級聯對一組模擬電壓的采樣進行保持。經典的模擬累加器是一個運放加上至少三只精密電阻。這些電阻的值應盡可能低,以避免影響累加器的帶寬。但這些低值電阻會消耗功率。此外,累加器與采樣保持放大器的結構也帶來了另一種缺點,當兩個輸入電壓幅度相近而極性相反時,就會顯示出這種缺點。此時,即使輸入電壓幅度很高,得到的總和也很低,如果輸入電壓幅度相等則總和為零。對低電壓的采樣通常會使輸出電壓出現相對較大的誤差,因為每個放大器都有一些動態誤差,如殘留的寄生電荷傳入存儲電容。一個模擬電壓采樣保持電路:

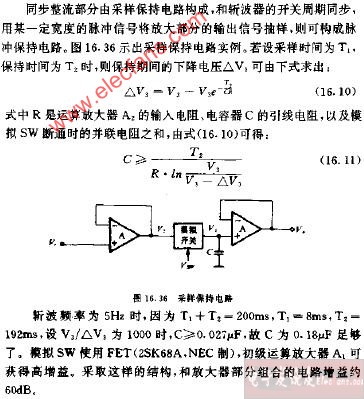

采樣保持電路圖設計(五)

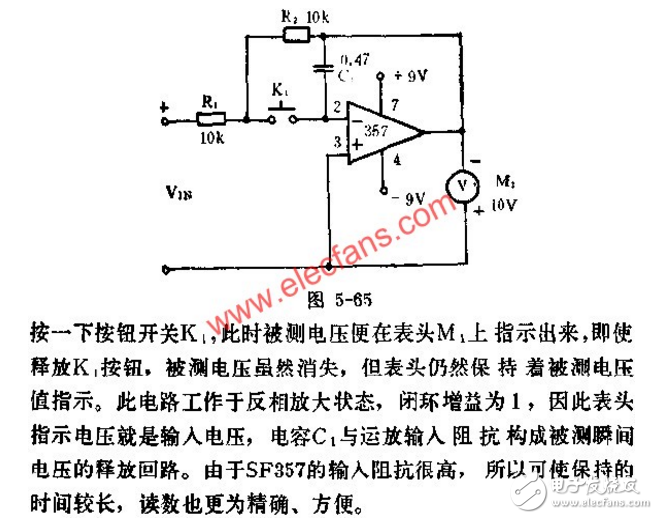

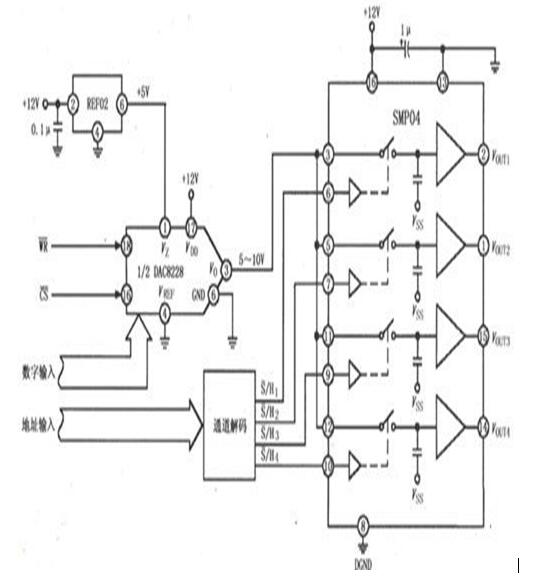

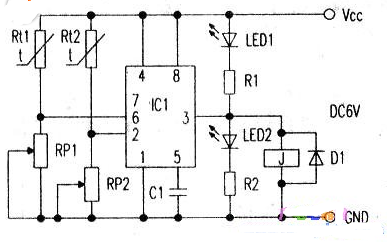

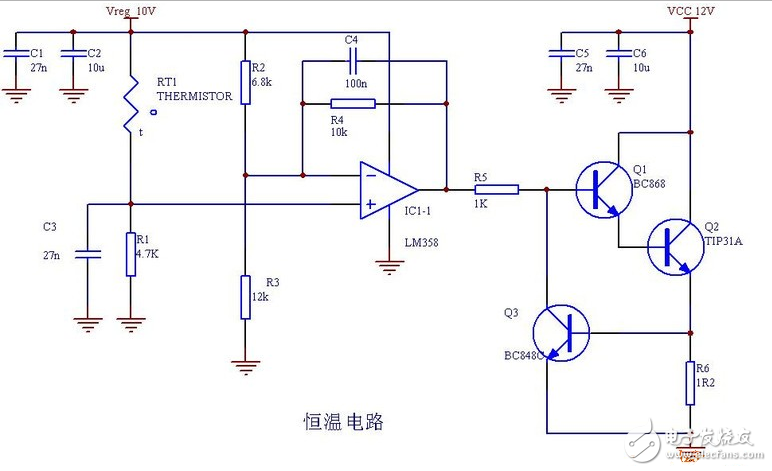

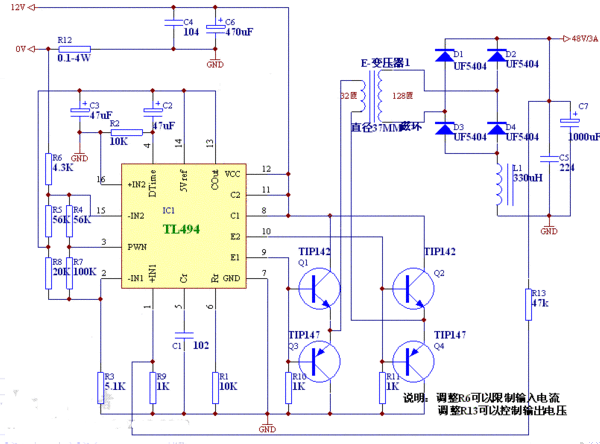

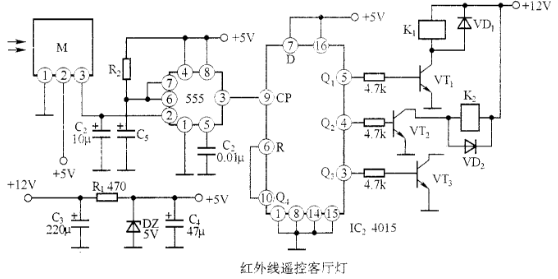

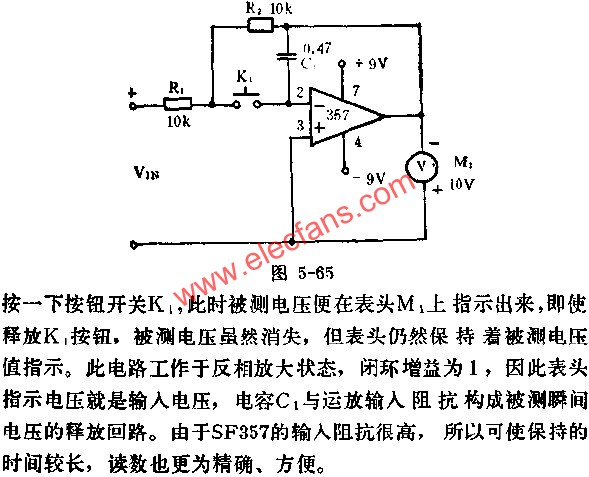

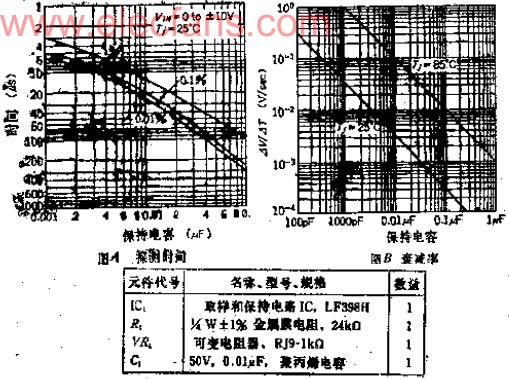

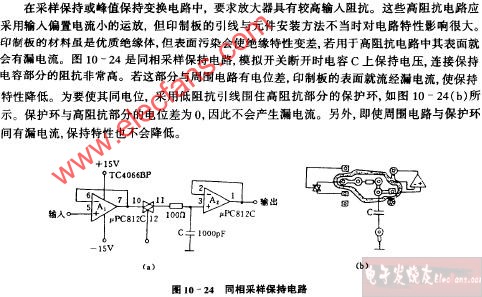

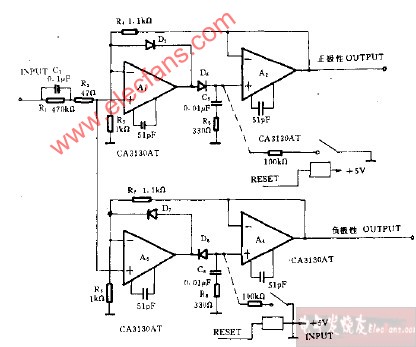

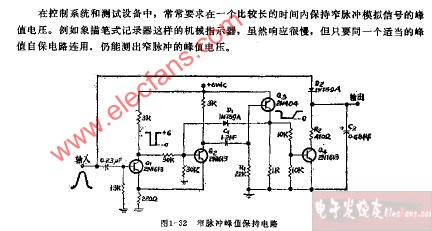

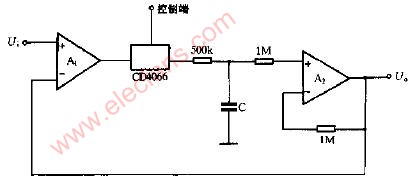

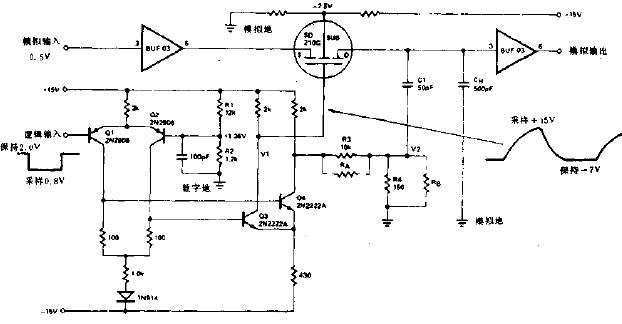

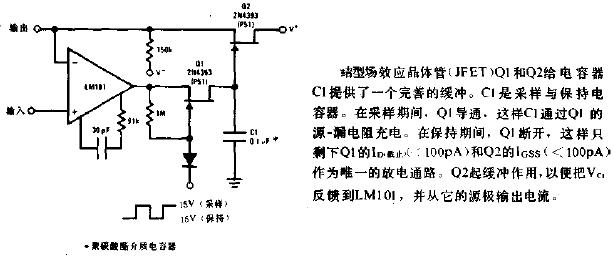

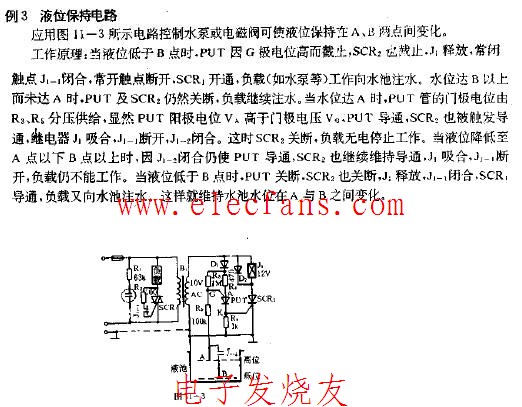

圖中所示是用SF357運放組成的電壓采樣保持電路。這種電壓采樣保持電路可以方便地觀察任一時間內的被測瞬間電壓值。

在測試電壓時,只需將其輸入端跨接于被測電壓的兩端,接著

電子發燒友App

電子發燒友App

評論