隨著FPGA融入越來越多的能力,對有效調(diào)試工具的需求將變得至關(guān)重要。對內(nèi)部可視能力的事前周密計(jì)劃將能使研制組采用正確的調(diào)試戰(zhàn)略,以更快完成他們的設(shè)計(jì)任務(wù)。

“我知道我的設(shè)計(jì)中存在一個問題,但我沒有很快找到問題所需要的內(nèi)部可視能力。”由于缺乏足夠的內(nèi)部可視能力,調(diào)試FPGA基系統(tǒng)可能會受挫。使用通常包含整個系統(tǒng)的較大FPGA時(shí),調(diào)試的可視能力成為很大的問題。為獲得內(nèi)部可視能力,設(shè)計(jì)工程師必須把一些引腳專門用作調(diào)試引腳,而不是實(shí)際用于設(shè)計(jì)。哪些工具可用于進(jìn)行內(nèi)部FPGA跡線測量?又有哪些技術(shù)可用固定的引腳數(shù)最大化內(nèi)部可視能力?

FPGA設(shè)計(jì)工程師有兩種進(jìn)行內(nèi)部跡線測量的方法:

1. 把結(jié)點(diǎn)路由至引腳,使用傳統(tǒng)的外部邏輯分析儀測試。

2. 把一個邏輯分析儀內(nèi)核插入FPGA 設(shè)計(jì),通過JTAG把由內(nèi)部FPGA存儲器保存的跡線捕獲路由輸出。

邏輯分析

FPGA開發(fā)者要在設(shè)計(jì)前期作出重要的判定,他們有意識或無意識地確定如何能夠調(diào)試他們的設(shè)計(jì)。得到內(nèi)部FPGA可視能力的最常用方法是使用邏輯分析儀,把感興趣的內(nèi)部結(jié)點(diǎn)路由至分析儀探測的引腳。這種方法提供深存儲器跡線,在這里問題成因和其影響可能有很大的時(shí)間間隔。邏輯分析儀能很好測量可能逃逸仿真的異步事件。一個例子是具有非相關(guān)頻率的兩個或多個時(shí)鐘域交互影響。邏輯分析儀提供強(qiáng)大的觸發(fā),所得到的測量結(jié)果能建立與其它系統(tǒng)事件的時(shí)間相關(guān)。

傳統(tǒng)邏輯分析儀提供狀態(tài)和定時(shí)模式,因此可同步或異步地捕獲數(shù)據(jù)。在定時(shí)模式,設(shè)計(jì)工程師能看到信號躍變間的關(guān)系。在狀態(tài)模式,設(shè)計(jì)工程師有能力觀察相對于狀態(tài)時(shí)鐘的總線。當(dāng)調(diào)試總線值至關(guān)重要的數(shù)據(jù)路徑時(shí),狀態(tài)模式是特別有用的。

有效的真實(shí)世界測量需要事先周密的計(jì)劃。使用傳統(tǒng)邏輯分析儀要顧及的主要權(quán)衡是把結(jié)點(diǎn)路由輸出至可探測的引腳。傳統(tǒng)邏輯分析儀只能觀察到路由至引腳的信號。由于還不知道潛在的電路內(nèi)調(diào)試問題,設(shè)計(jì)工程師只能把很少幾個引腳用于調(diào)試。這樣少的引腳數(shù)可能不足以提供解決手頭問題的足夠可視能力,從而延誤項(xiàng)目的完成。

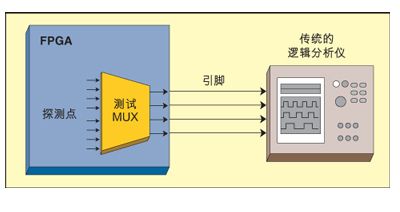

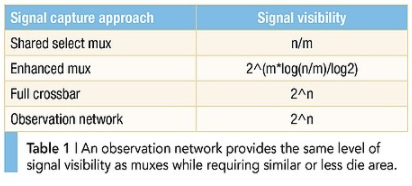

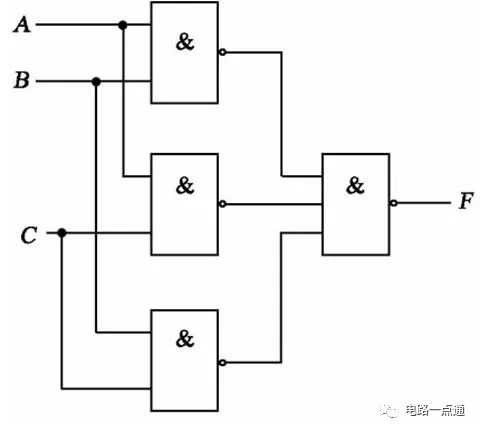

保持內(nèi)部可視能力,同時(shí)減少專用于調(diào)試引腳數(shù)的一種方法是在設(shè)計(jì)中插入開關(guān)多路轉(zhuǎn)換器(見圖1)。例如當(dāng) FPGA 設(shè)計(jì)進(jìn)入電路時(shí),可能需要觀察128個內(nèi)部結(jié)點(diǎn),這就需要一次跟蹤32個通道。在這種情況下,可在FPGA設(shè)計(jì)中實(shí)現(xiàn)多路轉(zhuǎn)換器,在給定時(shí)間內(nèi)路由出32個結(jié)點(diǎn)。為編程多路轉(zhuǎn)換器,設(shè)計(jì)工程師可下載新的配置文件,使用JTAG或通過多路轉(zhuǎn)換器上的控制線經(jīng)路由切換各信號。在設(shè)計(jì)階段,必須仔細(xì)規(guī)劃測試多路轉(zhuǎn)換器插入。否則設(shè)計(jì)工程師可能止步于不能同時(shí)訪問需要調(diào)試的結(jié)點(diǎn)。

圖1: 測試多路轉(zhuǎn)換器的插入使設(shè)計(jì)工程師有能力路由出內(nèi)部信號的子集,圖中為Agilent 16702B所捕獲的跡線。

最小化調(diào)試專用引腳數(shù)的第二種方法是時(shí)分復(fù)用(TDM)。TDM復(fù)用常用于設(shè)計(jì)原型,此時(shí)把多片F(xiàn)PGA 作為單片ASIC的原型,從而用于最小化調(diào)試專用引腳數(shù)。這項(xiàng)技術(shù)最適合用于處理較慢的內(nèi)部電路。假定使用8位總線的50MHz設(shè)計(jì)(時(shí)鐘沿間為20ns)需要電路內(nèi)的可視能力。使用100MHz在第一個10ns期間采樣低4bit,在第二個10ns期間采樣高4位。這樣僅用4個引腳,就可在每個20ns周期內(nèi)捕獲到全部8位的調(diào)試信息。在捕獲跡線后,組合相繼的4位捕獲就可重建8位跡線。TDM復(fù)用也有一些缺點(diǎn)。如果用傳統(tǒng)邏輯分析儀捕獲跡線,觸發(fā)就變得非常復(fù)雜和容易出錯。例如在8位碼型上的觸發(fā)就包括把邏輯分析儀設(shè)置到尋找跟隨規(guī)定4位碼型后的另一特定4位碼型。但邏輯分析儀不知道哪一個4位是 8位組的開始,因此要在與觸發(fā)設(shè)置相匹配的條件上觸發(fā)-而不是使用者所中意的觸發(fā)條件。

采用TDM復(fù)用時(shí)得到的測量結(jié)果有精確的周期。但設(shè)計(jì)工程師卻丟失了時(shí)鐘周期間的定時(shí)關(guān)系信息。通常單端引腳的速度和邏輯分析儀收集跡線的采集速度(狀態(tài)模式)限制了壓縮比。例如如果最大單端引腳速度是200MHz,內(nèi)部電路運(yùn)行于高達(dá)100 MHz,那么可實(shí)現(xiàn)的最大壓縮比是2:1。

隨著給定FPGA設(shè)計(jì)的成熟,它可能會增強(qiáng)和改變。原來專門用于調(diào)試的引腳會被用于設(shè)計(jì)增強(qiáng)。或開始就限制了設(shè)計(jì)的引腳。另一種調(diào)試技術(shù)為這類情況帶來價(jià)值。

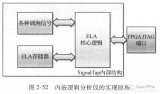

邏輯分析內(nèi)核

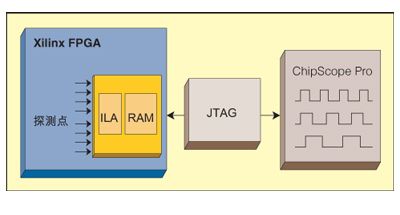

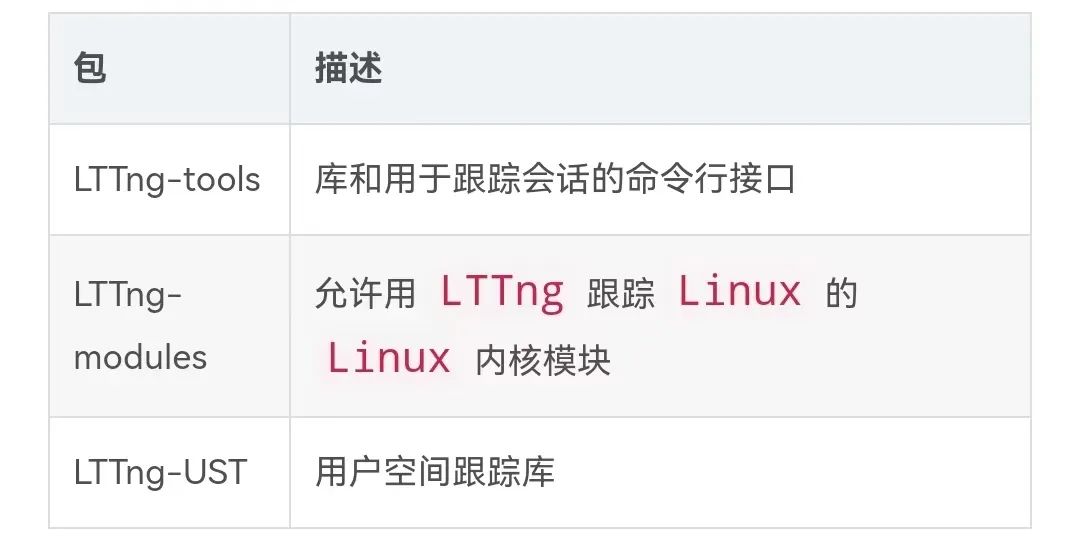

現(xiàn)在大多數(shù)FPGA 廠商也提供邏輯分析(見圖2)。這些 IP在合成前或合成后插入FPGA。內(nèi)核包含觸發(fā)電路,以及用于設(shè)置測量和內(nèi)部RAM,以保存跡線的資源。插入設(shè)計(jì)的邏輯分析內(nèi)核改變了設(shè)計(jì)的定時(shí),因此大多數(shù)設(shè)計(jì)工程師都把內(nèi)核永久性地留在設(shè)計(jì)內(nèi)。

圖2: 從 JTAG 下載邏輯分析儀的配置,圖中的例子是 Xilinx ChipScopePro。

對于電路內(nèi)配置,可通過JTAG訪問內(nèi)核,以及為觀察而把捕獲數(shù)據(jù)傳送到PC。如果內(nèi)核消耗不到5%的可用資源,F(xiàn)PGA 內(nèi)核就能充分發(fā)揮作用。如果 FPGA的尺寸使內(nèi)核要消耗超過10%的資源,設(shè)計(jì)工程師在使用這種方法時(shí)將會遇到很多問題。

邏輯分析內(nèi)核有三項(xiàng)主要優(yōu)點(diǎn)。

1. 它們的使用不增加引腳。可通過FPGA 上已有的專門JTAG引腳訪問。即使沒有其它可用引腳,這種調(diào)試方法也能得到內(nèi)部可視能力。

2. 簡單的探測。探測包括把結(jié)點(diǎn)路由到內(nèi)部邏輯分析儀的輸入。不需要擔(dān)心為得到有效信息,應(yīng)如何連接到電路板上,也不存在信號完整性問題。

3. 邏輯分析內(nèi)核是便宜的。FPGA廠商把他們的業(yè)務(wù)模型建立于用硅片所獲取價(jià)值的基礎(chǔ)上。所以所用的調(diào)試IP 通常能以低于$1,000美元的價(jià)格獲得。

使用內(nèi)部邏輯分析內(nèi)核也有三方面的影響。

1. 內(nèi)核的尺寸限制了在大FPGA中的使用。此外由于內(nèi)部FPGA存儲器用于跡線,使跡線深度很淺。

2. 設(shè)計(jì)工程師必須放棄把內(nèi)部存儲器用于調(diào)試,存儲器會由所作的設(shè)計(jì)使用。

3. 內(nèi)部邏輯分析儀只工作于狀態(tài)模式。它們捕獲的數(shù)據(jù)與規(guī)定的時(shí)鐘同步,而不能提供信號定時(shí)關(guān)系。

混合技術(shù)

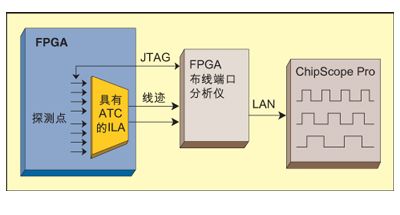

一些FPGA廠商已開始與傳統(tǒng)邏輯分析儀廠商聯(lián)合開發(fā)組合技術(shù)(見圖 3)。例如Agilent 和 Xilinx 最近聯(lián)合為Xilinx的ChipScope開發(fā)2M狀態(tài)深存儲器。

圖3: 混合內(nèi)部和傳統(tǒng)邏輯分析的第一個例子是Agilent 和 Xilinx聯(lián)合為ChipScopePro開發(fā)的深存儲器,通過TDM復(fù)用能把引腳數(shù)減到最少。

這一解決方案把內(nèi)部邏輯分析內(nèi)核用于觸發(fā)。在滿足內(nèi)核的觸發(fā)條件時(shí),內(nèi)核把跡線信息從經(jīng)路由的結(jié)點(diǎn)傳送到內(nèi)核,再送到引腳。引腳通過mictor連接器接到一個小的外部跟蹤盒。該解決方案融入了TDM復(fù)用,以減少調(diào)試專用引腳數(shù)。根據(jù)內(nèi)部電路的速度,復(fù)用壓縮可能是1:1,2:1或4:1。由于跡線未在內(nèi)部保存,因此IP內(nèi)核要小于帶跡線存儲器的邏輯分析IP。

如何作出決定?

傳統(tǒng)邏輯分析和基于內(nèi)核的邏輯分析技術(shù)都很有用。在選擇最適合您調(diào)試需要的方案時(shí),事先考慮一些因素將能幫助您作出決定。下面這幾個問題能幫助您確定哪種方案最為有效。

1. 您預(yù)計(jì)會遇到哪種類型的調(diào)試問題?用內(nèi)部邏輯分析儀能找到較簡單的問題,而傳統(tǒng)邏輯分析儀則能勝任復(fù)雜的故障。

2. 除了狀態(tài)模式外,您還需要捕獲定時(shí)信息嗎?如果需要,傳統(tǒng)邏輯分析儀能適應(yīng)這一要求。

3. 需要多深的跡線?傳統(tǒng)邏輯分析儀可在各通道上捕獲達(dá)64M的跡線,而內(nèi)部邏輯分析內(nèi)核更適合淺的跡線。

4. 有多少引腳可專門用于調(diào)試?引腳數(shù)越少,使用內(nèi)部邏輯分析儀就越適合。

5. 必須為新工具投入多少資金?雖然32通道傳統(tǒng)邏輯分析儀的起價(jià)為$6K,但內(nèi)部邏輯分析儀及相隨波形觀察器的起價(jià)還不到$1K。

6. 研制組能容忍對FPGA設(shè)計(jì)的沖擊嗎?內(nèi)核只能在大的 FPGA上工作,并會改變設(shè)計(jì)的定時(shí)。對所有尺寸和類型的FPGA,傳統(tǒng)邏輯分析儀的路由信號輸出對設(shè)計(jì)和工作的影響甚微。

基于邏輯分析內(nèi)核的FPGA電路內(nèi)調(diào)試 - 全文

相關(guān)推薦

SoC FPGA:產(chǎn)品開發(fā)中的自適應(yīng)性能分析

SoC新器件包括ARM應(yīng)用處理器和FPGA架構(gòu),為推出更高效的產(chǎn)品帶來了新機(jī)遇。片內(nèi)調(diào)試硬件、FPGA工具和軟件調(diào)試以及分析工具的創(chuàng)新已經(jīng)與硬件創(chuàng)新相匹配,因此,開發(fā)這些器件以及充分發(fā)揮其功率特性優(yōu)勢變得與在固定的ASIC器件上開發(fā)軟件一樣簡單高效。

2013-07-17 16:29:24 1125

1125

1125

1125

FPGA數(shù)字核脈沖分析器硬件電路

基于FPGA 的數(shù)字核脈沖分析器硬件設(shè)計(jì)方案,該方案采用現(xiàn)場可編程邏輯部件(FPGA),完成數(shù)字多道脈沖幅度分析儀的硬件設(shè)計(jì)。

2015-02-03 09:55:05 1869

1869

1869

1869

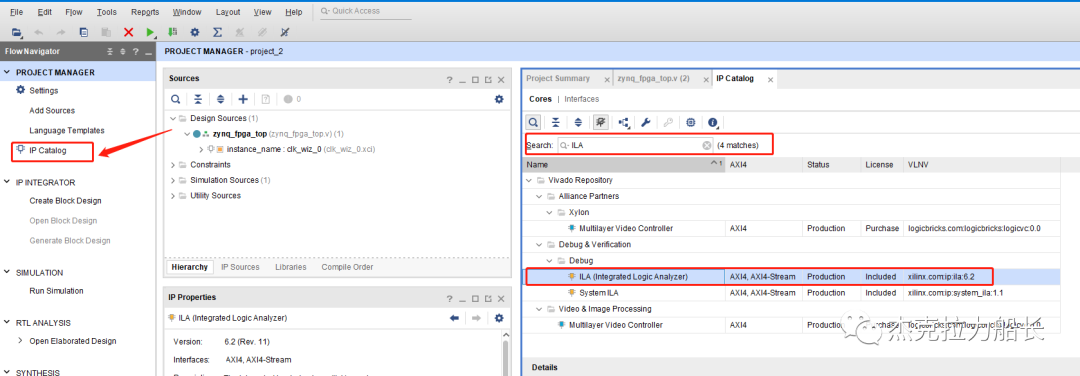

FPGA學(xué)習(xí)之vivado邏輯分析儀的使用

其中待測設(shè)計(jì)就是我們整個的邏輯設(shè)計(jì)模塊,在線邏輯分析儀也同樣是在FPGA設(shè)計(jì)中。通過一個或多個探針來采集希望觀察的信號。然后通過JTAG接口,將捕獲到的數(shù)據(jù)通過下載器回傳給我們的用戶界面,以便我們進(jìn)行觀察。

2023-07-25 09:52:58 503

503

503

503

集成邏輯分析儀(ILA)的使用方法

在日常FPGA開發(fā)過程中,邏輯代碼設(shè)計(jì)完成后,為了驗(yàn)證代碼邏輯的正確性,優(yōu)先使用邏輯仿真(modesim)進(jìn)行驗(yàn)證。仿真驗(yàn)證通過后進(jìn)行板級驗(yàn)證時(shí),使用邏輯分析儀進(jìn)行分析和驗(yàn)證邏輯是否正確。FPGA

2023-10-01 17:08:00 1454

1454

1454

1454

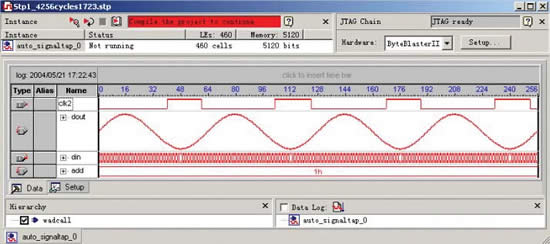

淺析FPGA的調(diào)試-內(nèi)嵌邏輯分析儀(SignalTap)原理及實(shí)例

對于FPGA調(diào)試,主要以Intel FPGA為例,在win10 Quartus ii 17.0環(huán)境下進(jìn)行仿真和調(diào)試,開發(fā)板類型EP4CE15F17。

2024-01-12 09:34:14 785

785

785

785

FPGA與數(shù)字邏輯電路的區(qū)別

FPGA則應(yīng)該理解為可用電腦編輯的數(shù)字邏輯電路集成芯片,其實(shí)是在描繪一個數(shù)字邏輯電路。關(guān)于兩者的區(qū)別在于以下:1、速度上(兩者最大的差別)因?yàn)?b class="flag-6" style="color: red">FPGA是硬件電路,運(yùn)行速度則取決于晶振速度,系統(tǒng)

2021-07-13 08:43:08

FPGA培訓(xùn)--FPGA高級邏輯設(shè)計(jì)研修班

以及高速數(shù)字電路的時(shí)序設(shè)計(jì)與優(yōu)化。相信通過三天的學(xué)習(xí),將會對學(xué)員在邏輯設(shè)計(jì)領(lǐng)域的工作和學(xué)習(xí)大有裨益。課程時(shí)間的安排上授課占60%,實(shí)驗(yàn)占40%。五、培訓(xùn)對象課程適合于使用FPGA器件進(jìn)行科研、教學(xué)和產(chǎn)品

2009-07-24 13:13:48

FPGA實(shí)戰(zhàn)演練邏輯篇17:FPGA電源電路設(shè)計(jì)

FPGA電源電路設(shè)計(jì)本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 整個系統(tǒng)需要三檔不同的電源電壓,即

2015-04-22 12:06:21

FPGA實(shí)戰(zhàn)演練邏輯篇48:基本的時(shí)序分析理論1

基本的時(shí)序分析理論1本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 何謂靜態(tài)時(shí)序分析(STA,Static

2015-07-09 21:54:41

FPGA實(shí)戰(zhàn)演練邏輯篇69:基于FPGA的在線系統(tǒng)調(diào)試概述

的板級調(diào)試方法有很多,借助于常規(guī)的示波器和邏輯分析儀的調(diào)試方法是最典型的手段。如圖10.1所示,基于傳統(tǒng)的臺式示波器或邏輯分析儀進(jìn)行板級調(diào)試有著諸多的不便,相對于設(shè)計(jì)電路深藏在芯片內(nèi)部的FPGA

2015-09-02 18:39:49

FPGA實(shí)現(xiàn)邏輯函數(shù)用的什么電路結(jié)構(gòu)?

FPGA實(shí)現(xiàn)邏輯函數(shù)用的什么電路結(jié)構(gòu)?

2017-01-01 21:49:23

FPGA工作調(diào)試方式

FPGA調(diào)試時(shí)間占用的比較多,想了解下這個調(diào)試是以什么方式進(jìn)行的,需要和板子硬件電路部分打交道多還是和軟件邏輯打交道多,主要偏向哪一個方向,請有經(jīng)驗(yàn)的解釋下

2012-11-25 02:10:05

FPGA最小系統(tǒng)的下載配置與調(diào)試接口電路設(shè)計(jì)

下載配置與調(diào)試接口電路設(shè)計(jì)FPGA是SRAM型結(jié)構(gòu),本身并不能固化程序。因此FPGA需要一片F(xiàn)lash結(jié)構(gòu)的配置芯片來存儲邏輯配置信息,用于進(jìn)行上電配置。以Altera公司的FPGA為例,配置芯片

2019-06-11 05:00:07

fpga時(shí)序邏輯電路的分析和設(shè)計(jì)

fpga時(shí)序邏輯電路的分析和設(shè)計(jì) 時(shí)序邏輯電路的結(jié)構(gòu)及特點(diǎn)時(shí)序邏輯電路——任何一個時(shí)刻的輸出狀態(tài)不僅取決于當(dāng)時(shí)的輸入信號,還與電路的原狀態(tài)有關(guān)。[hide][/hide]

2012-06-20 11:18:44

調(diào)試FPGA時(shí),TD軟件是否支持內(nèi)部邏輯分析功能?

調(diào)試FPGA時(shí),TD軟件是否支持內(nèi)部邏輯分析(抓波形)功能?

2023-08-11 10:32:27

調(diào)試底層硬件模塊的邏輯是什么

調(diào)試底層硬件模塊的邏輯是什么?怎樣在基于FPGA的嵌入式硬件設(shè)計(jì)添加一個debug的硬件模塊?

2021-12-24 06:37:53

邏輯分析儀測試在基于FPGA的LCD顯示控制中的應(yīng)用

摘要:邏輯分析儀作為基礎(chǔ)儀器,應(yīng)該在基礎(chǔ)數(shù)字電路教學(xué)中得到廣泛應(yīng)用。本文介紹了基于FPGA的液晶顯示控制設(shè)計(jì)方案,通過使用OLA2032B邏輯分析儀,對控制線進(jìn)行監(jiān)測與分析,保證設(shè)計(jì)方案的準(zhǔn)確性

2017-10-19 09:07:43

邏輯定時(shí)分析儀和邏輯狀態(tài)分析儀的區(qū)別是什么?

邏輯分析儀在數(shù)字電路測試中的觸發(fā)選擇延遲觸發(fā)有哪幾種類型?邏輯定時(shí)分析儀和邏輯狀態(tài)分析儀的區(qū)別是什么?

2021-04-12 06:55:10

[分享]組合邏輯電路的分析與設(shè)計(jì)

本帖最后由 gk320830 于 2015-3-5 08:04 編輯

第三章 組合邏輯電路的分析與設(shè)計(jì) 在任何時(shí)刻,輸出狀態(tài)只決定于同一時(shí)刻各輸入狀態(tài)的組合,而與先前狀態(tài)無關(guān)的邏輯電路稱為

2009-04-07 10:54:26

keil 調(diào)試時(shí)用邏輯分析時(shí)添加引腳PORTA_0為什么總是顯示unkno...

keil 調(diào)試時(shí)用邏輯分析時(shí)添加引腳PORTA_0為什么總是顯示unknown signal

2014-03-17 16:05:44

【實(shí)驗(yàn)】入門基礎(chǔ)篇--FPGA數(shù)字邏輯電路設(shè)計(jì)與分析:全加器

FPGA數(shù)字邏輯電路的設(shè)計(jì)與分析,包含項(xiàng)目實(shí)例、全流程設(shè)計(jì)說明文檔,項(xiàng)目源代碼文件。

2021-03-30 14:48:05

【案例分享】玩轉(zhuǎn)FPGA必學(xué)的復(fù)雜邏輯設(shè)計(jì)

(Interconnect)三個部分。 現(xiàn)場可編程門陣列(FPGA)是可編程器件,與傳統(tǒng)邏輯電路和 門陣列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的結(jié)構(gòu)。FPGA利用小型查找表(16×1RAM

2019-08-11 04:30:00

【夢翼師兄今日分享】 SignalTapII在線調(diào)試邏輯分析儀使用

FPGA開發(fā)的基本流程,幾乎都介紹到了嵌入式邏輯分析儀(或稱之為虛擬邏輯分析儀)的相關(guān)知識,包括為什么要有這樣的在線調(diào)試邏輯分析儀,它可以做什么,什么情況下使用,基于什么樣的原理,有哪些邏輯分析儀等等

2019-12-04 10:30:42

為什么FPGA可以用來實(shí)現(xiàn)組合邏輯電路和時(shí)序邏輯電路呢?

為什么FPGA可以用來實(shí)現(xiàn)組合邏輯電路和時(shí)序邏輯電路呢?

2023-04-23 11:53:26

便攜式邏輯分析儀電路設(shè)計(jì)

了邏輯分析儀的成本且便于攜帶。重點(diǎn)闡述硬件電路部分的設(shè)計(jì)。關(guān)鍵詞 邏輯分析儀;USB接口;FPGA;FIFO傳輸邏輯分析儀是數(shù)字設(shè)計(jì)驗(yàn)證與調(diào)試過程中應(yīng)用廣泛的工具,其能夠檢驗(yàn)數(shù)字電路是否正常工作,并幫助

2019-06-18 07:56:45

加速FPGA系統(tǒng)實(shí)時(shí)調(diào)試過程和方法詳細(xì)介紹

使得設(shè)計(jì)調(diào)試和檢驗(yàn)變成設(shè)計(jì)周期中最困難的流程。本文重點(diǎn)介紹在調(diào)試FPGA系統(tǒng)時(shí)遇到的問題及有助于提高調(diào)試效率的技術(shù),通過邏輯分析儀配合FPGA View軟件快速有效的觀測FPGA內(nèi)部節(jié)點(diǎn)信號。最后提供了FPGA具體的調(diào)試過程和方法。

2019-06-25 07:51:47

如何使用SignalTap II邏輯分析儀調(diào)試FPGA?

本文將介紹SignalTap II邏輯分析儀的主要特點(diǎn)和使用流程,并以一個實(shí)例介紹該分析儀具體的操作方法和步驟。

2021-04-29 06:12:52

如何用內(nèi)部邏輯分析儀調(diào)試FPGA?

推動FPGA調(diào)試技術(shù)改變的原因是什么外部邏輯分析儀受到的限制是什么如何用內(nèi)部邏輯分析儀調(diào)試FPGA

2021-04-30 06:44:08

小編科普一下link logic邏輯分析儀調(diào)試器

link logic邏輯分析儀調(diào)試器有哪些優(yōu)點(diǎn)呢?link logic邏輯分析儀調(diào)試器有哪些功能呢?

2022-02-24 06:13:38

推動FPGA調(diào)試技術(shù)發(fā)展的幾項(xiàng)潛在原因

”的方法。先將要觀察的FPGA內(nèi)部信號引到引腳,然后用外部的邏輯分析儀捕獲數(shù)據(jù)。然而當(dāng)設(shè)計(jì)的復(fù)雜程度增加時(shí),這個方法就不再適合了,其中有幾個原因。 &

2010-01-08 15:05:27

數(shù)字電路與邏輯設(shè)計(jì)電路的分析和方法

數(shù)字電路與邏輯設(shè)計(jì)數(shù)字邏輯電路的分析和方法,常用集成數(shù)字邏輯電路的功能和應(yīng)用;主要內(nèi)容包括:邏輯代數(shù)基礎(chǔ)、組合邏輯電路分析和設(shè)計(jì)、常用組合邏輯電路及MSI組合電路模塊的應(yīng)用,時(shí)序邏輯電路的分析

2021-08-06 07:33:41

求一款虛擬FPGA邏輯驗(yàn)證分析儀的設(shè)計(jì)方案

虛擬FPGA邏輯驗(yàn)證分析儀的工作原理是什么?虛擬FPGA邏輯驗(yàn)證分析儀有哪幾個主要工作環(huán)節(jié)?

2021-04-29 07:07:24

淺析邏輯分析儀的原理

邏輯分析儀是常用的電子儀器之一,主要應(yīng)用于做數(shù)字電路測試,FPGA調(diào)試,CPU/DSP調(diào)試,數(shù)字IQ/IF分析,無線通信/雷達(dá)接收機(jī)測試等場合。邏輯分析儀由模塊和計(jì)算機(jī)組成(當(dāng)然還有探頭),模塊負(fù)責(zé)

2019-06-28 07:51:30

示波器和邏輯分析儀聯(lián)合調(diào)試SPI通訊

在調(diào)試MCU 的SPI 接口時(shí),偶爾發(fā)現(xiàn)通信不成功的情況,為了找出問題原因,使用MI1062 抓取了數(shù)字信號和模擬信號進(jìn)行對比分析。 1、邏輯分析儀測試信號邏輯 啟動MI1062 邏輯分析儀功能

2017-07-27 09:51:02

組合邏輯與時(shí)序邏輯電路一般分析方法

你了解如何分析組合邏輯電路與時(shí)序邏輯電路嗎?數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時(shí)序邏輯電路(簡稱時(shí)序電路)。邏輯電路的特點(diǎn)組合邏輯電路在

2021-11-18 06:30:00

請問16~32點(diǎn)邏輯分析儀能做什么?

公司10年前太克的已經(jīng)報(bào)廢,因?yàn)榇蠹叶紤械勉^現(xiàn)在的 FPGA 都有內(nèi)建軟核邏輯分析儀,每次測都上百點(diǎn)...16~32點(diǎn)邏輯分析儀能做什么? FPGA 運(yùn)行都破百 MHZ..不知道號稱n百M(fèi)HZ邏輯分析儀抓的到嗎?

2019-09-04 23:50:44

一種基于FPGA技術(shù)的虛擬邏輯分析儀的研究與實(shí)現(xiàn)

一種基于FPGA技術(shù)的虛擬邏輯分析儀的研究與實(shí)現(xiàn):邏輯分析儀的現(xiàn)狀" 發(fā)展趨勢及研制虛擬邏輯分析儀的必要性, 論述了基于FPGA技術(shù)的虛擬邏輯分析儀的設(shè)計(jì)方案及具體實(shí)現(xiàn)方法,介紹

2008-11-27 13:13:04 29

29

29

29基于FPGA的USB2.0高速、低成本的虛擬邏輯分析儀的設(shè)計(jì)

基于FPGA的USB2.0高速、低成本的虛擬邏輯分析儀的設(shè)計(jì)原理與實(shí)現(xiàn)方法:本文介紹了一種基于FPGA的USB2.0高速、低成本的虛擬邏輯分析儀的設(shè)計(jì)原理與實(shí)現(xiàn)方法。重點(diǎn)介紹了邏輯分析儀

2009-06-22 19:11:17 57

57

57

57TLA邏輯分析儀原理與應(yīng)用硬件調(diào)試基礎(chǔ)教程

TLA邏輯分析儀原理與應(yīng)用硬件調(diào)試基礎(chǔ)教程:數(shù)字系統(tǒng)的調(diào)試過程– 首先啟動硬件電路– 調(diào)試硬件的設(shè)計(jì)錯誤– 調(diào)試部局或結(jié)構(gòu)錯誤 短路, 開路, 連接錯誤等

2009-10-17 17:33:59 19

19

19

19使用SignalTap II邏輯分析儀調(diào)試FPGA

本文介紹了可編程邏輯器件開發(fā)工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個具體的設(shè)計(jì)實(shí)例,詳細(xì)介紹使用SignalTap II對FPGA調(diào)試的具體方法和步驟。關(guān)鍵字 : S

2009-11-01 14:49:39 45

45

45

45邏輯分析儀入門手冊

邏輯分析儀入門手冊:與許多電子測試和測量工具一樣,邏輯分析儀是一種針對特定類型問題的解決方案。它是一種通用工具,可以幫助您調(diào)試數(shù)字硬件、檢驗(yàn)設(shè)計(jì)和調(diào)試嵌入式軟件

2009-11-15 22:34:18 64

64

64

64組合邏輯電路的分析、設(shè)計(jì)和調(diào)試

組合邏輯電路的分析、設(shè)計(jì)和調(diào)試(一)一、實(shí)驗(yàn)?zāi)康?.進(jìn)一步熟悉數(shù)字邏輯實(shí)驗(yàn)箱的使用。2.掌握用SSI(小規(guī)模數(shù)字集成電路)構(gòu)成的組合邏輯電路的分析與設(shè)計(jì)方法。

2009-11-19 15:01:53 185

185

185

185簡化Xilinx和Altera FPGA調(diào)試過程

簡化Xilinx和Altera FPGA調(diào)試過程:通過FPGAViewTM 解決方案,如混合信號示波器(MSO)和邏輯分析儀,您可以在Xilinx 和Altera FPGA 內(nèi)部迅速移動探點(diǎn),而無需重新編譯設(shè)計(jì)方案。能夠把內(nèi)部FPGA

2009-11-20 17:46:26 26

26

26

26實(shí)用FPGA的調(diào)試工具—ChipScope Pro

實(shí)用FPGA的調(diào)試工具—ChipScope Pro

ChipScope Pro應(yīng)用于FPGA調(diào)試階段,它具有傳統(tǒng)邏輯分析儀的功能,可以觀察FPGA內(nèi)部的任何信號,觸發(fā)條件,數(shù)據(jù)寬度和深度等的設(shè)

2010-02-09 15:10:46 95

95

95

95TLA邏輯分析儀原理與應(yīng)用 (硬件調(diào)試基礎(chǔ)教程)

TLA邏輯分析儀原理與應(yīng)用 -硬件調(diào)試基礎(chǔ)教程。

2010-08-05 15:08:02 49

49

49

49使用邏輯分析儀調(diào)試定時(shí)問題

使用邏輯分析儀調(diào)試定時(shí)問題

在今天的數(shù)字世界, 嵌入式系統(tǒng)比以往任何時(shí)候都更為復(fù)雜。 使用速度更快、 功耗更

2010-08-06 07:49:46 24

24

24

24FPGA電路測試及故障分析

目錄•FPGA調(diào)試的挑戰(zhàn)•傳統(tǒng)的FPGA調(diào)試方案•Agilent FPGA動態(tài)探頭的調(diào)試方案•總結(jié)

2010-10-11 11:04:36 26

26

26

26LAB6000系列邏輯分析儀簡介

LAB6000系列邏輯分析儀是一款緊湊、快速調(diào)試數(shù)字電路設(shè)計(jì)強(qiáng)有力的便攜式邏輯分析儀;高速的USB2.0接口、高端的FPGA、強(qiáng)大的ARM處理器等組成的嵌入式系統(tǒng)全方位智能控制;高速、高

2010-11-15 17:15:58 9

9

9

9LAB7000系列邏輯分析儀簡介

LAB7000系列邏輯分析儀是一款緊湊、快速調(diào)試數(shù)字電路設(shè)計(jì)強(qiáng)有力的便攜式邏輯分析儀;高速的USB2.0接口、高端的FPGA、強(qiáng)大的ARM處理器等組成的嵌入式系統(tǒng)全方位智能控制;高速、高

2010-11-16 16:23:20 35

35

35

35虛擬FPGA邏輯驗(yàn)證分析儀的設(shè)計(jì)

虛擬FPGA邏輯驗(yàn)證分析儀的設(shè)計(jì)

隨著FPGA技術(shù)的廣泛使用,越來越需要一臺能夠測試驗(yàn)證FPGA芯片中所下載電路邏輯時(shí)序是否正確的儀器。目前,雖然Agilent、Tektronix 等大公司生

2008-10-15 08:56:31 575

575

575

575

邏輯分析儀測試在基于FPGA的LCD顯示控制中的應(yīng)用

邏輯分析儀測試在基于FPGA的LCD顯示控制中的應(yīng)用

摘要:邏輯分析儀作為基礎(chǔ)儀器,應(yīng)該在基礎(chǔ)數(shù)字電路教學(xué)中得到廣泛應(yīng)用。本文介紹了

2008-11-27 09:38:24 1031

1031

1031

1031

使用SignalTap II邏輯分析儀調(diào)試FPGA

摘 要 :本文介紹了可編程邏輯器件開發(fā)工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個具體的設(shè)計(jì)實(shí)例,詳細(xì)介紹使用SignalTap II對FPGA調(diào)試的具體方

2009-06-20 10:42:18 1365

1365

1365

1365

使用邏輯分析儀調(diào)試時(shí)序問題

使用邏輯分析儀調(diào)試時(shí)序問題

在今天的數(shù)字世界,嵌入式系統(tǒng)比以往任何時(shí)候都更為復(fù)雜。使用速度更快、功耗更低的設(shè)備和功能更強(qiáng)大的電路,

2009-08-26 12:09:14 1389

1389

1389

1389

FPGA硬件系統(tǒng)的調(diào)試方法

FPGA硬件系統(tǒng)的調(diào)試方法

在調(diào)試FPGA電路時(shí)要遵循一定的原則和技巧,才能減少調(diào)試時(shí)間,避免誤操作損壞電路。一般情況下,可以參考以下步驟進(jìn)行

2010-02-08 14:44:42 2558

2558

2558

2558內(nèi)調(diào)制雜音,什么是內(nèi)調(diào)制雜音

內(nèi)調(diào)制雜音,什么是內(nèi)調(diào)制雜音

當(dāng)不同頻率的信號共享同一傳輸介質(zhì)的時(shí)候,可能導(dǎo)致內(nèi)調(diào)制雜音。這些信號的頻率是某兩個頻率

2010-03-17 17:18:11 455

455

455

455嵌入式邏輯分析儀在FPGA測試中的應(yīng)用

邏輯分析儀自1973年問世以來,在短短幾十年的時(shí)間內(nèi)得到了迅速的發(fā)展。傳統(tǒng)邏輯分析儀利用芯片的引腳對信號采樣,并送到顯示部分對系統(tǒng)進(jìn)行分析,但對于無引腳的封裝類型,傳統(tǒng)邏輯分析儀很難有效的監(jiān)測系統(tǒng)內(nèi)部信號。而在FPGA測試中,嵌入式邏輯分析儀(ELA

2011-03-15 14:52:53 38

38

38

38邏輯分析儀在嵌入式開發(fā)調(diào)試中的應(yīng)用

嵌入式開發(fā)調(diào)試中,開發(fā)人員的調(diào)試手段包括斷點(diǎn)、觸發(fā)和跟蹤三種。在線調(diào)試器(I(、I))與邏輯分析儀(IA)協(xié)調(diào)工作,為調(diào)試新一代嵌入式處理器的開發(fā)人員提供了上述三種調(diào)試手段。

2011-11-07 15:58:09 33

33

33

33FPGA培訓(xùn)基礎(chǔ)資料

1. FPGA技術(shù)基礎(chǔ);2. FPGA基本設(shè)計(jì)流程及工具;3. FPGA設(shè)計(jì)指導(dǎo)原則與設(shè)計(jì)技巧;4. FPGA設(shè)計(jì)約束;5. TestBench設(shè)計(jì)與ModelSim仿真;6. FPGA配置及片內(nèi)調(diào)試技術(shù);7. 基于ISE、EDK的FPGA設(shè)計(jì)實(shí)例

2012-05-22 14:52:14 283

283

283

283Xilinx FPGA集成電路的動態(tài)老化試驗(yàn)

3 FPGA設(shè)計(jì)流程 完整的FPGA 設(shè)計(jì)流程包括邏輯電路設(shè)計(jì)輸入、功能仿真、綜合及時(shí)序分析、實(shí)現(xiàn)、加載配置、調(diào)試。FPGA 配置就是將特定的應(yīng)用程序設(shè)計(jì)按FPGA設(shè)計(jì)流程轉(zhuǎn)化為數(shù)據(jù)位流加載

2013-01-16 11:52:22 16

16

16

16FPGA硬件電路的調(diào)試必備原則和技巧

在調(diào)試FPGA電路時(shí)要遵循必須的原則和技巧,才能降低調(diào)試時(shí)間,防止誤操作損壞電路。通常情況下,參考以下步驟執(zhí)行 FPGA硬件系統(tǒng)的調(diào)試。 1、在焊接硬件電路前,首先要測試電路板

2013-01-16 11:59:58 4665

4665

4665

4665怎樣使用 MSO 和 MDO 系列示波器的基本邏輯分析儀功能迅速驗(yàn)證和調(diào)試數(shù)字電路

怎樣使用 MSO 和 MDO 系列示波器的基本邏輯分析儀功能迅速驗(yàn)證和調(diào)試數(shù)字電路

2017-09-16 10:31:31 13

13

13

13一種基于FPGA的SDRAM設(shè)計(jì)與邏輯時(shí)序分析

由于同步動態(tài)隨機(jī)存儲器SDRAM內(nèi)部結(jié)構(gòu)原因?qū)е缕淇刂?b class="flag-6" style="color: red">邏輯比較復(fù)雜。現(xiàn)場可編程邏輯門陣列FPGA作為一種半定制電路具有速度快、內(nèi)部資源豐富、可重構(gòu)等優(yōu)點(diǎn)。本文設(shè)計(jì)了一種基于FPGA的SDRAM

2017-11-18 12:42:03 2054

2054

2054

2054

傳統(tǒng)FPGA調(diào)試方案與EXOSTIV Probe硬件調(diào)試儀

相信每一個電子工程師在項(xiàng)目開發(fā)的過程中都不可避免的要進(jìn)行方案的調(diào)試,除了模擬調(diào)試我們還必須進(jìn)行真機(jī)調(diào)試才能確保功能的正常,通常我們采用的調(diào)試方法分為兩種:第一種是使用硬件邏輯分析儀,第二種是采用嵌入邏輯分析IP。

2018-03-13 13:54:41 6885

6885

6885

6885

學(xué)會Linux內(nèi)核調(diào)試方法!

內(nèi)核開發(fā)比用戶空間開發(fā)更難的一個因素就是內(nèi)核調(diào)試艱難。內(nèi)核錯誤往往會導(dǎo)致系統(tǒng)宕機(jī),很難保留出錯時(shí)的現(xiàn)場。調(diào)試內(nèi)核的關(guān)鍵在于你的對內(nèi)核的深刻理解。

2019-05-07 11:01:26 2154

2154

2154

2154數(shù)字設(shè)計(jì)FPGA應(yīng)用:時(shí)序邏輯電路FPGA的實(shí)現(xiàn)

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-05 07:08:00 2539

2539

2539

2539

數(shù)字設(shè)計(jì)FPGA應(yīng)用:FPGA的基本邏輯結(jié)構(gòu)

本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-03 07:04:00 2191

2191

2191

2191

邏輯分析儀的工作原理和結(jié)構(gòu)

邏輯分析儀是常用的電子儀器之要應(yīng)用于做數(shù)字電路測試A調(diào)試,CPU/DSP調(diào)試,數(shù)字IQF分析,無線通信需達(dá)接收機(jī)測試等場合。邏輯分析儀由模塊和計(jì)算機(jī)組成(當(dāng)然還有探頭),模塊負(fù)責(zé)數(shù)據(jù)的觸發(fā),采集和存儲的工作,計(jì)算機(jī)負(fù)責(zé)后端的數(shù)據(jù)顯示,數(shù)據(jù)處理和分析等工作。

2020-07-10 10:29:00 4

4

4

4采用內(nèi)部或者嵌入式邏輯分析儀推動FPGA調(diào)試技術(shù)改變

進(jìn)行硬件設(shè)計(jì)的功能調(diào)試時(shí),FPGA的再編程能力是關(guān)鍵的優(yōu)點(diǎn)。CPLD和FPGA早期使用時(shí),如果發(fā)現(xiàn)設(shè)計(jì)不能正常工作,工程師就使用“調(diào)試鉤”的方法。先將要觀察的FPGA內(nèi)部信號引到引腳,然后用外部的邏輯分析儀捕獲數(shù)據(jù)。

2020-09-14 15:08:00 527

527

527

527

FPGA設(shè)計(jì)與調(diào)試教程說明

FPGA概述FPGA調(diào)試介紹調(diào)試挑戰(zhàn)設(shè)計(jì)流程概述■FPGA調(diào)試方法概述嵌入式邏輯分析儀外部測試設(shè)備■使用 FPGAVIEW改善外部測試設(shè)備方法■FPGA中高速O的信號完整性測試和分析

2020-09-22 17:43:21 9

9

9

9FPGA開發(fā)在線調(diào)試和配置過程

在線調(diào)試也稱作板級調(diào)試,它是將工程下載到FPGA芯片上后分析代碼運(yùn)行的情況。

2020-11-01 10:00:49 3947

3947

3947

3947

嵌入式LINUX系統(tǒng)內(nèi)核和內(nèi)核模塊調(diào)試

嵌入式LINUX系統(tǒng)內(nèi)核和內(nèi)核模塊調(diào)試(嵌入式開發(fā)和硬件開發(fā))-嵌入式LINUX系統(tǒng)內(nèi)核和內(nèi)核模塊調(diào)試? ? ? ? ? ? ? ? ?

2021-07-30 13:55:21 9

9

9

9邏輯調(diào)試器link-logic

link_logic帶link調(diào)試功能、串口調(diào)試、邏輯分析儀與一身的數(shù)字調(diào)試器項(xiàng)目地址:GitHub個人博客:全球:fzxhub.com 中國:fzxhub.gitee.io簡介本項(xiàng)目是一個link

2022-01-12 20:21:00 9

9

9

9通過片上儀器和邏輯分析輕松進(jìn)行FPGA和ASIC調(diào)試

隨著復(fù)雜性的增加和對探測點(diǎn)的訪問受限,ASIC 和 FPGA 驗(yàn)證和調(diào)試變得乏味且耗時(shí)。隨著越來越多的功能集成到每個芯片中,對探測點(diǎn)的物理訪問變得不可能。接下來的挑戰(zhàn)是整合足夠的片上觀察點(diǎn),不僅可以處理預(yù)期的調(diào)試場景,還可以處理意外的調(diào)試場景。

2022-07-09 06:54:00 321

321

321

321

FPGA調(diào)試中LVDS信號線間串?dāng)_問題

在FPGA調(diào)試過程中,除了邏輯代碼本身的質(zhì)量之外,FPGA板子上PCB走線、接插件質(zhì)量等因素的影響也非常重要。

2022-10-28 16:40:03 2217

2217

2217

2217Linux內(nèi)核調(diào)試的方式以及工具匯總(上)

內(nèi)核總是那么捉摸不透, 內(nèi)核也會犯錯, 但是調(diào)試卻不能像用戶空間程序那樣, 為此內(nèi)核開發(fā)者為我們提供了一系列的工具和系統(tǒng)來支持內(nèi)核的調(diào)試.

內(nèi)核的調(diào)試, 其本質(zhì)是內(nèi)核空間與用戶空間的數(shù)據(jù)交換, 內(nèi)核開發(fā)者們提供了多樣的形式來完成這一功能.

2023-05-12 14:58:41 636

636

636

636

Linux內(nèi)核調(diào)試的方式以及工具匯總(下)

內(nèi)核總是那么捉摸不透, 內(nèi)核也會犯錯, 但是調(diào)試卻不能像用戶空間程序那樣, 為此內(nèi)核開發(fā)者為我們提供了一系列的工具和系統(tǒng)來支持內(nèi)核的調(diào)試.

內(nèi)核的調(diào)試, 其本質(zhì)是內(nèi)核空間與用戶空間的數(shù)據(jù)交換, 內(nèi)核開發(fā)者們提供了多樣的形式來完成這一功能.

2023-05-12 14:59:24 878

878

878

878

國微思爾芯多FPGA聯(lián)合深度調(diào)試新思路

剖析》分析了用戶在進(jìn)行大規(guī)模原型驗(yàn)證過程中的多FPGA聯(lián)合調(diào)試難題,并介紹了一種新型FPGA原型驗(yàn)證深度跟蹤調(diào)試解決方案,用于幫助客戶在SoC開發(fā)過程中解決調(diào)試問

2022-06-16 10:16:48 627

627

627

627

usb邏輯分析儀怎么用

usb邏輯分析儀怎么用 USB邏輯分析儀是一種用于分析USB設(shè)備和主機(jī)之間通信的工具。它能夠監(jiān)視USB的數(shù)據(jù)傳輸,捕獲和解碼USB的通信信號,對USB接口進(jìn)行調(diào)試,并以便捷的方式檢測出USB環(huán)境

2023-09-19 16:03:47 1221

1221

1221

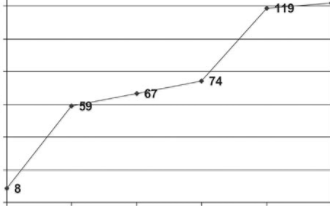

1221如何用內(nèi)部邏輯分析儀調(diào)試FPGA?

的FPGA內(nèi)部信號引到引腳,然后用外部的邏輯分析儀捕獲數(shù)據(jù)。然而當(dāng)設(shè)計(jì)的復(fù)雜程度增加時(shí),這個方法就不再適合了,其中有幾個原因。第一是由于FPGA的功能增加了,而器件的引腳數(shù)目卻緩慢地增長。因此,可用邏輯對I/O的比率減小了,參見圖1。此外,設(shè)計(jì)很復(fù)雜時(shí)

2023-12-20 13:35:01 147

147

147

147

電子發(fā)燒友App

電子發(fā)燒友App

評論