完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

電子發燒友網技術文庫為您提供最新技術文章,最實用的電子技術文章,是您了解電子技術動態的最佳平臺。

VHDL和verilog各有優點,選擇一個,建議選擇verilog。熟練使用設計軟件,知道怎樣編譯、仿真、下載等過程。起步階段不希望報一些培訓班,除非你有錢,或者運氣好,碰到一個水平高、又想把自己的經驗和別人共享的培訓老師,不然的話,培訓完后總會感覺自己是一個冤大頭。入門階段可以在利用網絡資源完成。...

當電源定序不當時,就有可能發生閉鎖失靈或電流消耗過大的現象。如果兩個電源加到芯核接口和I/O接口上的電位不同時,就會出現觸發閉鎖。定序要求不相同的FPGA和其他元件會使電源系統設計更加復雜化。...

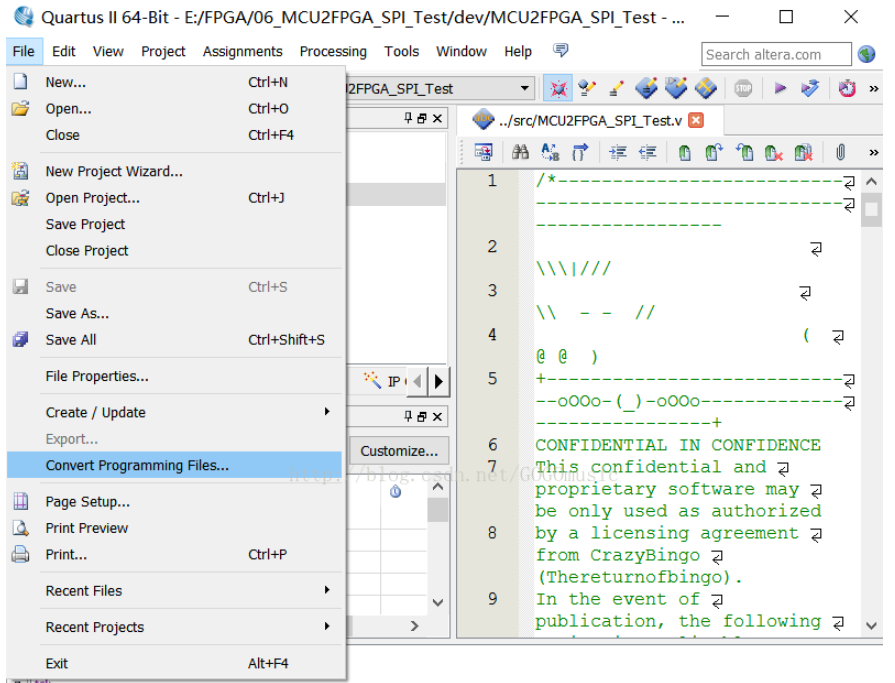

在Configuration d e vi ce 下拉列表框中根據實際設計選擇被編程目標器件,對于EP3C8 選擇EPCS16 。這個型號根據板子上的型號選擇。...

本文主要介紹的是FPGA的片上資源使用情況,分別是從組合邏輯及時序邏輯來詳細的分析。...

首先,你必須有學習單片機的熱情,不是說今天去圖書館看了一個下午關于單片機的書,而明天玩上半天,后天就不知道那個本書在講什 么東西了。第二,既然你想學好單片機,你必須得舍得花錢,如果不買些芯片回來自己動手焊焊拆拆的(但是在后期會介紹給大家一個很好用的硬件。...

什么是單片機燒寫軟件? 什么是單片機燒寫軟件? 簡單點說,就是把你寫好代碼(C或者是匯編)專程的機器語言通過一定的方式下載到單片機中。稱為燒寫。 燒寫軟件很多,方式也很多,主要看你的單片機型號....

你想用 Linux,但希望它不要影響電機驅動的確定性和響應時間;你想從驅動器中高速采集電流、電壓和角速度等數據進行分析,以便集成到工業4.0或其他工業物聯網系統中....

基于數字特征的識別算法其核心是通過對數字的形狀以及結構等幾何特征進行分析與統計,通過對數字特征的識別從而達到對圖像中數字的識別。...

說到模塊化編程,以前曾看過不少大蝦的例子,他們的源文件和輸出下載文件是放在項目文件夾下地不同文件夾中,如源文件放在src文件夾中,輸出*.hex放在output文件夾中,這樣整個項目就更顯得清晰明了。...

像素是由比特組成的數字。例如,在256級灰度圖像中,每個像素的灰度是由8比特(也就是1個字節)組成。一幅8比特圖像可以認為由8個1比特平面組成,如圖1所示,其中平面1包含圖像中所有像素的最低階比特,而平面8包含圖像中所有像素的最高階比特。...

我們使用3x3模板進行邊界提取,所以當3x3九個點都是‘1’的時候,輸出為‘1’,當九個點都是‘0’的時候,輸出為‘1’,其他情況輸出均為‘0’。...

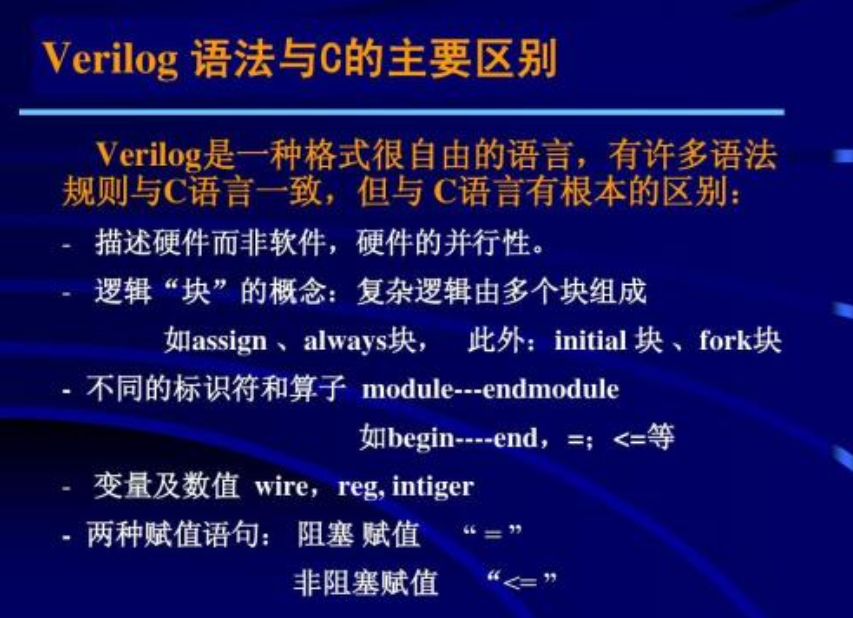

學習verilog最重要的不是語法,“因為10%的語法就能完成90%的工作”,verilog語言常用語言就是always@(),if~else,case,assign這幾個了。...

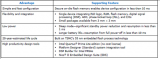

Intel公司的MAX 10 FPGA系列采用TSMC 55nm NOR閃存技術,容量從2K到50K 邏輯單元(LE),采用單個或雙核電源電壓和小尺寸3x3mm和高I/O引腳數封裝;器件具有全特性FPGA功能,支持Nios II軟核嵌入處理器,數字信號處理(DSP)區塊以及軟DDR3存儲器控制器,內...

在二值圖像的腐蝕算法過程中我們使用二值圖像3x3圖像矩陣,由圖2可知,當九個格子中不全為‘0’或者‘1’時,經過腐蝕算法后九個格子的值最終都會變成‘1’;如果九個全是‘1’或者‘0’時,那么最終的結果九個全是‘1’或者‘0’。...

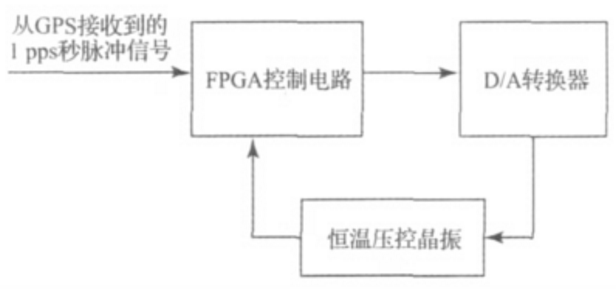

本文主要介紹了基于FPGA的壓控晶振同步頻率控制系統的研究與設計。利用GPS提供的1pps秒脈沖信號,為解決上述問題,在FPGA的基礎上利用干擾秒脈沖信號消除和偏差頻率平均運算等方法,減少外圍電路,既消減了GPS時鐘信號的隨機干擾誤差,又消除了本地晶振時鐘信號的累計誤差,從而控制本地壓控晶振輸出頻率...

這一次給大家分享的內容主要涉及Xilinx FPGA內的CLBs,SelectIO和Clocking資源,適合對FPGA設計有時序要求,卻還沒有足夠了解的朋友。 ...

以下列出了學習 Python 時犯的三種錯誤: 1.可變數據類型作為函數定義中的默認參數 2.可變數據類型作為類變量 3. 可變的分配錯誤...

Spartan6系列FPGA常見的配置模式有5種,該5種模式可分為3大類,1. JTAG模式(可歸為從模式);2. 主模式;3. 從模式。主模式又劃分為master serial模式、master parallel模式,從模式分為slave serial模式、slave parallel模式兩種。...