完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > vivado

Vivado設(shè)計(jì)套件,是FPGA廠商賽靈思公司2012年發(fā)布的集成設(shè)計(jì)環(huán)境。包括高度集成的設(shè)計(jì)環(huán)境和新一代從系統(tǒng)到IC級的工具,這些均建立在共享的可擴(kuò)展數(shù)據(jù)模型和通用調(diào)試環(huán)境基礎(chǔ)上。

文章:618個 瀏覽:68647次 帖子:936個

隨著FPGA規(guī)模的增大,設(shè)計(jì)復(fù)雜度的增加,Vivado編譯時間成為一個不可回避的話題。尤其是一些基于SSI芯片的設(shè)計(jì),如VU9P/VU13P/VU19P...

Xilinx的新一代設(shè)計(jì)套件Vivado相比上一代產(chǎn)品ISE,在運(yùn)行速度、算法優(yōu)化和功能整合等很多方面都有了顯著地改進(jìn)。但是對初學(xué)者來說,新的約束語言X...

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數(shù)學(xué)運(yùn)算(乘法器、除法器、浮點(diǎn)運(yùn)算器等)、信號處理(FFT、DFT、DDS等)。I...

直接在modelsim軟件內(nèi)執(zhí)行.do文件進(jìn)行仿真,不通過vivado調(diào)用modelsim,vivado僅用于生成IP核。

2023-12-04 標(biāo)簽:XilinxVivadoMODELSIM仿真 2178 0

Vivado可以導(dǎo)出腳本,保存創(chuàng)建工程的相關(guān)命令和配置,并可以在需要的時候使用腳本重建Vivado工程。腳本通常只有KB級別大小,遠(yuǎn)遠(yuǎn)小于工程打包文件的...

Vivado的“Placement Exploration”配方案例分析

盡管 Vivado 不支持 “placement cost tale”的功能,InTime 卻有一個相似功能叫做“Placement Explorati...

FPGA在深度學(xué)習(xí)領(lǐng)域有哪些優(yōu)勢?

FPGA(Field-Programmable Gate Array)是一種靈活的可編程硬件設(shè)備,它在深度學(xué)習(xí)應(yīng)用領(lǐng)域中具有許多優(yōu)勢。

每次我們更改硬件時,我們都需要告訴 HLS 將其導(dǎo)出為硬件描述語言并生成 Vivado 需要的所有各種源數(shù)據(jù)。

2022-09-22 標(biāo)簽:FPGA設(shè)計(jì)VivadoHLS 2098 0

基于Digilent basys 3開發(fā)板的FPGA示波器設(shè)計(jì)

首先,AD模塊對模擬信號進(jìn)行采樣,觸發(fā)電路根據(jù)采樣信號判斷觸發(fā)條件(例如:上升沿觸發(fā))。滿足觸發(fā)條件后,連續(xù)采樣一定數(shù)量的點(diǎn)(本系統(tǒng)中為640個點(diǎn)),存...

在Vivado中構(gòu)建AMD Versal可擴(kuò)展嵌入式平臺示例設(shè)計(jì)流程

為了應(yīng)對無線波束形成、大規(guī)模計(jì)算和機(jī)器學(xué)習(xí)推斷等新一代應(yīng)用需求的非線性增長,AMD 開發(fā)了一項(xiàng)全新的創(chuàng)新處理技術(shù) AI 引擎,片內(nèi)集成該AI Engin...

2024-04-09 標(biāo)簽:Linux系統(tǒng)機(jī)器學(xué)習(xí)數(shù)據(jù)交互 2087 0

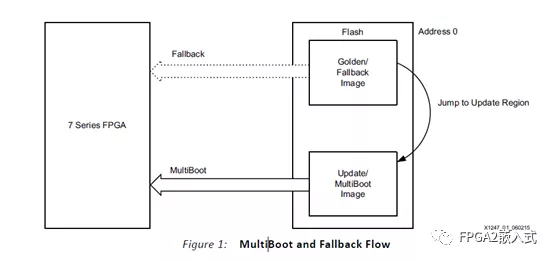

7 eries FPGAs SPI MultiBoot實(shí)現(xiàn)方式

7 Series FPGAs MultiBoot功能指讓FPGA從2個或者多個BIT文件中加載一個BIT文件運(yùn)行程序,所以它的2個主要應(yīng)用如下: 1. ...

Vivado設(shè)計(jì)套件終于震撼登場,賽靈思采用先進(jìn)的 EDA技術(shù)和方法,提供了全新的工具套件,可顯著提高設(shè)計(jì)生產(chǎn)力和設(shè)計(jì)結(jié)果質(zhì)量,使設(shè)計(jì)者更好、更快地創(chuàng)建...

如何用Python實(shí)現(xiàn)Vivado和ModelSim仿真自動化?

我們在Windows系統(tǒng)下使用Vivado的默認(rèn)設(shè)置調(diào)用第三方仿真器比如ModelSim進(jìn)行仿真時,一開始仿真軟件都會默認(rèn)在波形界面中加載testben...

Vivado IDE 中的Timing Constraints窗口介紹

隨著設(shè)計(jì)復(fù)雜度和調(diào)用 IP 豐富度的增加,在調(diào)試時序約束的過程中,用戶常常會對除了頂層約束外所涉及的繁雜的時序約束感到困惑而無從下手。舉個例子,用戶在 ...

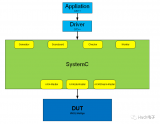

如何使用SystemC做RTL和C/C++的聯(lián)合仿真呢?

當(dāng)FPGA開發(fā)者需要做RTL和C/C++聯(lián)合仿真的時候,一些常用的方法包括使用MicroBlaze軟核,或者使用QEMU仿真ZYNQ的PS部分。

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |