完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > vivado

Vivado設計套件,是FPGA廠商賽靈思公司2012年發布的集成設計環境。包括高度集成的設計環境和新一代從系統到IC級的工具,這些均建立在共享的可擴展數據模型和通用調試環境基礎上。

文章:612個 瀏覽:68076次 帖子:935個

在這篇新博文中,我們來聊一聊如何將 AXI VIP 添加到 Vivado 工程中,并對 AXI4-Lite 接口進行仿真。隨后,我們將在仿真波形窗口中講...

使用像ZYNQ這樣的SOC架構的FPGA,開發難度比較大的,能熟練開發FPGA已經很難了,ZYNQ需要硬件邏輯開發,然后還要開發ARM。

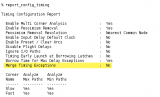

在FPGA設計里,設計仿真完成RTL代碼設計后便是交給設計套件進行綜合及布局布線。在綜合過程里,Vivado里提供的參數選項有點兒多,今天閑暇抽空梳理下。

波形(waveform)以列表的形式給出,表中包含上升沿和下降沿在周期中的絕對時間,以ns為單位;第一個上升沿對應于第一個值,第一個下降沿對應第二個值;...

在Vivado中創建基于IP集成器(IP Integrator)的設計

Zynq UltraScale+ RFSoC 是業界首款單芯片自適應無線電平臺,在一款芯片內集成射頻直采數據轉換器、單芯片軟決策前向糾錯核(SD-FEC...

有時我們需要在設計網表的基礎上微調一下邏輯,這樣可以無需修改代碼,也無需重新做綜合,在設計調試中可以節省時間同時維持其他邏輯無任何改動。

在FPGA實際的開發中,官方提供的IP并不是適用于所有的情況,需要根據實際修改,或者是在自己設計的IP時,需要再次調用時,我們可以將之前的設計封裝成自定...

數字設計中,“時鐘”表示在寄存器間可靠地傳輸數據所需的參考時間。Vivado的時序引擎通過時鐘特征來計算時序路徑需求,通過計算裕量(Slack)的方法報...

等該例子工程跑完綜合,實現,并產生bit文件之后,請將PDI文件加載到你的VPK120里面:

時序約束的目的就是告訴工具當前的時序狀態,以讓工具盡量優化時序并給出詳細的分析報告。一般在行為仿真后、綜合前即創建基本的時序約束。Vivado使用SDC...

很對人在使用Vivado時喜歡使用多個約束文件對整個工程進行約束,同時Vivado允許設計者使用一個或多個約束文件。雖然使用一個約束文件對于一個完整的編...

如何追溯同一時鐘域內partial false path的來源

隨著設計復雜度和調用IP豐富度的增加,在調試時序約束的過程中,用戶常常會對除了自己設定的約束外所涉及的繁雜的時序約束感到困惑而無從下手。舉個例子,我的X...

在Vitis中把Settings信息傳遞到底層的Vivado

本篇文章來自賽靈思高級工具產品應用工程師 Hong Han. 本篇博文將繼續介紹在Vitis中把Settings信息傳遞到底層的Vivado. 對于Vi...

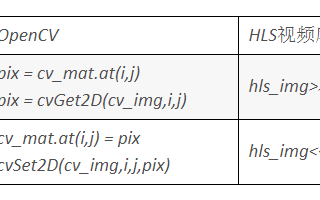

Vivado設計流程分析 Vivado HLS實現OpenCV的開發流程

作者:Harvest Guo來源:Xilinx DSP Specilist 本文通過對OpenCV中圖像類型和函數處理方法的介紹,通過設計實例描述在vi...

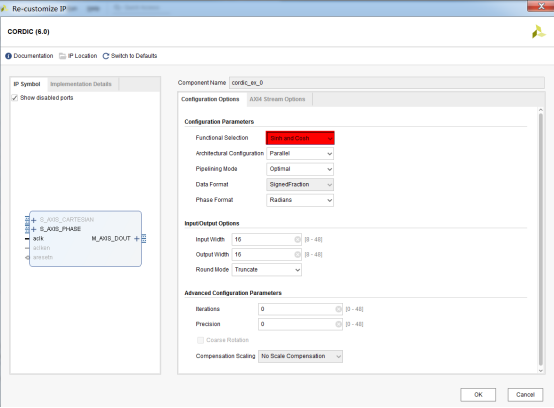

Vivado中xilinx_courdic IP核的使用方法

由于Verilog/Vhdl沒有計算exp指數函數的庫函數,所以在開發過程中可利用cordic IP核做exp函數即e^x值;但前提要保證輸入范圍在(-...

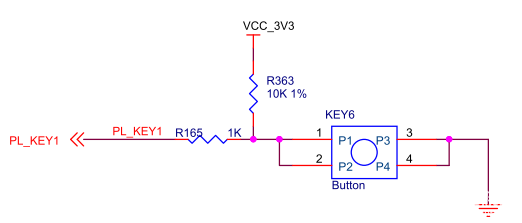

【ZYNQ Ultrascale+ MPSOC FPGA教程】第九章Vivado下按鍵實驗

按鍵是FPGA設計當中最常用也是最簡單的外設,本章通過按鍵檢測實驗,檢測開發板的按鍵功能是否正常,并了解硬件描述語言和FPGA的具體關系,學習Vivad...

【ZYNQ Ultrascale+ MPSOC FPGA教程】第五章Vivado下PLL實驗

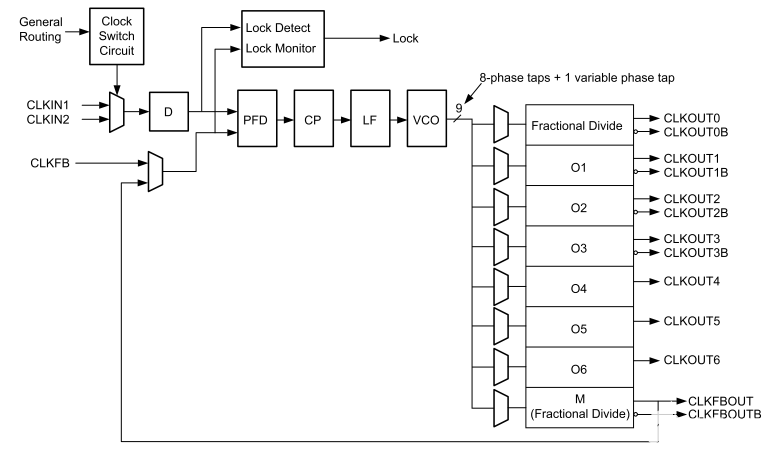

PLL(phase-locked loop),即鎖相環。是FPGA中的重要資源。由于一個復雜的FPGA系統往往需要多個不同頻率,相位的時鐘信號。所以,一...

Vivado提出了UFDM(UltraFast Design Methodology)設計方法學,其核心思想是盡可能在設計初期發現潛在問題并解決。畢竟,...

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |