完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > system

system是一個(gè)C語言和C++下的函數(shù)。windows操作系統(tǒng)下system () 函數(shù)詳解主要是在C語言中的應(yīng)用,system函數(shù)需加頭文件《stdlib.h》后方可調(diào)用。

文章:117個(gè) 瀏覽:37562次 帖子:105個(gè)

如何利用SystemVerilog仿真生成隨機(jī)數(shù)

采用SystemVerilog進(jìn)行仿真則更容易生成隨機(jī)數(shù),而且對(duì)隨機(jī)數(shù)具有更強(qiáng)的可控性。對(duì)于隨機(jī)變量,在SystemVerilog中可通過rand或ra...

利用模塊化建模方法實(shí)現(xiàn)基于System Generator的控制器導(dǎo)出并多軟硬件仿真驗(yàn)證

利用System Generator軟件平臺(tái),實(shí)現(xiàn)基于模塊化建模方法的變換器建模,并簡(jiǎn)化語言編寫控制系統(tǒng)的復(fù)雜過程。研究了從MATLAB-Xilinx環(huán)...

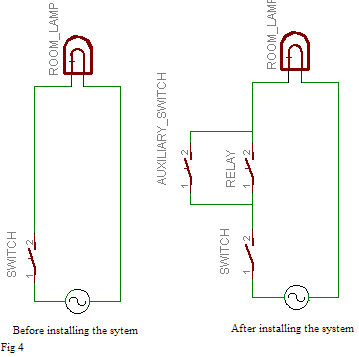

燈光控制系統(tǒng)電路,ht Control System

燈光控制系統(tǒng)電路,ht Control System It is easy to install a couple of infrared emitt...

SystemVerilog是一種 硬件描述和驗(yàn)證語言 (HDVL),它 基于IEEE1364-2001 Verilog硬件描述語言(HDL),并對(duì)其進(jìn)行...

基于System Generator的Rife算法設(shè)計(jì)實(shí)現(xiàn)與仿真分析

在FPGA平臺(tái)上應(yīng)用System Generator工具實(shí)現(xiàn)了高精度頻率估計(jì)Rife算法。不同于傳統(tǒng)的基于HDL代碼和IP核的設(shè)計(jì)方法,采用System...

作者:limanjihe ?https://blog.csdn.net/limanjihe/article/details/83005713 Syste...

基于System Generator實(shí)現(xiàn)高速盲均衡器設(shè)計(jì)并闡述了MCMA算法的實(shí)現(xiàn)過程

基于System Generator軟件,在xc7z020-1clg484芯片上設(shè)計(jì)了一種高速盲均衡器。該盲均衡器由延遲模塊、濾波模塊、誤差計(jì)算模塊和...

Axiomtek宣布推出AIE100-903-FL-NX AI Edge System

NVIDIA Jetson為AIE100-903-FL-NX AI邊緣系統(tǒng)提供動(dòng)力,該系統(tǒng)使用帶有六核處理器的Xavier NX模塊和帶有Volta圖形...

2021-01-27 標(biāo)簽:處理器操作系統(tǒng)System 2173 0

SystemVerilog既是一種硬件設(shè)計(jì)語言,也是一種硬件驗(yàn)證語言。IEEE SystemVerilog官方標(biāo)準(zhǔn)沒有區(qū)分這兩個(gè)目標(biāo),也沒有指定完整Sy...

了解決這個(gè)復(fù)雜的問題,設(shè)計(jì)了這個(gè)庫,它可以幫助您簡(jiǎn)化設(shè)計(jì)流程。使用一些簡(jiǎn)單的 API 可以輕松地在測(cè)試臺(tái)中讀取和寫入標(biāo)準(zhǔn)位圖文件 (.BMP)。并且,使...

Sequencing with the MAX16046 S

Sequencing with the MAX16046 System-Management IC Abstract: Complex device...

深入了解賽靈思System Generator中的時(shí)間參數(shù)

深入了解賽靈思System Generator中的時(shí)間參數(shù) 基于模型的設(shè)計(jì)(MBD)因其在縮小實(shí)時(shí)系統(tǒng)抽象的數(shù)學(xué)建模和物理實(shí)現(xiàn)之間差距方面的光明前景...

文本整數(shù)值是一個(gè)整數(shù),沒有小數(shù)點(diǎn)。(IEEE 1800 SystemVerilog標(biāo)準(zhǔn)使用術(shù)語“整數(shù)文本integer literal”而不是“文本整數(shù)...

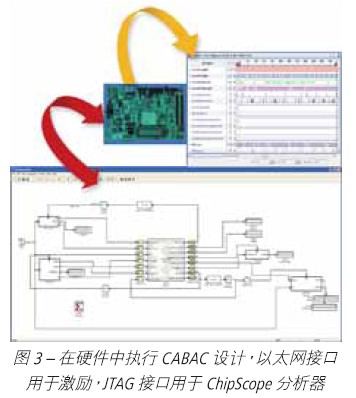

HDL設(shè)計(jì)和驗(yàn)證與System Generator相結(jié)合

HDL設(shè)計(jì)和驗(yàn)證與System Generator相結(jié)合 Xilinx®SystemGeneratoRForDSP是用來協(xié)助系統(tǒng)設(shè)計(jì)的MATL...

IAR Systems發(fā)布 IAR Embedded Wor

IAR Systems發(fā)布 IAR Embedded Workbench for ARM新版本 IAR Systems發(fā)布IAR Embedded ...

ALVA Systems 攜手合作伙伴加快構(gòu)建產(chǎn)業(yè)創(chuàng)新體系

10 月,羅克韋爾自動(dòng)化數(shù)智化賦能研討會(huì)在成都舉辦。 ALVA Systems 攜手合作伙伴成都?xì)W嘉美(E&A)出席本次活動(dòng),進(jìn)行議題分享和創(chuàng)新 AR ...

IAR Systems全球推廣VLP 計(jì)劃 嵌入式系統(tǒng)軟件工具供應(yīng)商IAR Systems正式宣布在全球范圍內(nèi)推廣推廣VLP (Volume Lice...

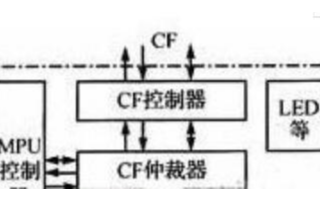

采用DSP的System ACE對(duì)CF卡進(jìn)行數(shù)據(jù)存儲(chǔ)管理

目前,對(duì)圖像處理系統(tǒng)的速度和精度要求越來越高,采樣的數(shù)據(jù)量也越來越大。

In-Circuit Programming for the

In-Circuit Programming for the MAX16046–MAX16049 EEPROM-Programmable System ...

2008-11-15 標(biāo)簽:System 1215 0

System推出便攜型數(shù)字式輻射測(cè)量?jī)xGC-S1

日本System Talks將上市便攜型數(shù)字式輻射測(cè)量?jī)x“GC-S1”。該產(chǎn)品因采用最新的微處理器

2011-04-01 標(biāo)簽:System輻射測(cè)量?jī)xGC-S1 1189 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |