完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > 靜態(tài)時(shí)序分析

文章:19個(gè) 瀏覽:9659次 帖子:4個(gè)

在芯片設(shè)計(jì)中,前仿真和后仿真都是非常重要的環(huán)節(jié),但它們?cè)诠δ芎湍康纳洗嬖诿黠@的區(qū)別。本文將詳細(xì)介紹前仿真和后仿真的區(qū)別,以及它們?cè)谛酒O(shè)計(jì)中的應(yīng)用和重要...

數(shù)字IC前端設(shè)計(jì)+后端設(shè)計(jì)流程實(shí)現(xiàn)

RTL 設(shè)計(jì)** :芯片功能設(shè)計(jì)。硬件描述語(yǔ)言如 Verilog、VHDL、SystemVerilog。

2023-11-08 標(biāo)簽:緩沖器IC設(shè)計(jì)EDA工具 5886 0

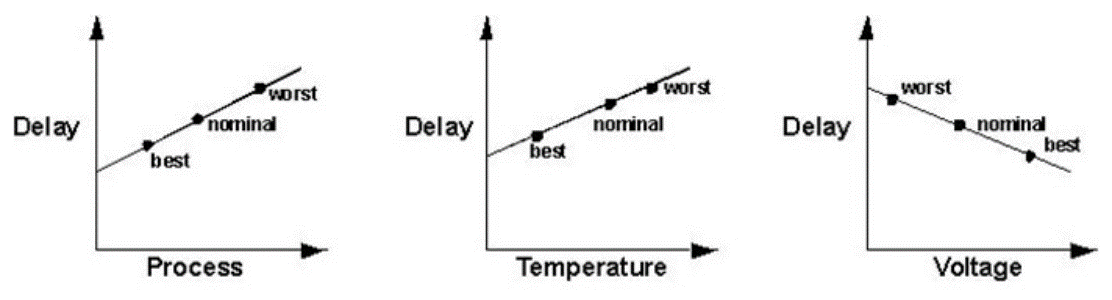

即便是同一種FF,在同一個(gè)芯片上不同操作條件下的延時(shí)都不盡相同,我們稱(chēng)這種現(xiàn)象為OCV(on-chip variation)。OCV表示的是芯片內(nèi)部的時(shí)...

2019-07-25 標(biāo)簽:數(shù)字電路靜態(tài)時(shí)序分析 4994 0

仿真設(shè)置中修改脈沖拒絕和錯(cuò)誤限制來(lái)防止脈沖濾波

現(xiàn)在假設(shè)設(shè)計(jì)采用的頻率是 200MHz。對(duì)應(yīng)的周期就是 5ns,那么一半就是 2.5ns。在仿真中時(shí)鐘每隔 2.5ns 變化一次,也就是時(shí)鐘脈沖的寬度是...

2019-07-30 標(biāo)簽:脈沖靜態(tài)時(shí)序分析 4902 0

同步時(shí)序設(shè)計(jì)靜態(tài)時(shí)序分析等f(wàn)pga設(shè)計(jì)技巧剖析

從大學(xué)時(shí)代第一次接觸FPGA至今已有10多年的時(shí)間,至今記得當(dāng)初第一次在EDA實(shí)驗(yàn)平臺(tái)上完成數(shù)字秒表、搶答器

2017-11-06 標(biāo)簽:FPGA設(shè)計(jì)靜態(tài)時(shí)序分析同步時(shí)序設(shè)計(jì) 4666 0

本文描述的跨時(shí)鐘錯(cuò)誤在特定場(chǎng)景下,有些是允許的,甚至有些是正常設(shè)計(jì)。因此IC設(shè)計(jì)者想要確認(rèn)跨時(shí)鐘錯(cuò)誤需要分析應(yīng)用場(chǎng)景。

2023-07-24 標(biāo)簽:寄存器靜態(tài)時(shí)序分析時(shí)鐘域 4284 0

靜態(tài)時(shí)序分析是什么 靜態(tài)時(shí)序分析可以檢查什么

傳統(tǒng)的電路設(shè)計(jì)分析方法是僅僅采用動(dòng)態(tài)仿真的方法來(lái)驗(yàn)證設(shè)計(jì)的正確性。隨著集成電路的發(fā)展,這一驗(yàn)證方法就成為了大規(guī)模復(fù)雜的設(shè)計(jì)驗(yàn)證時(shí)的瓶頸。

2023-07-20 標(biāo)簽:觸發(fā)器靜態(tài)時(shí)序分析時(shí)鐘信號(hào) 3925 0

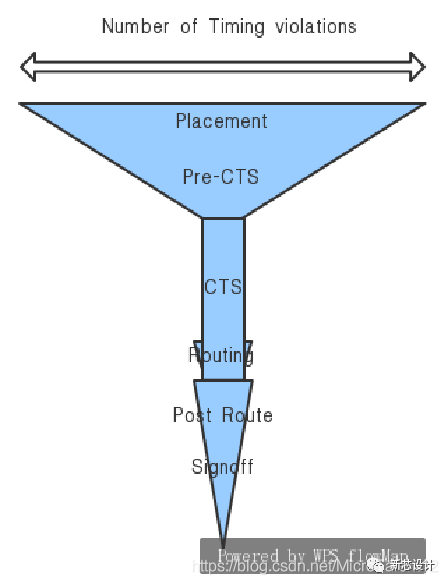

靜態(tài)時(shí)序分析簡(jiǎn)稱(chēng)STA,它是一種窮盡的分析方法,它按照同步電路設(shè)計(jì)的要求,根據(jù)電路網(wǎng)表的拓?fù)浣Y(jié)構(gòu),計(jì)算并檢查電路中每一個(gè)DFF(觸發(fā)器)的建立和保持時(shí)間...

2022-09-27 標(biāo)簽:fpgaSTA靜態(tài)時(shí)序分析 3342 0

詳細(xì)介紹數(shù)字IC設(shè)計(jì)的全流程內(nèi)容

一顆芯片是如何造出來(lái)的,相信對(duì)行業(yè)稍有涉獵的同學(xué),都能簡(jiǎn)單作答:即先通過(guò)fabless進(jìn)行設(shè)計(jì),再交由Foundry進(jìn)行制造,最后由封測(cè)廠交出。

2023-10-09 標(biāo)簽:寄存器IC設(shè)計(jì)RTL 2890 0

FPGA那些事兒--TimeQuest靜態(tài)時(shí)序分析REV7.0立即下載

類(lèi)別:FPGA/ASIC 2014-03-07 標(biāo)簽:FPGA靜態(tài)時(shí)序分析FPGA教程 1776 0

靜態(tài)時(shí)序分析基礎(chǔ)知識(shí)立即下載

類(lèi)別:課件下載 2011-05-11 標(biāo)簽:靜態(tài)時(shí)序分析 1303 0

華為靜態(tài)時(shí)序分析與邏輯設(shè)計(jì)立即下載

類(lèi)別:FPGA/ASIC 2016-09-01 標(biāo)簽:邏輯設(shè)計(jì)靜態(tài)時(shí)序分析 1246 1

靜態(tài)時(shí)序分析在IC設(shè)計(jì)中的應(yīng)用立即下載

類(lèi)別:半導(dǎo)體技術(shù)論文 2011-12-20 標(biāo)簽:IC設(shè)計(jì)靜態(tài)時(shí)序分析 1162 2

靜態(tài)時(shí)序分析(Static Timing Analysis)基礎(chǔ)及應(yīng)用立即下載

類(lèi)別:模擬數(shù)字 2011-05-27 標(biāo)簽:靜態(tài)時(shí)序分析 1008 1

靜態(tài)時(shí)序分析與邏輯(華為內(nèi)部培訓(xùn)資料)立即下載

類(lèi)別:可編程邏輯 2010-07-09 標(biāo)簽:靜態(tài)時(shí)序分析 968 4

類(lèi)別:電子資料 2021-03-17 標(biāo)簽:寄存器電源技術(shù)靜態(tài)時(shí)序分析 458 0

run_cmax > ./starrc_cmax.logs 2>&1中的 2>&1是啥意思?

2023-07-30 標(biāo)簽:SoC設(shè)計(jì)DRCSTA 2226 0

萊迪思全新版本Radiant設(shè)計(jì)軟件進(jìn)一步擴(kuò)展了功能安全和可靠性

萊迪思Radiant集成了最新版本Synopsys Synplify和三重模塊化冗余(TMR),可創(chuàng)建先進(jìn)的設(shè)計(jì)自動(dòng)化流程解決方案

2024-04-03 標(biāo)簽:FPGATMR靜態(tài)時(shí)序分析 815 0

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專(zhuān)題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹(shù)莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |