資料介紹

描述

什么是仲裁員?

仲裁器是硬件設(shè)計(jì)中非常常用的塊。

我想我可以在家里找到仲裁者的最好例子。當(dāng)我的兩個(gè)孩子十幾歲時(shí),我只有一輛車。在周五和周六晚上,通常會(huì)因?yàn)檎l可以使用汽車而發(fā)生沖突。通常,由我來決定(仲裁者)誰得到了這輛車。這不是一件容易的事。(我仍然只有一輛車,正好我的孩子都不是十幾歲了,贊美主,他們有自己的車)。

硬件板沒有什么不同。至少在兩種情況下,多個(gè)用戶“需要”共享(且有價(jià)值且昂貴)的資源:

- 公共內(nèi)存:在處理器和 FPGA 之間共享快速內(nèi)存(即 DDR)的電路板是很常見的。顯然,記憶不能同時(shí)回答兩個(gè)高手。處理器和 FPGA 向仲裁器請求訪問內(nèi)存的權(quán)限。即使它以非常高的速度同時(shí)完成,對于我們的感知,實(shí)際上,F(xiàn)PGA 和處理器必須輪流擁有內(nèi)存。注意:這只是一個(gè)簡單的示例,因?yàn)檫€有許多其他應(yīng)用程序甚至超過兩個(gè)“智能”設(shè)備(處理器、DSP、GPU、FPGA、ASIC)輪流訪問公共內(nèi)存。

- 公共總線:很多時(shí)候多個(gè)主機(jī)(和從機(jī))通過公共總線進(jìn)行通信。從電氣角度來說,總線非常簡單。它只不過是一組銅連接或電線(有時(shí)帶有總線驅(qū)動(dòng)器)。但是總線所有權(quán)很重要,因?yàn)閮蓚€(gè)主機(jī)不可能同時(shí)擁有總線(多主機(jī)總線的示例:I2C、PCI)。如果兩個(gè)主機(jī)試圖同時(shí)“交談”,就會(huì)發(fā)生沖突,總線上的數(shù)據(jù)就會(huì)被破壞。

仲裁者是硬件的一部分,它決定誰可以在任何給定時(shí)間使用公共的、有價(jià)值的資源。然而,與足球仲裁器不同的是,VHDL 仲裁器永遠(yuǎn)不會(huì)將其中一個(gè)設(shè)備從“游戲”中移除(好吧......幾乎永遠(yuǎn)不會(huì)。在某些情況下,硬件仲裁器會(huì)決定一個(gè)設(shè)備表現(xiàn)不佳并決定將其從“游戲”中移除一個(gè)例子是可插拔卡訪問公共總線,可以在關(guān)鍵時(shí)刻拔掉,如果仲裁器沒有識(shí)別出故障,總線可能會(huì)卡在 - 現(xiàn)在丟失的 - 設(shè)備上)。

仲裁器從其客戶端接收兩種類型的信號:

- 請求:由想要擁有公共資源的每個(gè)設(shè)備聲明。可以同時(shí)斷言許多請求信號,就像許多設(shè)備請求擁有公共資源的許可一樣。另一方面,可以只有一個(gè),甚至沒有斷言的請求信號。后者是在特定時(shí)刻沒有人需要共享資源的情況。

- Grant:由仲裁器斷言,每個(gè)master有一個(gè)grant信號。通常,在任何給定時(shí)間都只會(huì)斷言一個(gè)授權(quán)信號。

第一次實(shí)現(xiàn) - 固定大小,固定優(yōu)先級

我們將分析的第一個(gè)仲裁器具有三個(gè)請求輸入和三個(gè)授權(quán)輸出。它也有一個(gè)固定的主人優(yōu)先權(quán)。master 編號越低,其優(yōu)先級越高。該塊也有忙信號。總線仲裁僅在其處于非活動(dòng)狀態(tài)時(shí)進(jìn)行。如果總線已經(jīng)被授權(quán)給代理,即使更高優(yōu)先級的主機(jī)請求總線,當(dāng)前事務(wù)也必須在仲裁器將總線授權(quán)給另一個(gè)主機(jī)之前完成。

生成授權(quán)信號的邏輯(在進(jìn)程arbiter_pr上)非常簡單。如果第一個(gè)主控(主控 0)斷言請求,則它被授予授權(quán)。只有當(dāng)主控 1 請求總線而主控 0 不請求總線時(shí),它才會(huì)獲得授權(quán)。只有當(dāng)主控 2 請求總線并且主控 0 和主控 1 都沒有請求總線時(shí),它才會(huì)被授予授權(quán)。

gnt信號只有在總線不忙時(shí)才會(huì)改變。進(jìn)程busy_pr和相關(guān)邏輯檢測忙信號的下降沿。在 busy 變?yōu)榈碗娖胶螅惺跈?quán)信號都被取消斷言一個(gè)時(shí)鐘,然后選擇下一個(gè)總線主機(jī)的邏輯被激活。

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity arbiter is

port (

clk : in std_logic;

rst : in std_logic;

-- inputs

req : in std_logic_vector(2 downto 0);

busy : in std_logic;

-- outputs

gnt : out std_logic_vector(2 downto 0)

);

end arbiter;

architecture rtl of arbiter is

signal busy_d : std_logic := '0';

signal busy_fe : std_logic;

begin

busy_pr : process (clk)

begin

if (rising_edge(clk)) then

busy_d <= busy;

end if;

end process busy_pr;

-- Falling edge of busy signal

busy_fe <= '1' when busy = '0' and busy_d = '1' else '0';

arbiter_pr : process (clk, rst)

begin

if (rst = '1') then

gnt <= (others => '0');

elsif (rising_edge(clk)) then

if (busy_fe = '1') then

gnt <= (others => '0');

elsif (busy = '0') then

gnt(0) <= req(0);

gnt(1) <= req(1) and not req(0);

gnt(2) <= req(2) and not (req(0) or req(1));

end if;

end if;

end process arbiter_pr;

end rtl;

gnt信號只有在總線不忙時(shí)才會(huì)改變。進(jìn)程busy_pr和相關(guān)邏輯檢測忙信號的下降沿。在 busy 變?yōu)榈碗娖胶螅惺跈?quán)信號都被取消斷言一個(gè)時(shí)鐘,然后選擇下一個(gè)總線主機(jī)的邏輯被激活。

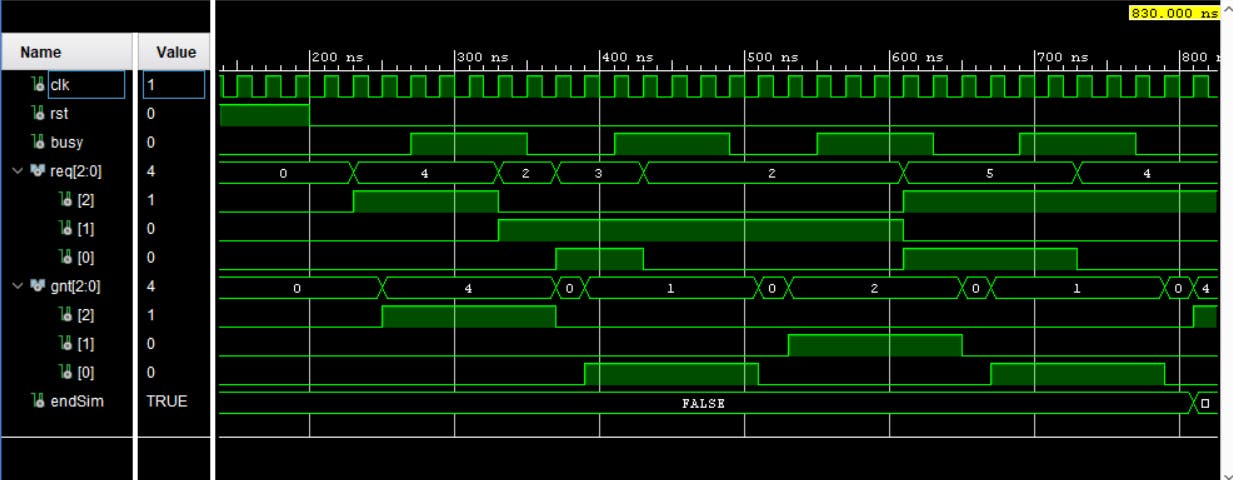

復(fù)位釋放后,沒有未完成的請求,因此仲裁器也不會(huì)斷言任何授權(quán)信號。稍后在模擬中,多個(gè)主機(jī)請求仲裁器的許可(請求已斷言)并根據(jù)其優(yōu)先級獲得授權(quán)。

在 300 到 400ns 之間,主機(jī)“1”斷言其請求信號。兩個(gè)時(shí)鐘周期后,來自主機(jī)“0”的請求被置位。因此,即使 master '0' 稍后到達(dá),當(dāng)仲裁器可以自由分配總線時(shí),它也會(huì)將其分配給 master '0'。

請注意,在gnt信號之間始終有一個(gè)“休息”時(shí)鐘。每個(gè)主機(jī)使用總線四個(gè)時(shí)鐘并放棄總線(這可以在忙信號的持續(xù)時(shí)間內(nèi)看到)。

稍后,主機(jī)“2”和“0”都請求總線,正如預(yù)期的那樣,總線被授予主機(jī)“0”。

GitHub 上提供了仲裁器“簡單實(shí)現(xiàn)”、測試平臺(tái)和 Modelsim 文件的 VHDL 源代碼

第二種實(shí)現(xiàn)——可變大小,固定優(yōu)先級

上述仲裁器的邏輯是固定大小的。通過一些更改,并通過使用不受約束的端口(查看req和gnt端口),我們可以制作一個(gè)通用仲裁器,其大小可以在實(shí)現(xiàn)時(shí)決定。

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity arbiter_unc is

port (

clk : in std_logic;

rst : in std_logic;

-- inputs

req : in std_logic_vector;

busy : in std_logic;

-- outputs

gnt : out std_logic_vector

);

end arbiter_unc;

architecture rtl of arbiter_unc is

signal busy_d : std_logic;

signal busy_fe : std_logic;

begin

busy_pr : process (clk)

begin

if (rising_edge(clk)) then

busy_d <= busy;

end if;

end process busy_pr;

-- Falling edge of busy signal

busy_fe <= '1' when busy = '0' and busy_d = '1' else '0';

arbiter_pr : process (clk)

variable prio_req : std_logic;

begin

if (rising_edge(clk)) then

if (rst = '1') then

gnt <= (others => '0');

else

if (busy_fe = '1') then

gnt <= (others => '0');

elsif (busy = '0') then

gnt(0) <= req(0);

for I in 1 to req'left - 1 loop

prio_req := '0';

for J in 1 to I loop

prio_req := prio_req or req(J - 1);

end loop;

gnt(I) <= req(I) and not prio_req;

end loop;

end if;

end if;

end if;

end process arbiter_pr;

end rtl;

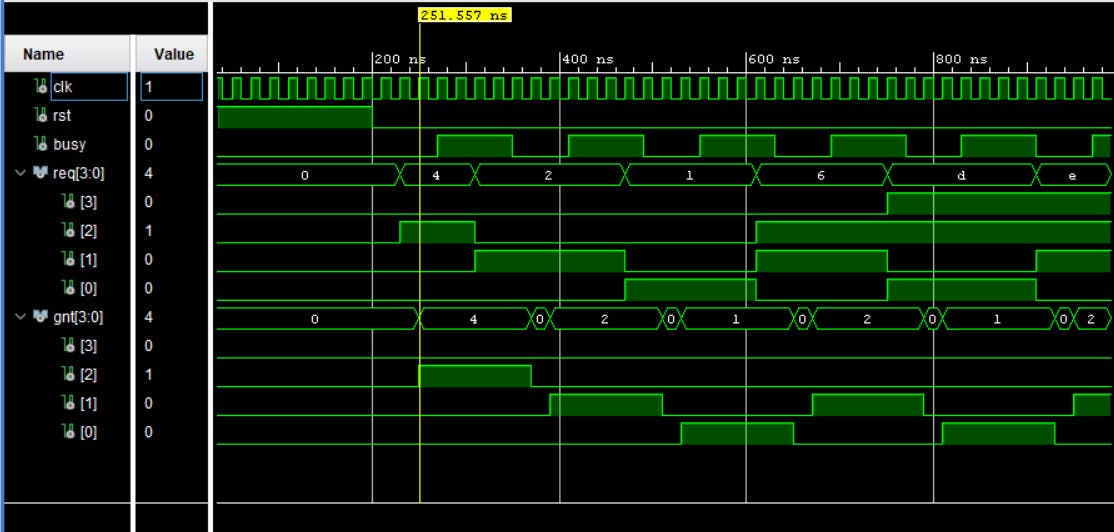

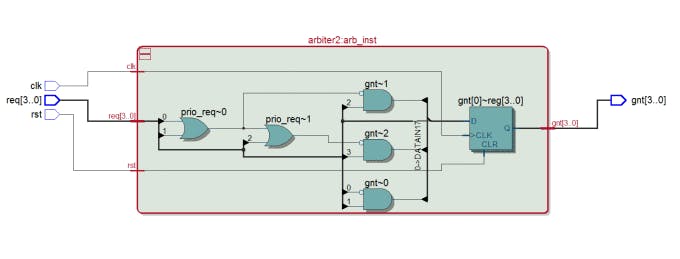

可變大小仲裁器的 Vivado 仿真,實(shí)例化為 size = 4

?

?

?

?

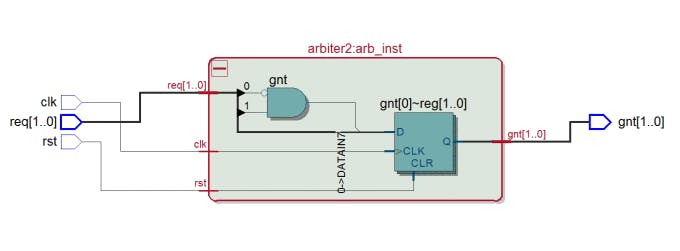

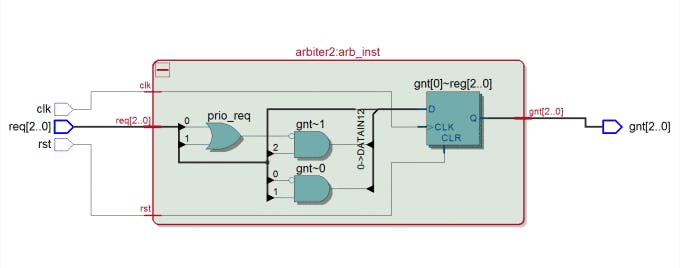

RTL 表示顯示了處理越來越多的端口所需的組合復(fù)雜性不斷增加,并且是使用 Quartus Prime 15.1 生成的。請注意,某些塊(如輸出 FF)不是單個(gè)而是堆疊的原始實(shí)例化。如前所述,如果多個(gè)主機(jī)請求總線,則編號最小的主機(jī)將獲得gnt(回想一下,在任何給定時(shí)間只有一個(gè)主機(jī)應(yīng)接收gnt)。這個(gè)仲裁器有一個(gè)固定的優(yōu)先級。雖然在某些應(yīng)用程序中可以使用這樣的仲裁器,但最常見的仲裁器類型沒有固定的優(yōu)先級。我將在以后的文章中討論更復(fù)雜的仲裁器(循環(huán)法)。

建議練習(xí)

- 如前所述,這個(gè)簡單的仲裁器具有固定的優(yōu)先級。如果多個(gè)主控?cái)嘌运鼈兊恼埱笮盘枺瑒t編號最小的主控器被賦予gnt。設(shè)計(jì)一個(gè)固定優(yōu)先級的主機(jī),其中編號最高的主機(jī)具有最高優(yōu)先級。

- 在這個(gè)仲裁器中,只要一個(gè)主機(jī)請求總線,總線就被授予它。添加超時(shí)邏輯。如果一個(gè)主機(jī)斷言req超過 10 個(gè)時(shí)鐘周期,如果其他請求未完成,則取消斷言對該主機(jī)的授權(quán)信號。

- 一些仲裁者具有公園功能。Park 的意思是,如果沒有未完成的請求,gnt信號將發(fā)送給最后一個(gè)接收到它的主機(jī)。在另一個(gè)版本中,如果沒有主機(jī)斷言req,則gnt信號被分配給“默認(rèn)主機(jī)”。為這兩個(gè)選項(xiàng)中的每一個(gè)選項(xiàng)設(shè)計(jì)代碼。

GitHub 上提供了仲裁器“無約束實(shí)現(xiàn)”、測試平臺(tái)和 Modelsim 文件的 VHDL 源代碼

誠邀您訪問我的網(wǎng)站,在那里您可以找到更多VHDL 項(xiàng)目、文章以及合法免費(fèi)的書籍和課程。

- 開源VHDL驗(yàn)證方法 (OSVVM) 0次下載

- VHDL測試平臺(tái)開源分享

- 開源網(wǎng)絡(luò)協(xié)議分析器WireShark軟件下載 15次下載

- 基于SaaS的替代性糾紛在線仲裁系統(tǒng) 9次下載

- VHDL語言的詳細(xì)講解學(xué)習(xí)課件免費(fèi)下載 17次下載

- VHDL最經(jīng)典的參考指南資料免費(fèi)下載 32次下載

- VHDL的參考手冊免費(fèi)下載 32次下載

- VHDL測試平臺(tái)編寫綜述 19次下載

- 電梯控制器的VHDL程序與仿真資料合集 11次下載

- 如何進(jìn)行SOC總線仲裁算法的研究資料說明 5次下載

- 最全面的VHDL例程源碼資料下載 115次下載

- 低功耗應(yīng)用處理器的特征 3次下載

- PLD Programming Using VHDL 0次下載

- OPB總線仲裁器的RTL設(shè)計(jì)與FPGA實(shí)現(xiàn)

- PCI總線仲裁器的設(shè)計(jì)及實(shí)現(xiàn)

- Verilog與VHDL的比較 Verilog HDL編程技巧 259次閱讀

- Verilog到VHDL轉(zhuǎn)換的經(jīng)驗(yàn)與技巧總結(jié) 2615次閱讀

- 例說Verilog HDL和VHDL區(qū)別 3948次閱讀

- 基于LEON開源微處理器IP軟核實(shí)現(xiàn)SoC系統(tǒng)基本平臺(tái)的構(gòu)建 2871次閱讀

- 如何在VHDL中解決綜合工具使用轉(zhuǎn)化問題 2666次閱讀

- 基于CPLD器件實(shí)現(xiàn)雙主設(shè)備PCI總線仲裁器的設(shè)計(jì) 1248次閱讀

- C到VHDL的編譯器設(shè)計(jì)與實(shí)現(xiàn)詳解 4659次閱讀

- CAN總線仲裁示意圖_CAN總線位仲裁技術(shù)及優(yōu)缺點(diǎn) 1.6w次閱讀

- vhdl和verilog的區(qū)別_vhdl和verilog哪個(gè)好? 12.3w次閱讀

- VHDL語言設(shè)計(jì)四人搶答器(三種設(shè)計(jì)方案) 3.7w次閱讀

- 基于VHDL的電子計(jì)時(shí)器的設(shè)計(jì)方法詳解 2.5w次閱讀

- vhdl按鍵控制數(shù)碼管顯示 1.8w次閱讀

- 8位移位寄存器vhdl代碼 1.6w次閱讀

- 我對VHDL的延時(shí)理解 4192次閱讀

- 基于VHDL的交通燈控制器設(shè)計(jì) 6054次閱讀

下載排行

本周

- 1山景DSP芯片AP8248A2數(shù)據(jù)手冊

- 1.06 MB | 532次下載 | 免費(fèi)

- 2RK3399完整板原理圖(支持平板,盒子VR)

- 3.28 MB | 339次下載 | 免費(fèi)

- 3TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費(fèi)

- 4DFM軟件使用教程

- 0.84 MB | 295次下載 | 免費(fèi)

- 5元宇宙深度解析—未來的未來-風(fēng)口還是泡沫

- 6.40 MB | 227次下載 | 免費(fèi)

- 6迪文DGUS開發(fā)指南

- 31.67 MB | 194次下載 | 免費(fèi)

- 7元宇宙底層硬件系列報(bào)告

- 13.42 MB | 182次下載 | 免費(fèi)

- 8FP5207XR-G1中文應(yīng)用手冊

- 1.09 MB | 178次下載 | 免費(fèi)

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費(fèi)

- 2555集成電路應(yīng)用800例(新編版)

- 0.00 MB | 33566次下載 | 免費(fèi)

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費(fèi)

- 4開關(guān)電源設(shè)計(jì)實(shí)例指南

- 未知 | 21549次下載 | 免費(fèi)

- 5電氣工程師手冊免費(fèi)下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費(fèi)

- 6數(shù)字電路基礎(chǔ)pdf(下載)

- 未知 | 13750次下載 | 免費(fèi)

- 7電子制作實(shí)例集錦 下載

- 未知 | 8113次下載 | 免費(fèi)

- 8《LED驅(qū)動(dòng)電路設(shè)計(jì)》 溫德爾著

- 0.00 MB | 6656次下載 | 免費(fèi)

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費(fèi)

- 2protel99se軟件下載(可英文版轉(zhuǎn)中文版)

- 78.1 MB | 537798次下載 | 免費(fèi)

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420027次下載 | 免費(fèi)

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費(fèi)

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費(fèi)

- 6電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191187次下載 | 免費(fèi)

- 7十天學(xué)會(huì)AVR單片機(jī)與C語言視頻教程 下載

- 158M | 183279次下載 | 免費(fèi)

- 8proe5.0野火版下載(中文版免費(fèi)下載)

- 未知 | 138040次下載 | 免費(fèi)

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問

提問  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評論