資料介紹

描述

介紹

安全哈希算法 (SHA-256) 是一種加密哈希函數(shù),用于保護(hù)密碼或網(wǎng)站服務(wù)器等安全性。它的一個(gè)著名用途是比特幣的工作量證明,它基于 SHA256 算法來(lái)驗(yàn)證交易。

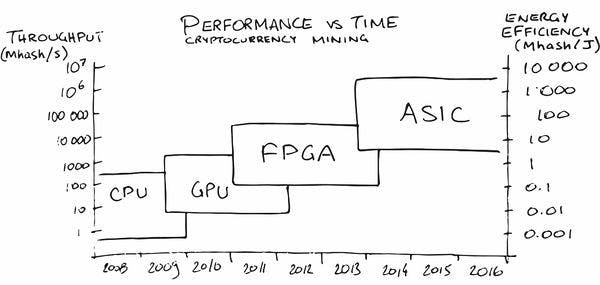

我想很多人會(huì)聽(tīng)說(shuō) GPU 被用于挖礦,因?yàn)?GPU 更適合哈希算法所需的數(shù)字運(yùn)算。但是,您知道嗎,可以使用 FPGA 完成定制化程度更高的加速?通過(guò)配置 FPGA 以在硬件中加速它,它的性能甚至?xí)?GPU 更高。事實(shí)上,比特幣礦工早在 2011 年就開(kāi)始使用 FPGA 進(jìn)行挖礦。

如今,挖比特幣的復(fù)雜性越來(lái)越高,F(xiàn)PGA 挖礦可能不再有利可圖。然而,我們可以將其作為一個(gè)有用的案例研究來(lái)了解如何使用 Xilinx FPGA 輕松完成加速。也許下次當(dāng)我們看到另一個(gè)潛在的算法加速用例時(shí),我們就會(huì)知道該怎么做。

開(kāi)發(fā)流程總結(jié)

我們將使用 Xilinx Kria KV260 的硬件套件以及新發(fā)布的 Ubuntu 20.04 LTS 操作系統(tǒng)。我們將安裝 PYNQ,以便我們可以從 Python notebook 獲得硬件加速的好處。

在我們的 PC 上,我們將使用 Vitis HLS 將開(kāi)源 C 代碼實(shí)現(xiàn)轉(zhuǎn)換為硬件 IP 模塊。之后,Vivado 用于創(chuàng)建與處理器的連接并生成比特流。

最后,我們將比特流傳輸?shù)?Xilinx Kria 并在 PYNQ 環(huán)境中對(duì)性能增益進(jìn)行基準(zhǔn)測(cè)試。

設(shè)置 SD 卡映像

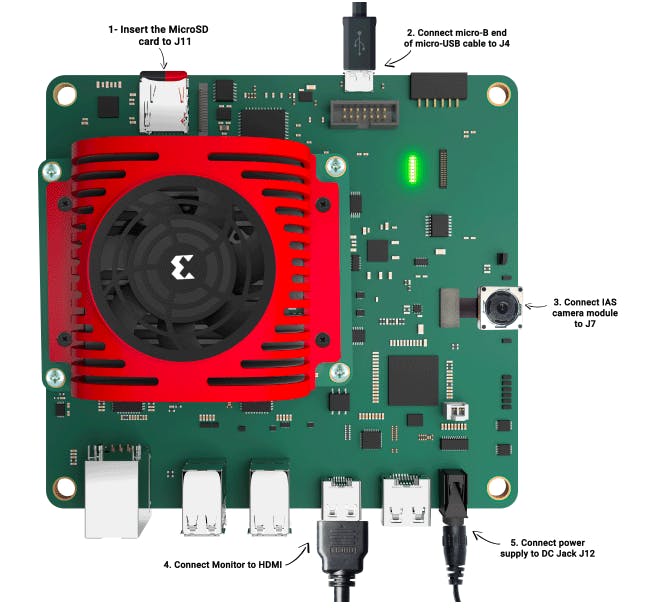

首先我們需要為 Kria KV260 Vision AI Starter Kit 準(zhǔn)備 SD 卡。

包裝盒中提供了一張 16GB 的 SD 卡,但我建議至少使用 32GB的,因?yàn)樵O(shè)置可能會(huì)超過(guò) 16GB 的空間。

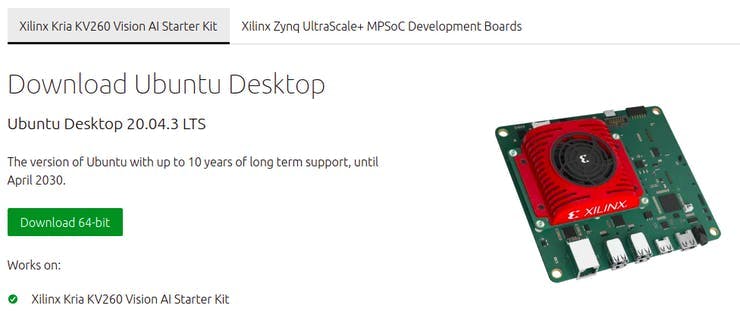

我們將使用 Ubuntu 20.04.3 LTS 下載。從網(wǎng)站下載圖像并將其保存在您的計(jì)算機(jī)上。

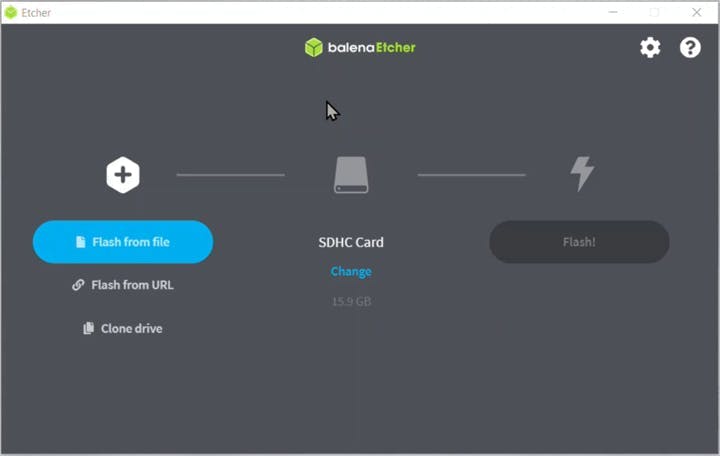

在您的 PC 上,下載 Balena Etcher 以將其寫(xiě)入您的 SD 卡。

完成后,您的 SD 卡已準(zhǔn)備就緒,您可以將其插入 Kria 以設(shè)置 Xilinx Ubuntu!將 USB 鍵盤(pán)、USB 鼠標(biāo)、HDMI/DisplayPort 和以太網(wǎng)連接到 Kria。

連接電源打開(kāi) Kria,您將看到 Ubuntu 登錄屏幕。

默認(rèn)登錄憑據(jù)是用戶(hù)名:ubuntu密碼:ubuntu

啟動(dòng)時(shí),界面可能會(huì)非常慢,所以我運(yùn)行了這些命令來(lái)禁用動(dòng)畫(huà)調(diào)整以加快速度。

gsettings set org.gnome.desktop.interface enable-animations false

gsettings set org.gnome.shell.extensions.dash-to-dock animate-show-apps false

接下來(lái),通過(guò)執(zhí)行系統(tǒng)更新并調(diào)用此命令將系統(tǒng)更新到最新版本

sudo apt upgrade

安裝用于系統(tǒng)管理的 xlnx-config snap 并對(duì)其進(jìn)行配置(有關(guān) Xilinx wiki 的更多信息):

sudo snap install xlnx-config --classic

xlnx-config.sysinit

現(xiàn)在檢查設(shè)備配置是否工作正常。

sudo xlnx-config --xmutil boardid -b som

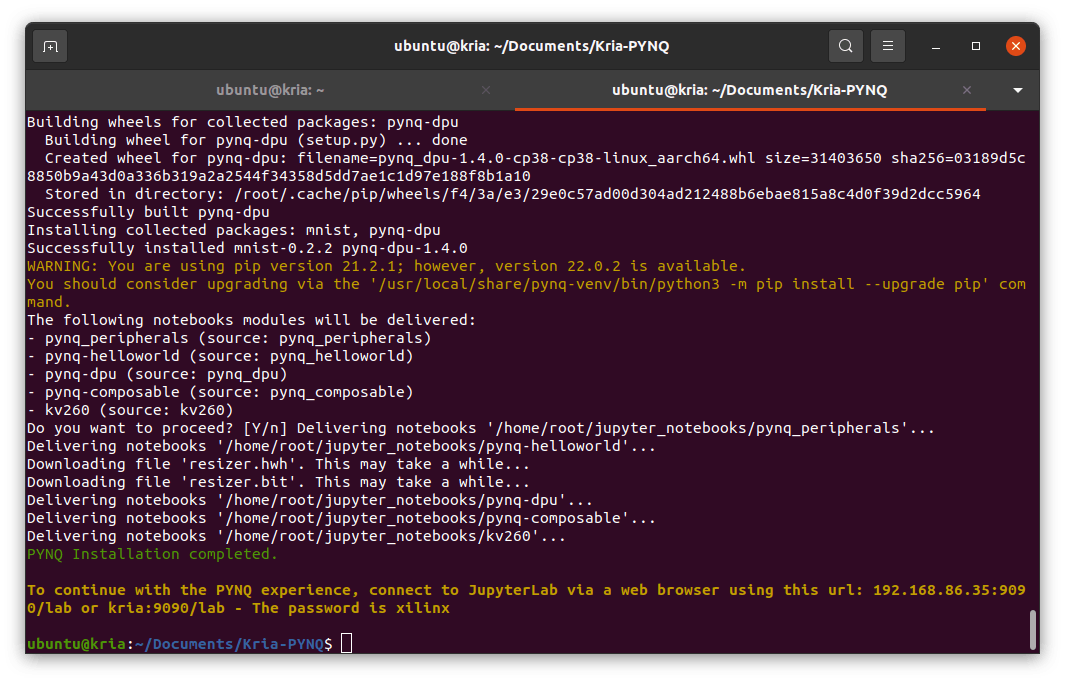

安裝最新的Kria-PYNQ 包。這最多需要 30 分鐘。

git clone https://github.com/Xilinx/Kria-PYNQ.git

cd Kria-PYNQ/

sudo bash install.sh

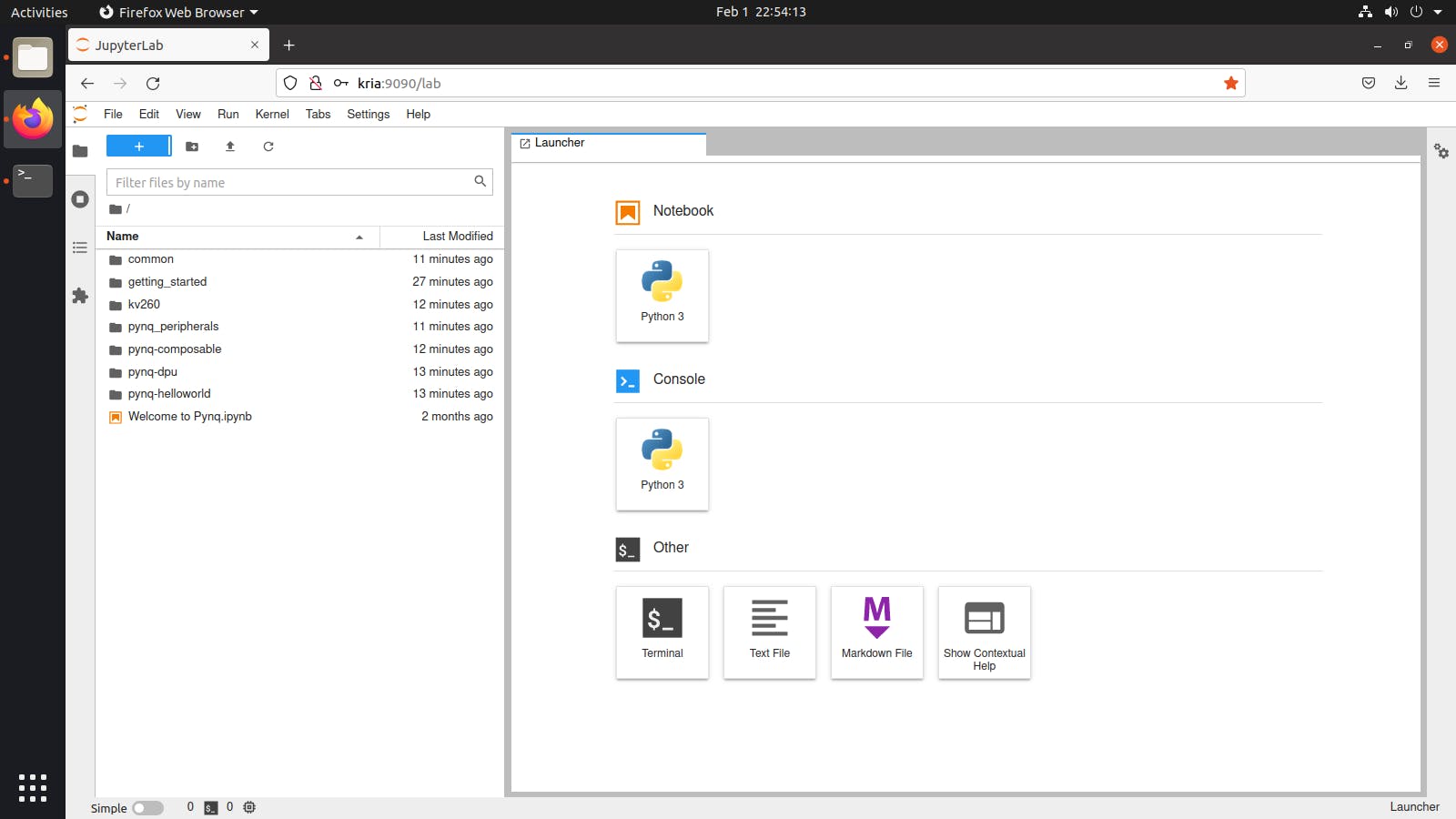

安裝后,您可以在網(wǎng)絡(luò)瀏覽器中轉(zhuǎn)到“ kria:9090 ”以查看 Jupyter 筆記本。默認(rèn)密碼為xilinx 。

Kria 系統(tǒng)已準(zhǔn)備就緒。現(xiàn)在讓我們回到我們的 PC 來(lái)創(chuàng)建 PYNQ 覆蓋比特流。

Vitis HLS 中的加速器 IP

使用 Vitis HLS,我們可以將許多現(xiàn)有的 C/C++ 代碼轉(zhuǎn)換為硬件 IP 模塊。我將在不做任何修改的情況下調(diào)整此 SHA256 C 代碼實(shí)現(xiàn)。

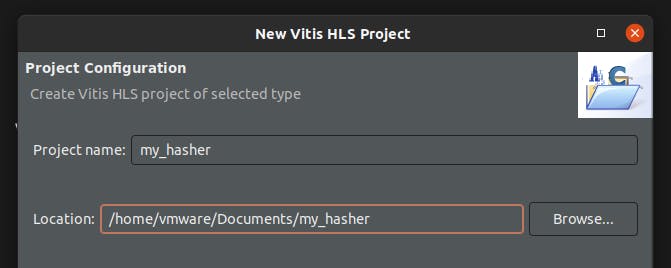

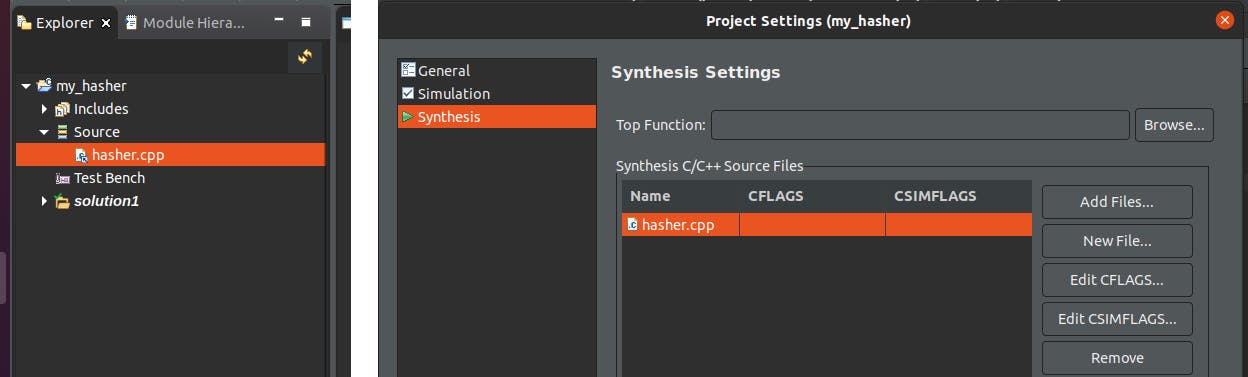

啟動(dòng) Vitis HLS 并創(chuàng)建一個(gè)新項(xiàng)目。

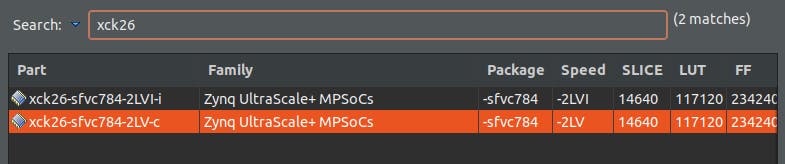

在下一頁(yè)上,選擇目標(biāo)設(shè)備。對(duì)于 Kria KV260 Vision AI 入門(mén)套件,它使用的是零件:xck26-sfvc784-2lv-c。

進(jìn)入工作區(qū)后,創(chuàng)建一個(gè)源文件。選擇該文件作為項(xiàng)目綜合設(shè)置中的頂級(jí)函數(shù)。

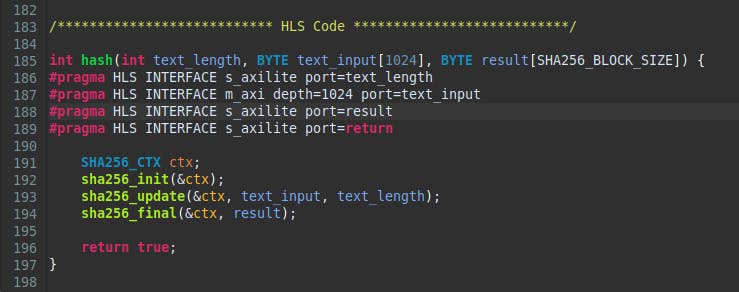

在代碼中,我創(chuàng)建了一個(gè)名為hash(). 它基本上只調(diào)用 SHA256 散列函數(shù)。

現(xiàn)在請(qǐng)注意,此功能是在可編程邏輯 (PL) 中實(shí)現(xiàn)的。這意味著 的參數(shù)hash()實(shí)際上是需要傳輸?shù)教幚硐到y(tǒng) (PS) 或從處理系統(tǒng) (PS) 傳輸?shù)妮斎牒洼敵觥?/font>因此,需要選擇合適的通信接口。

對(duì)于 和 之類(lèi)的小變量text_length,result我選擇了s_axilitewhich 是適合小變量的串行協(xié)議。以后從 PYNQ 訪(fǎng)問(wèn)它也相對(duì)容易。

對(duì)于像 的大型緩沖區(qū)text_input[1024],我選擇m_axi了并行協(xié)議。它占用了更多的邏輯和互連,但這是必要的,以便傳輸數(shù)據(jù)足夠快。

有關(guān)更多信息,代碼在本項(xiàng)目末尾提供。

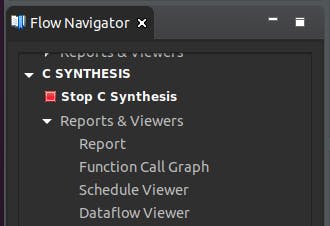

在 Flow Navigator 下啟動(dòng) C 綜合。

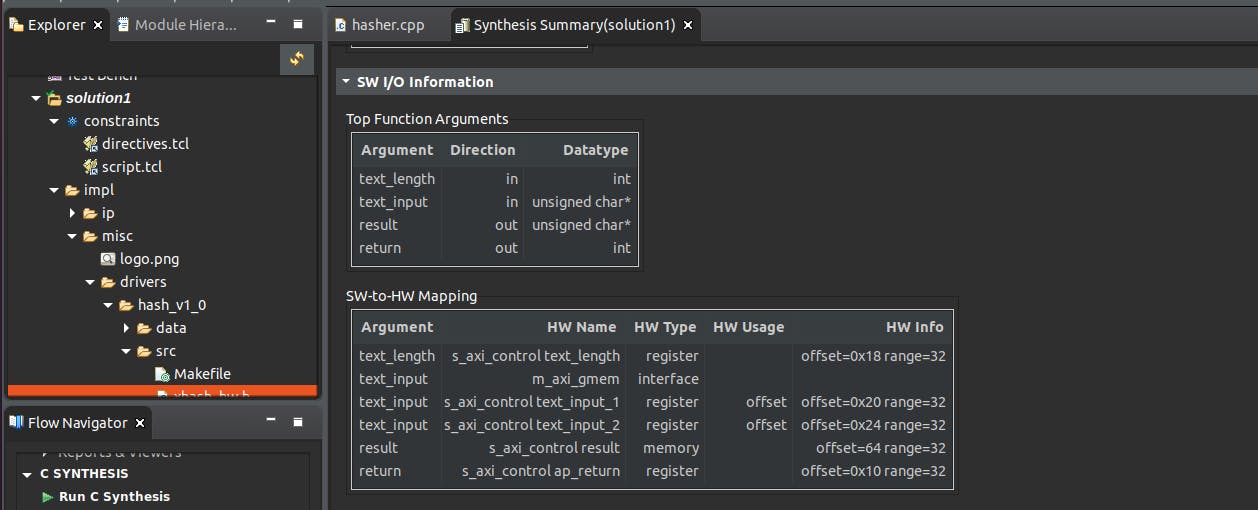

綜合后,您可以驗(yàn)證我們稍后將在 PYNQ 中訪(fǎng)問(wèn)的參數(shù)。

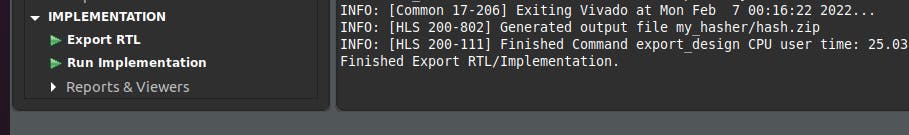

最后,選擇 Export RTL 并選擇要將其保存到的位置。它將輸出一個(gè) zip 文件,其中包含要在 Vivado 中導(dǎo)入的 IP 模塊。

Vivado 中的框圖綜合

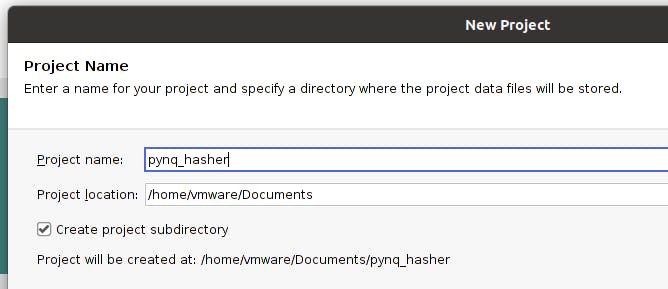

打開(kāi) Vivado 并創(chuàng)建一個(gè)新項(xiàng)目

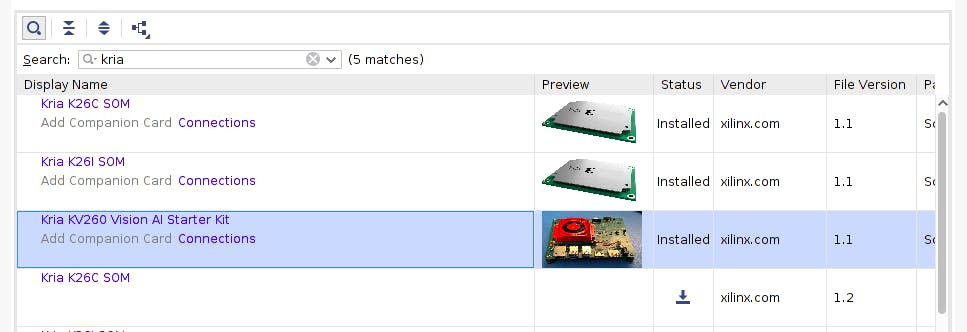

選擇 Kria KV260 Vision AI 入門(mén)套件。繼續(xù)使用所有默認(rèn)值,直到到達(dá)項(xiàng)目工作區(qū)。

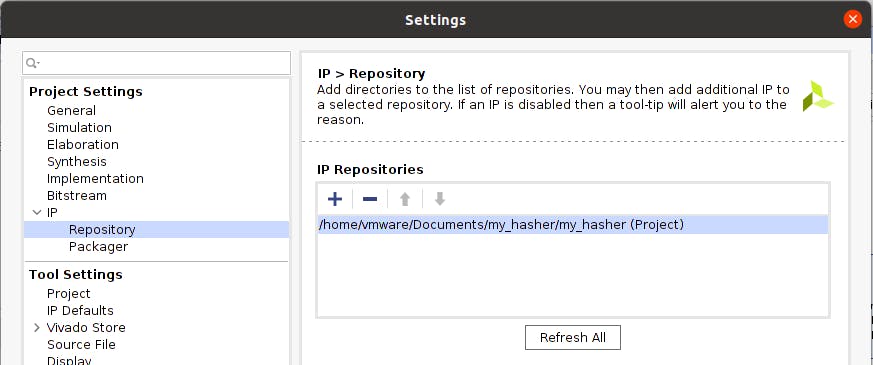

在我們做任何其他事情之前,我們需要添加我們之前創(chuàng)建的 IP。

轉(zhuǎn)到Project Manager > Settings > IP > Repository ,然后添加包含 zip 文件的文件夾。

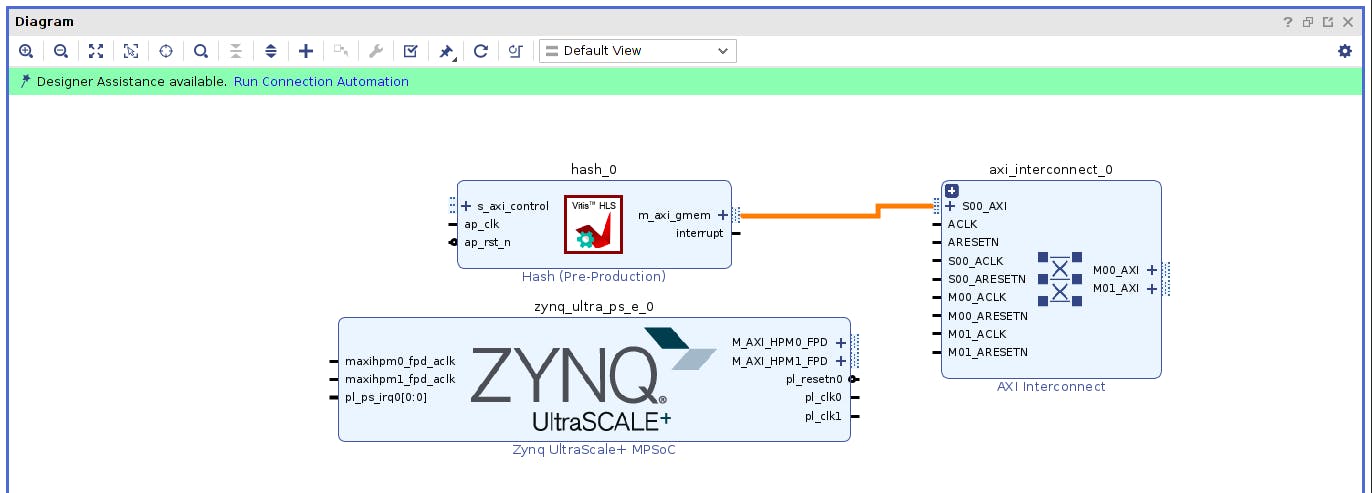

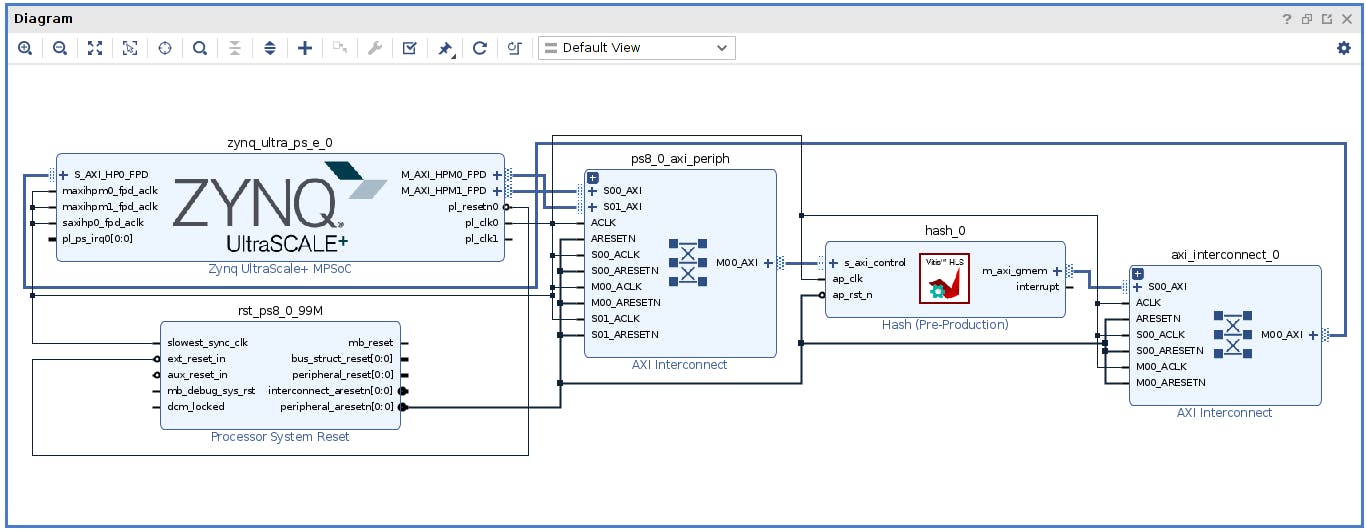

在 IP Integrator 下,選擇 Create Block Diagram。添加以下塊:

- Zynq UltraScale+ MPSoc(這是 PS)

- 哈希(我們從 Vitis HLS 生成的 IP)

-

AXI 互連(從我們的 IP 互連到

m_axi總線(xiàn))

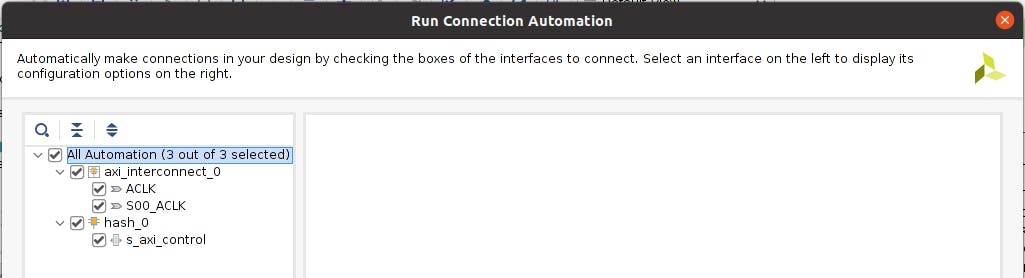

之后,運(yùn)行連接自動(dòng)化。選擇所有可能的自動(dòng)化并接受默認(rèn)設(shè)置。

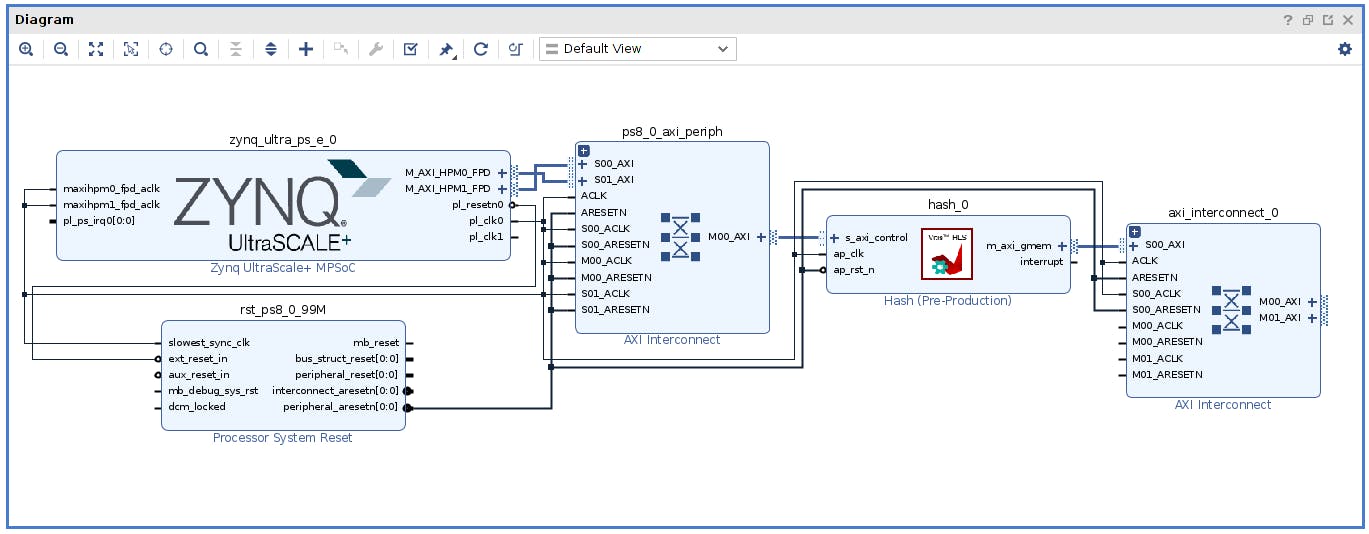

請(qǐng)注意,m_axi(Master)的互連總線(xiàn)仍未連接。這是因?yàn)槲彝浽赑S上啟用Slave接口。

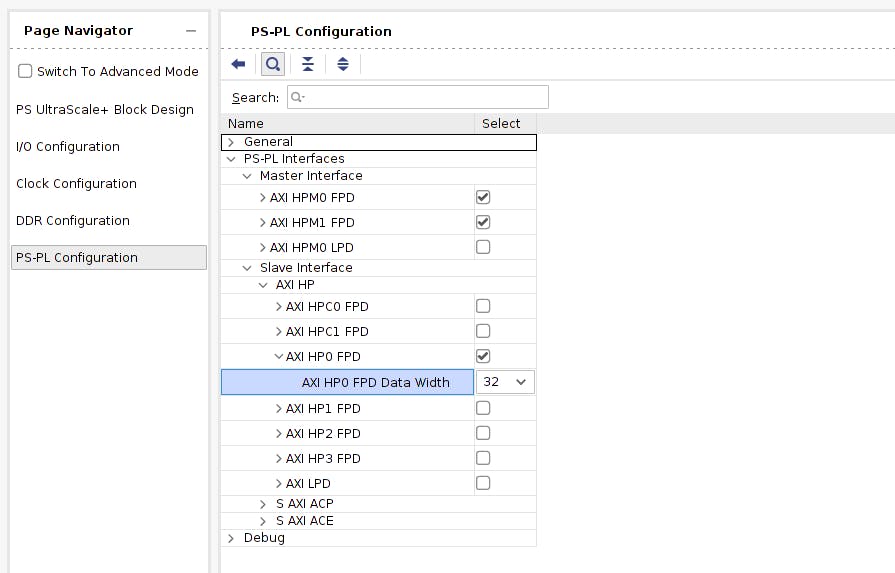

雙擊 Zynq UltraScale+ MPSoc 塊。啟用 AXI HP0 FPD (高性能)。檢查數(shù)據(jù)寬度是否為 32 位,這與 HLS 中合成的內(nèi)容相匹配。

再次運(yùn)行連接自動(dòng)化。這是最終的框圖。

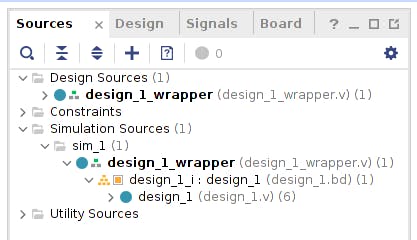

在 Sources 下,右鍵單擊設(shè)計(jì)并選擇 Create HDL Wrapper。它會(huì)自動(dòng)包裝設(shè)計(jì),以便您為綜合做好準(zhǔn)備。

?

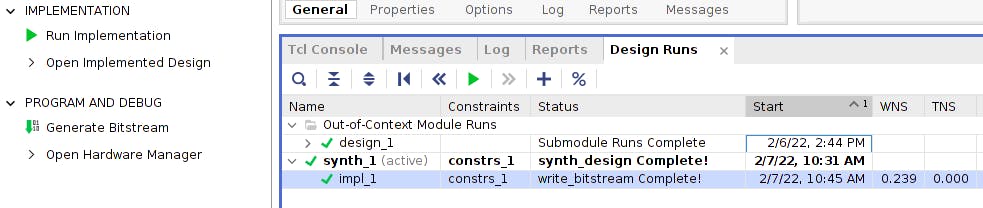

生成比特流。完成綜合和實(shí)施可能需要長(zhǎng)達(dá)一個(gè)小時(shí)的時(shí)間。

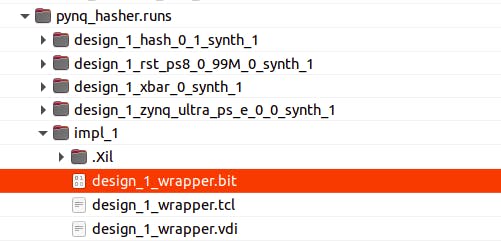

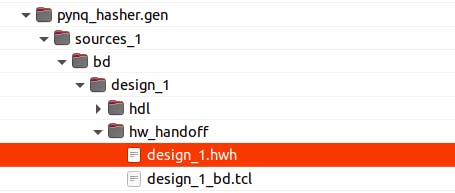

最后,為了獲得 PYNQ 覆蓋,我們必須檢索 2 個(gè)文件:.bit文件和.hwh文件。

可以在以下位置找到比特流文件:*.runs/impl_1/design_1_wrapper.bit

硬件切換文件可在以下位置找到:*.gen/sources_1/bd/design_1/hw_handoff/design_1.hwh

將這些文件復(fù)制到 Kria。

PYNQ 中的接口

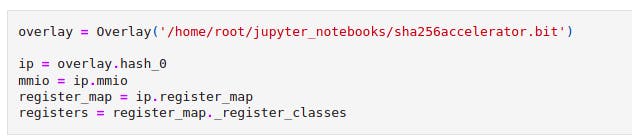

我復(fù)制了 2 個(gè)文件并將其重命名為sha256accelerator.bitand sha256accelerator.hwh。請(qǐng)注意,兩個(gè)文件必須具有相同的名稱(chēng)才能正確用作 PYNQ 覆蓋。

我將解釋我的代碼的一些片段。您可以在下面找到完整的代碼。

創(chuàng)建一個(gè)新的 Jupyter notebook,我們可以在其中編程比特流。

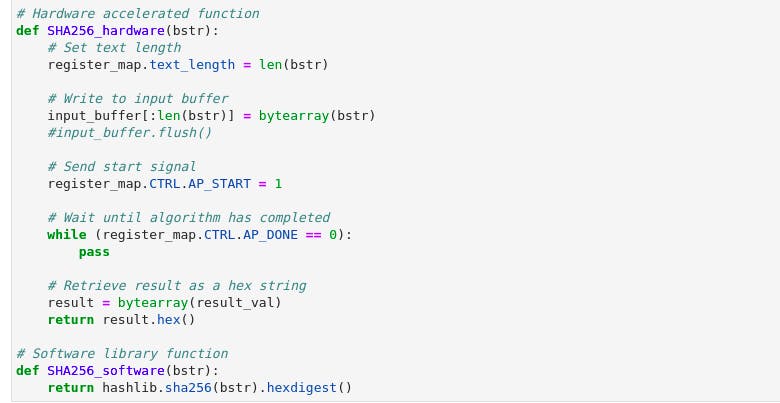

在這里,我定義了硬件功能,即將輸入數(shù)據(jù)寫(xiě)入緩沖區(qū)并啟動(dòng)該過(guò)程。完成后,該函數(shù)將返回。我還定義了一個(gè)稱(chēng)為內(nèi)置庫(kù)的軟件功能。

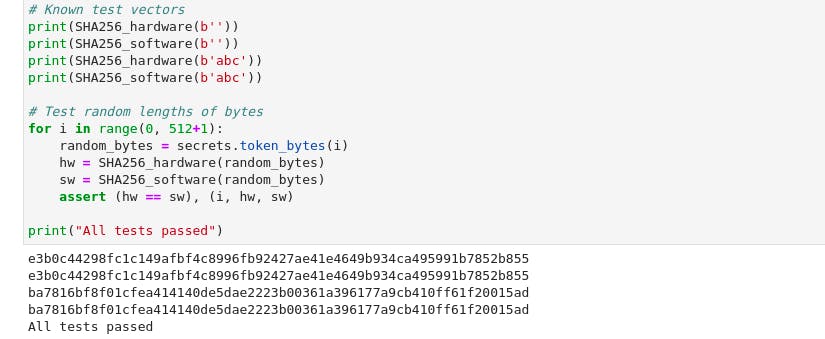

運(yùn)行一些測(cè)試,我們可以比較兩個(gè)函數(shù)的輸入,以驗(yàn)證一切都在硬件上正確實(shí)現(xiàn)。

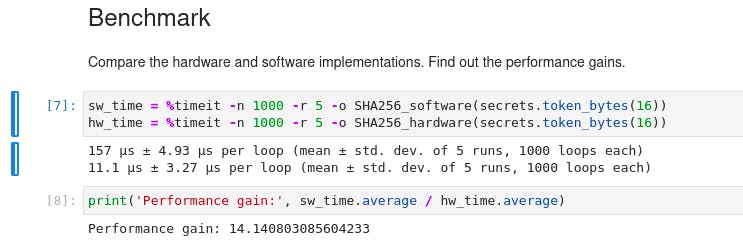

基準(zhǔn)性能

運(yùn)行一些基準(zhǔn)測(cè)試,我們發(fā)現(xiàn)硬件實(shí)現(xiàn)比在軟件上運(yùn)行快約 14 倍。

結(jié)論

總而言之,使用 Vitis HLS 無(wú)需任何修改即可輕松加速 C 函數(shù)。盡管需要對(duì)硬件協(xié)議及其變體有一定的了解和了解,但軟件過(guò)程相對(duì)簡(jiǎn)單。

從這里,我們了解過(guò)去如何使用 FPGA 來(lái)加速這些重復(fù)性計(jì)算,例如區(qū)塊鏈挖掘。通過(guò)直接針對(duì)算法,硬件更具體,因此性能更高。

- Vitis HLS:使用任務(wù)級(jí)并行性的高性能設(shè)計(jì)

- Vitis HLS移植指南

- 使用PYNQ和Vitis AI的智能辦公室熱辦公桌

- 《醫(yī)用電子直線(xiàn)加速器》pdf 0次下載

- 基于STM32的C語(yǔ)言SHA256加密算法

- 基于FPGA的SIMD卷積神經(jīng)網(wǎng)絡(luò)加速器 24次下載

- 神經(jīng)網(wǎng)絡(luò)加速器簡(jiǎn)述 13次下載

- 基于深度學(xué)習(xí)的矩陣乘法加速器設(shè)計(jì)方案 3次下載

- Vitis初探—1.將設(shè)計(jì)從SDSoC/Vivado HLS遷移到Vitis上

- Vitis Vision | 利用Vitis HLS tcl shell 一鍵跑通視覺(jué)加速例程

- 工具包和Eval板幫助加速加速器應(yīng)用 13次下載

- Green網(wǎng)絡(luò)加速器 24次下載

- DRM系統(tǒng)的SHA256算法設(shè)計(jì)及FPGA實(shí)現(xiàn) 141次下載

- 加速器控制技術(shù)

- 基于FPGA的SHA-256算法實(shí)現(xiàn)

- 在Windows 10上創(chuàng)建并運(yùn)行AMD Vitis?視覺(jué)庫(kù)示例 825次閱讀

- 一個(gè)微型的粒子加速器 836次閱讀

- 通過(guò)SHA-256主/從身份驗(yàn)證系統(tǒng)實(shí)現(xiàn)更高的安全性 1196次閱讀

- 使用AXI CDMA制作FPGA AI加速器通道 2139次閱讀

- 理解Vitis HLS默認(rèn)行為 1880次閱讀

- Vitis HLS知識(shí)庫(kù)總結(jié) 3546次閱讀

- Vitis HLS如何添加HLS導(dǎo)出的.xo文件 3117次閱讀

- 使用AXI4-Lite將Vitis HLS創(chuàng)建的IP連接到PS 848次閱讀

- Vitis初探—1.將設(shè)計(jì)從SDSoC/Vivado HLS遷移到Vitis上的教程 3952次閱讀

- 如何在Vitis HLS中使用C語(yǔ)言代碼創(chuàng)建AXI4-Lite接口 1872次閱讀

- Vitis HLS工具簡(jiǎn)介及設(shè)計(jì)流程 2410次閱讀

- 如何在Vitis HLS中使用C語(yǔ)言代碼創(chuàng)建AXI4-Lite接口 6495次閱讀

- XIlinx利用HLS進(jìn)行加速設(shè)計(jì)進(jìn)度 6748次閱讀

- Hash算法簡(jiǎn)介 5064次閱讀

- 基于SHA-256安全認(rèn)證工作原理的最新安全認(rèn)證解決方案 5390次閱讀

下載排行

本周

- 1DD3118電路圖紙資料

- 0.08 MB | 1次下載 | 免費(fèi)

- 2AD庫(kù)封裝庫(kù)安裝教程

- 0.49 MB | 1次下載 | 免費(fèi)

- 3PC6206 300mA低功耗低壓差線(xiàn)性穩(wěn)壓器中文資料

- 1.12 MB | 1次下載 | 免費(fèi)

- 4網(wǎng)絡(luò)安全從業(yè)者入門(mén)指南

- 2.91 MB | 1次下載 | 免費(fèi)

- 5DS-CS3A P00-CN-V3

- 618.05 KB | 1次下載 | 免費(fèi)

- 6海川SM5701規(guī)格書(shū)

- 1.48 MB | 次下載 | 免費(fèi)

- 7H20PR5電磁爐IGBT功率管規(guī)格書(shū)

- 1.68 MB | 次下載 | 1 積分

- 8IP防護(hù)等級(jí)說(shuō)明

- 0.08 MB | 次下載 | 免費(fèi)

本月

- 1貼片三極管上的印字與真實(shí)名稱(chēng)的對(duì)照表詳細(xì)說(shuō)明

- 0.50 MB | 103次下載 | 1 積分

- 2涂鴉各WiFi模塊原理圖加PCB封裝

- 11.75 MB | 89次下載 | 1 積分

- 3錦銳科技CA51F2 SDK開(kāi)發(fā)包

- 24.06 MB | 43次下載 | 1 積分

- 4錦銳CA51F005 SDK開(kāi)發(fā)包

- 19.47 MB | 19次下載 | 1 積分

- 5PCB的EMC設(shè)計(jì)指南

- 2.47 MB | 16次下載 | 1 積分

- 6HC05藍(lán)牙原理圖加PCB

- 15.76 MB | 13次下載 | 1 積分

- 7802.11_Wireless_Networks

- 4.17 MB | 12次下載 | 免費(fèi)

- 8蘋(píng)果iphone 11電路原理圖

- 4.98 MB | 6次下載 | 2 積分

總榜

- 1matlab軟件下載入口

- 未知 | 935127次下載 | 10 積分

- 2開(kāi)源硬件-PMP21529.1-4 開(kāi)關(guān)降壓/升壓雙向直流/直流轉(zhuǎn)換器 PCB layout 設(shè)計(jì)

- 1.48MB | 420064次下載 | 10 積分

- 3Altium DXP2002下載入口

- 未知 | 233089次下載 | 10 積分

- 4電路仿真軟件multisim 10.0免費(fèi)下載

- 340992 | 191390次下載 | 10 積分

- 5十天學(xué)會(huì)AVR單片機(jī)與C語(yǔ)言視頻教程 下載

- 158M | 183342次下載 | 10 積分

- 6labview8.5下載

- 未知 | 81588次下載 | 10 積分

- 7Keil工具M(jìn)DK-Arm免費(fèi)下載

- 0.02 MB | 73815次下載 | 10 積分

- 8LabVIEW 8.6下載

- 未知 | 65989次下載 | 10 積分

電子發(fā)燒友App

電子發(fā)燒友App

創(chuàng)作

創(chuàng)作 發(fā)文章

發(fā)文章 發(fā)帖

發(fā)帖  提問(wèn)

提問(wèn)  發(fā)資料

發(fā)資料 發(fā)視頻

發(fā)視頻 上傳資料賺積分

上傳資料賺積分

評(píng)論