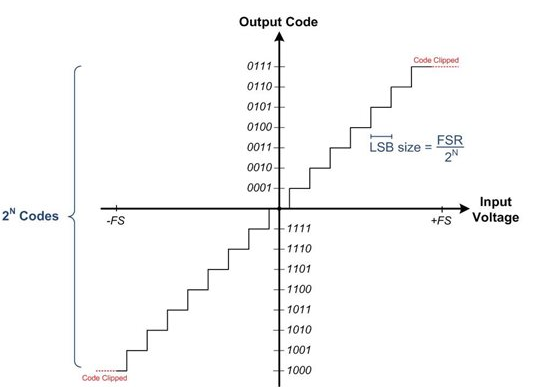

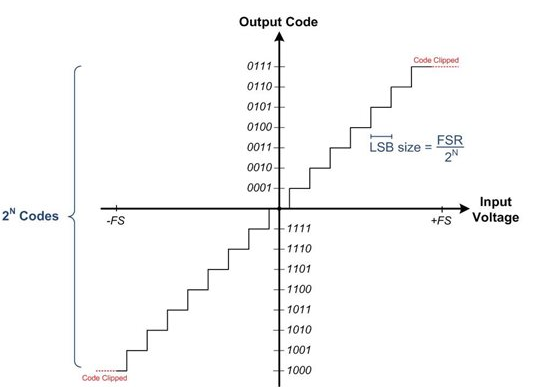

中,我將討論如何為各種應用執行這一數學轉換。在第1篇文章中,我將解釋如何將ADC代碼轉換回相應的電壓。在第2篇文章中,我將使用幾個應用示例來展示如何從測量的電壓計算感興趣的物理參數。 將代碼轉換為電壓 ADC采樣模擬信號提供表示輸入信號

2018-03-08 08:49:16 18113

18113

本文主要詳解PCB設計高速模擬輸入信號走線,首先介紹了PCB設計高速模擬輸入信號走線方法,其次闡述了九大關于PCB設計高速模擬輸入信號走線規則,具體的跟隨小編一起來了解一下。

2018-05-25 09:06:44 8394

8394

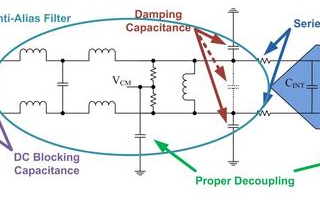

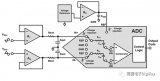

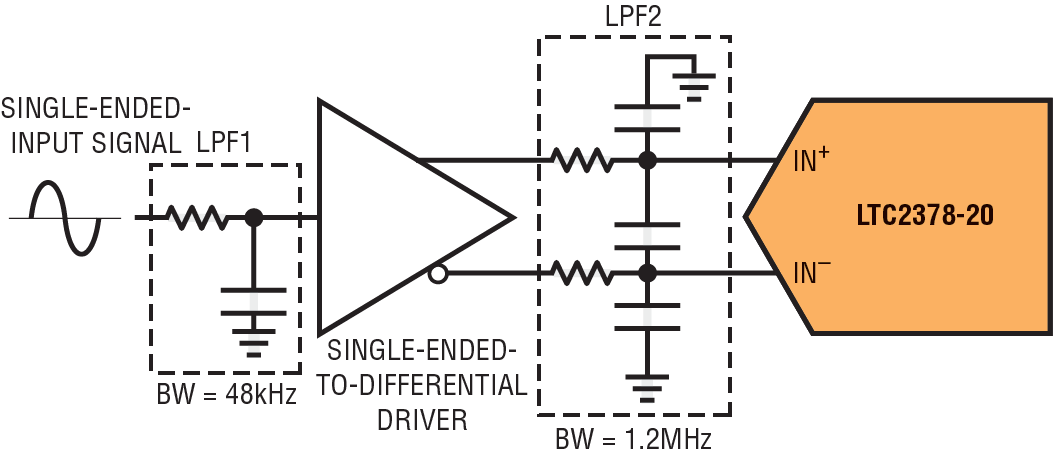

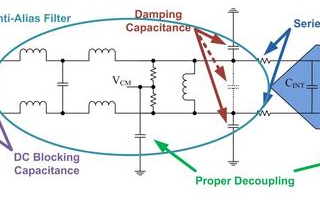

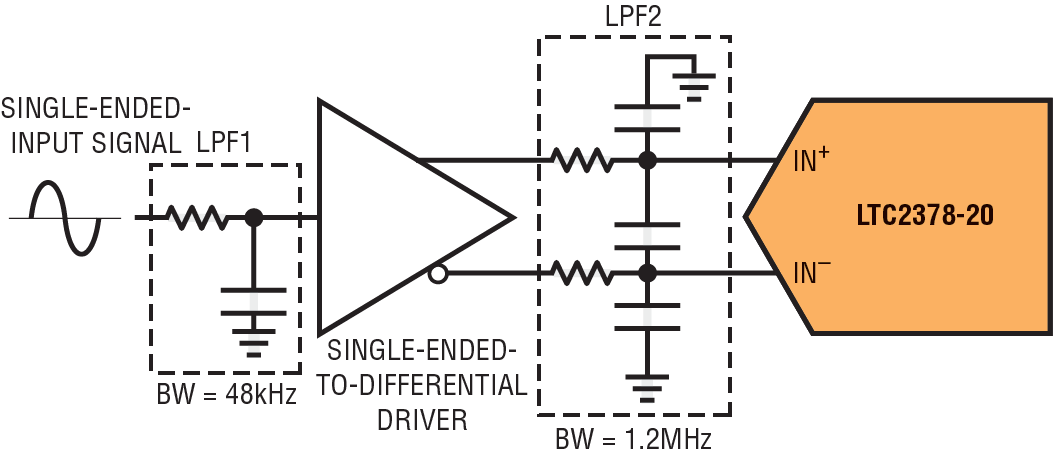

在考慮噪聲因素以及與ADC模擬輸入和共模電壓節點有關的其他失真情況時,自帶開關電容輸入采樣網絡的ADC同樣也可作為一個簡單的指標。圖1顯示集成驅動放大器和抗混疊濾波器(AAF)的典型ADC模擬輸入。

2020-09-02 10:01:02 921

921

采用高輸入頻率、高速模數轉換器(ADC)的系統設計是一項具挑戰性的任務。ADC輸入接口設計有6個主要條件:輸入阻抗、輸入驅動、帶寬、通帶平坦度、噪聲和失真。看看這里羅列的這六個條件,你都了解嗎?

2022-07-27 09:07:51 1548

1548 采用高輸入頻率、高速模數轉換器(ADC)的系統設計是一項具挑戰性的任務。ADC輸入接口設計有6個主要條件,你知道是那些嗎?

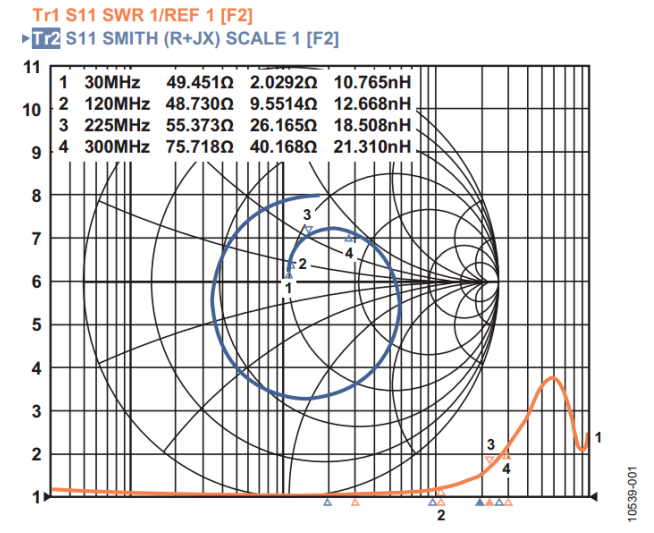

輸入阻抗

輸入阻抗是設計的特征阻抗。ADC的內部輸入阻抗取決于ADC

2023-12-18 06:13:51

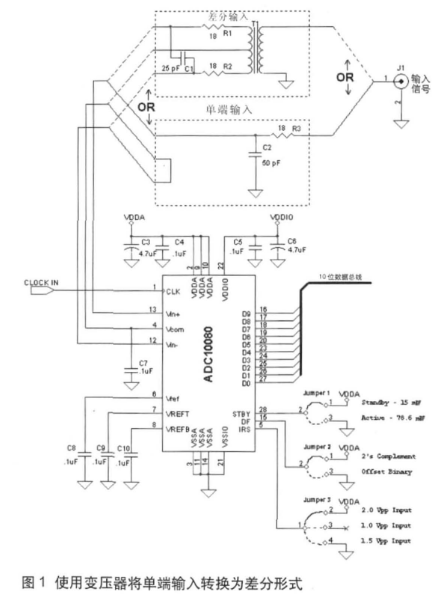

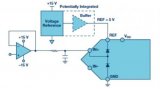

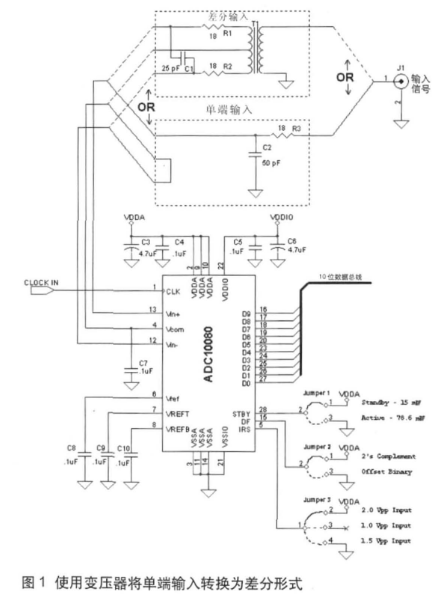

平衡-不平衡變壓器常用于將單端信號轉換為差分信號,其可在不增加噪聲的同時保持優良的失真指標。用于高速、差分輸入模數轉換器 (ADC) 的驅動器電路就是一個常見的例子。你有沒有考慮過采用差分放大器來替代 RF/IF 信號鏈路中的平衡-不平衡變壓器呢?如果沒有,那么你應該考慮一下。

2023-09-22 06:08:37

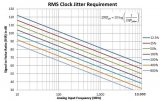

DN1013- 了解時鐘抖動對高速ADC的影響

2019-07-17 06:41:39

強大工具,使用戶能夠解決其中一個最關鍵、最棘手的轉換器問題。不過,這還遠遠不夠。你僅僅仿真了ADC的模擬部件。我們將在下個月談一談如何仿真轉換器的數字輸入/輸出。參考書目 “使用SAR ADC

2018-09-07 14:17:54

模擬數字轉換器輸入接口的設計考慮【作者】:Rob Reeder;【來源】:《電子與電腦》2010年02期【摘要】:<正>要針對高速模擬數字轉換器(ADC)設計輸入接口

2010-04-22 11:30:56

我有一個項目,用到AD7610BSTZ。一個現象是這樣的:我輸入的模擬量增加2MV,34401數字萬用表可以測得。但是ADC轉換的數字量并沒有變化。不知道為什么? 另外一個問題是:ADC數據轉換必須要用到采集保持IC嗎?如果不用會對采集精度有影響嗎?

2018-12-03 09:09:25

低Q電感或鐵氧體磁珠)

圖6中,通過在模擬輸入的每一側串聯一個低Q電感或鐵氧體磁珠,實現了輸入匹配。這是降低進入模擬輸入端的噪聲量的一種方法,需要時可采用。

緩沖ADC

緩沖輸入ADC(見圖7)更易

2023-12-18 07:42:00

(應用 輸入匹配,采用低Q電感或鐵氧體磁珠) 圖6中,通過在模擬輸入的每一側串聯一個低Q電感或鐵氧體磁珠,實現了輸入匹配。這是降低進入模擬輸入端的噪聲量的一種方法,需要時可采用。 緩沖ADC緩沖輸入ADC

2018-09-17 15:38:24

匹配,采用低Q電感或鐵氧體磁珠)圖6中,通過在模擬輸入的每一側串聯一個低Q電感或鐵氧體磁珠,實現了輸入匹配。這是降低進入模擬輸入端的噪聲量的一種方法,需要時可采用。緩沖ADC緩沖輸入ADC(見圖7

2018-10-18 11:23:57

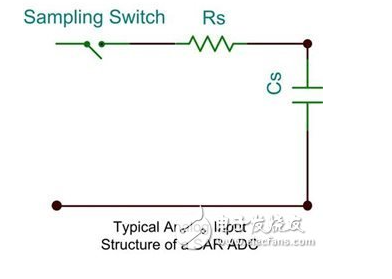

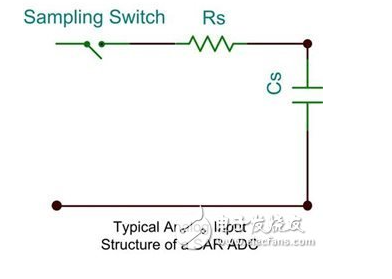

的外部前端設計直接連到ADC的內部采樣保持(SHA)網絡。圖1. 開關電容ADC這種方法有兩個缺點 輸入阻抗隨著時間和模式而變化; 第二是電荷注入會反射回ADC的模擬輸入端,可能導致濾波器建立問題。 當

2018-01-23 16:01:44

采用高輸入頻率、高速模數轉換器(ADC)的系統設計是一項具挑戰性的任務。ADC輸入接口設計有6個主要條件,你知道是那些嗎? 輸入阻抗輸入阻抗是設計的特征阻抗。ADC的內部輸入阻抗取決于ADC架構

2018-09-17 15:48:29

ADC實現與其前一代器件相同(或更好)的性能。現在,ADC的設計采取了多層面方法,其中:*采樣速度和模擬帶寬必須得到改善*性能必須與前一代相同或更好*納入更多片內數字處理功能來輔助數字接收邏輯下面將

2018-10-30 11:49:44

,系統對噪聲的敏感度就會提高一倍。因此,對于ADC設計,設計人員必須考慮一個常常被遺忘的噪聲源——系統電源。ADC屬于敏感型器件,每個輸入(即模擬、時鐘和電源輸入)均應平等對待,以便如數據手冊所述,實現

2019-12-11 18:12:18

13位,系統對噪聲的敏感度就會提高一倍。因此,對于ADC設計,設計人員必須考慮一個常常被遺忘的噪聲源——系統電源。ADC是敏感器件,為了實現數據手冊所述的最佳額定性能,應當同等看待模擬、時鐘和電源等

2018-09-30 16:31:56

,系統對噪聲的敏感度就會提高一倍。因此,對于ADC設計,設計人員必須考慮一個常常被遺忘的噪聲源——系統電源。ADC屬于敏感型器件,每個輸入(即模擬、時鐘和電源輸入)均應平等對待,以便如數據手冊所述,實現

2019-12-25 18:03:49

,系統對噪聲的敏感度就會提高一倍。因此,對于ADC設計,設計人員必須考慮一個常常被遺忘的噪聲源——系統電源。ADC屬于敏感型器件,每個輸入(即模擬、時鐘和電源輸入)均應平等對待,以便如數據手冊所述,實現

2018-08-27 17:45:35

,系統對噪聲的敏感度就會提高一倍。因此,對于ADC設計,設計人員必須考慮一個常常被遺忘的噪聲源——系統電源。ADC屬于敏感型器件,每個輸入(即模擬、時鐘和電源輸入)均應平等對待,以便如數據手冊所述,實現

2018-10-19 09:34:26

對噪聲的敏感度就會提高一倍。因此,對于ADC設計,設計人員必須考慮一個常常被遺忘的噪聲源——系統電源。ADC屬于敏感型器件,每個輸入(即模擬、時鐘和電源輸入)均應平等對待,以便如數據手冊所述,實現最佳

2018-10-15 09:49:24

能夠進行更精確的系統測量。然而,更高分辨率也意味著系統對噪聲更加敏感。系統分辨率每提高一位,例如從12位提高到13位,系統對噪聲的敏感度就會提高一倍。因此,對于ADC設計,設計人員必須考慮一個常常被遺忘

2018-11-21 17:14:38

輸入信號可以在變壓器的原邊或副邊端接,具體取決于系統對高速ADC增益平坦度和動態范圍的要求。寬帶變壓器是一個常用元件,能夠在較寬的頻率范圍內將單端信號轉換成差分信號,提供了一種快速、便捷的解決方案。本文

2021-10-23 11:10:35

們的建議,如有幫助,從精神到物質上雙重感謝自己之前用過普通ADC7606,SPI接口的。對高速ADC不太了解,有以下疑問,還請前輩們不吝賜教: 高速ADC與普通ADC接口不一樣,高速ADC能否用DSP驅動采集數據,還是只能用FPGA?

2018-12-10 09:37:39

描述此參考設計展示了高速放大器 LMH6554 執行單端至差動轉換以驅動高速模擬至數字轉換器 (ADC),同時保持卓越的噪聲和失真性能的能力。為交流和直流耦合應用顯示了連接到 ADS4449 四通

2018-08-03 06:00:28

輸出和RF輸入的安全間距是多少?【答】您好!需要考慮信號的頻率,功率等指標。【問】天線接口的輸入端在多層板中一定要挖空嗎?【答】不知道您指的挖空是哪部分挖空。通常設計是不建議挖空設計的。【問】RF板

2018-12-05 11:25:05

對于PCB高速板設計,器件布局是一個很重要的環節,要考慮電源的拓撲結構,還有高速部分、數字模擬部分的分割,作為初學者,因工作中需要這部分只是,論壇上是否有高手給指點一二,謝謝!

2019-08-29 04:36:01

在通信領域,隨著中頻(IF)頻率越來越高,了解輸入阻抗如何隨頻率而變化變得日益重要。本文解釋了為什么ADC輸入阻抗隨頻率而變化,以及為什么這是個電路設計難題;然后比較了確定輸入阻抗的兩種方法:利用

2019-06-05 06:19:12

假設您接到一項工作任務,設計一套由DSP與DAC與ADC等模擬器件組成的信號處理系統。如果您考慮到幾個重要因素,工作就會非常簡單。下面就來談談設計工作中應該考慮的這幾個因素。 詳細了解應用類型

2019-07-02 06:06:29

。例如,在下面提到的屏幕截圖中,ADC0_S9 存在于 J17 和 B14 中。那么我可以將這些 J17 和 B14 用于兩個不同的模擬輸入嗎?

2023-03-14 09:52:05

做出特定設計決策和權衡。最簡單的解決方案是匹配ADC輸入類型與信號源輸出配置。不過,源信號可能需要改變信號類型的調理,或者存在成本、功率或面積考慮因素,影響模擬輸入類型決策。我們來了解一下不同的可用模擬輸入

2018-10-18 11:25:47

你好!因為項目的原因,我需要選擇一個ADC芯片,希望ADC達到的要求包括:16路模擬單端輸入支持8個通道的模擬差分輸入采樣精度16位采樣速率250 kS/s

2019-02-26 10:59:44

信號)等,這時我們應該考慮通過相應的接口方式來很好地處理這個問題。下面就電路設計中7個常用的接口類型的關鍵點進行說明一下:(1)TTL電平接口:這個接口類型基本是老生常談的吧,從上大學學習模擬電路

2019-10-11 07:00:00

類型的調理,或者存在成本、功率或面積考慮因素,影響模擬輸入類型決策。我們來了解一下不同的可用模擬輸入類型。單端最簡單的模擬輸入類型是單端輸入。此時,信號從圖1. 單端單極性如果SAR ADC是雙極性單端

2018-10-17 10:24:38

了解一下不同的SAR ADC可用模擬輸入類型

2021-02-25 06:21:53

MHz。采用 G = 2的變壓器很難做到這一點,但是采用低輸出阻抗的放大器很容易實現。 問:在究竟選擇變壓器還是放大器來驅動ADC時,要考慮哪些因素呢?答:我們可以把這些因素歸結為6個參數,如下表所示

2018-12-14 09:27:03

關于數Gpbs高速存儲器接口設計的分析,看完你就懂了

2021-05-19 06:38:12

工程,已經使用Xilinx kintex-7實現這個ADC的接口數據接收驅動與后續信號處理。 由于AD9684需要外部觸發時鐘輸入,需要板卡上的外部基準時鐘輸入,通過FPGA內部的鎖相環倍頻產生一個

2019-12-06 15:33:22

在選擇高速A/D轉換器時,設計師必須考慮的因素是什么?用于評定A/D的最常用性能參數有哪些?

2021-04-14 06:34:22

三線接口邏輯電壓為2.25V,因此需要在單片機和ADC之間加一個緩沖器74LCX244進行電平轉換。6 結束語介紹了采用高速BICMOS技術的AT84AD001型模數轉換器,并將其應用在2 GHz數字

2019-04-30 07:00:11

通常需要比 LPF1 更寬的帶寬。該濾波器還有助于將緩沖器的噪聲貢獻降至最低。如何使用LTspice模擬 SAR ADC 模擬輸入?圖 1. 模擬放大器和 ADC 之間的接口有助于確定噪聲和建立時間之間的權衡。

2022-04-12 17:45:54

在設計 ADC 電路時,一個常見的問題是“如何在過壓條件下保護ADC 輸入”,那么 在過壓情形中可能出現哪些問題呢? 發生的頻率又是怎樣的呢? 有木有潛在的補救措施呢?

2021-03-11 07:36:43

大家好,我想給2 ADC模擬輸入使用AMUX與中斷。我想把選擇的頻道輸出顯示在液晶顯示器上。為此我編寫了程序。請在附件中找到。問題是我在LCD上只顯示1路輸出。我必須轉換為ISrtodo.c文件2個頻道。問候什維塔2MUXYADCY1.CYWRK.SARVEVE01.ZIP532.9 K

2019-08-13 09:13:47

; 麻省理工學院,1997年。Kester, Walt. 數據轉換手冊.ADI公司,2004年。MT-228: 高速ADC模擬輸入接口考慮因素Reeder, Rob. "高速無緩沖ADC的反沖

2018-11-01 11:25:01

怎樣通過STM32F103RCT6的ADC實現多個通道同時高速模擬信號采集并存儲呢?

2021-12-13 06:09:46

為主要誤差來源。

亞穩態高速ADC中造成轉換錯誤的一個常見原因是一種稱為亞穩態的現象。高速ADC在將模擬信號轉換為數字值的轉換過程中,往往會在不同階段使用多個梯級比較器。如果比較器無法確定模擬輸入是高于還是

2023-12-20 07:02:15

電池電壓的話,那么就必須保證ADC的模擬供電電壓5V一直存在,如果出于低功耗的考慮,5V需要關掉,那么在電池電壓和ADC之間需要使用一個隔離器件,否則有可能出現模擬供電電壓被抬升或者器件損壞的可能

2019-03-15 06:45:05

老生常談的吧,從上大學學習模擬電路、數字電路開始,對于一般的電路設計,TTL電平接口基本就脫不了“干系”!它的速度一般限制在30MHz以內,這是由于BJT的輸入端存在幾個pF的輸入電容的緣故(構成一個

2017-04-21 11:42:28

的輸入噪聲、電源噪聲、基準源噪聲、 數字接口饋通噪聲、ADC 芯片熱噪聲或量化噪聲。表1簡要列出了模擬濾波器與數字濾波器的優點和缺點。表1.模擬濾波器與數字濾波器模擬濾波器考慮抗混疊濾波器放在ADC

2018-10-16 18:45:40

圖1:USB協議的發展歷程——2019年發布USB 4.0為了讓您了解USB協議是否適合您的系統并滿足您的高速接口需求,我們為您列出了設計師通常需要考慮的六個關鍵問題:1:您的CPU或MCU的接口

2022-11-07 07:36:17

包含千兆采樣率ADC的系統設計會遇到許多復雜情況。面臨的主要挑戰包括時鐘驅動、模擬輸入級和高速數字接口。本文探討了如何才能克服這些挑戰,并給出了在千兆赫茲的速度下進行系統優化的方法。在討論中,時鐘

2019-05-30 05:00:04

:高級模擬IC設計工程師(ADC DAC 高速接口)-上海:方向一:高速ADC/DAC方向:1) 熟悉高速SAR、pipeline、或者高速DAC的設計,在其中一個領域有深入的研究和豐富的經驗。2

2017-07-19 16:18:50

高速ADC,什么是高速ADC

背景知識:

隨著計算機技術、通信技術和微電子技術的高速發展,大大促進了ADC技術的發展,ADC作為模擬量與數據量接

2010-03-24 13:28:01 9741

9741 設置高速ADC的共模輸入電壓范圍(中文)

對于包含基帶采樣、高速ADC的通信接收機,輸入共模電壓范圍(VCM)非常重要。特別是對于單電源供

2010-03-30 17:59:39 3883

3883

基本功能與概念: 模擬通道的組成 電壓基準源 分辨率等指標; ADC/DAC線性轉換關系 ADC/DAC與MPU接口

2011-04-07 16:49:00 111

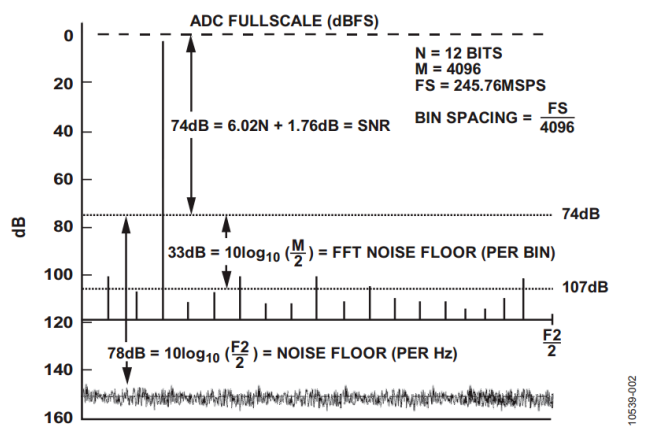

111 我的ADC沒有輸入信號,為什么輸出數據位仍在不斷變化?不熟悉高速ADC的人可能會認為:在靜態模擬輸入下,轉換器的數字輸出將保持恒定。

2012-06-01 15:15:53 3936

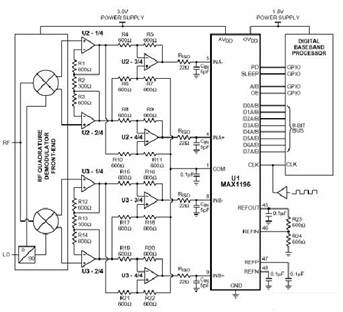

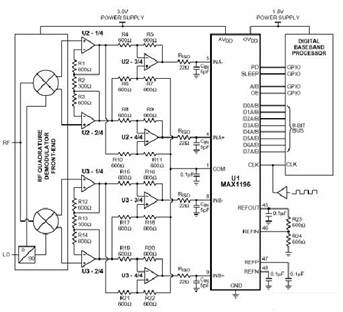

3936 高速ADC的性能特性對整個信號處理鏈路的設計影響巨大。系統設計師在考慮ADC對基帶影響的同時,還必須考慮對射頻(RF)和數字電路系統的影響。

2012-09-25 09:30:00 3000

3000

高速ADC的性能特性對整個信號處理鏈路的設計影響巨大。系統設計師在考慮ADC對基帶影響的同時,還必須考慮對射頻(RF)和數字電路系統的影響。

2012-11-13 10:34:22 1659

1659 采用高輸入頻率、高速模數轉換器(ADC)的系統設計是一項具挑戰性的任務。ADC輸入接口設計有6個主要條件:輸入阻抗、輸入驅動、帶寬、通帶平坦度、噪聲和失真。

2013-08-22 16:13:18 24

24 電子專業單片機相關知識學習教材資料之高速差分ADC驅動器設計考慮

2016-09-01 18:17:24 0

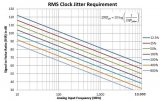

0 了解高速ADC時鐘抖動的影響將高速信號數字化到高分辨率要求仔細選擇一個時鐘,不會妥協模數轉換器的采樣性能(ADC)。 在這篇文章中,我們希望給讀者一個更好的了解時鐘抖動及其影響高速模數轉換器的性能

2017-05-15 15:20:59 13

13 任何通過時鐘電路進入ADC的噪聲都能直接到達輸出端。ADC中此電路的噪聲機制可認為是一個混頻器。當看到噪聲時,以這種方式考慮輸入就真正能洞察一切了。通過時鐘輸入進入ADC的噪聲頻率將混入模擬輸入信號,并出現在轉換器輸出端的FFT中。

2017-09-14 17:17:12 8

8 本文介紹了模擬信號中高斯噪聲對ADC輸入的影響。

2017-11-23 15:34:21 11

11 當ADC時鐘輸入時,都需要考慮哪些因素呢?如何做才能使ADC充分發揮芯片的性能呢?讓ADI公司數字視頻處理部高級工程師Ian Beavers告訴你吧! 為了充分發揮芯片的性能,應利用一個差分信號驅動

2017-12-19 04:10:01 4981

4981

在設計ADC電路時,一個常見的問題是如何在過壓條件下保護ADC輸入。ADC輸入的保護具有許多情況和潛在解決方案。所有供應商的ADC都在此方面具有相似需求。本文將深入分析過壓情形中可能出現的問題、發生

2018-02-21 12:35:00 8730

8730

一文了解高速差分ADC驅動器設計考慮

2018-04-08 14:07:08 30

30 幾種已知的方法用于設計具有電阻性負載終止的無源電感電容器(LC)濾波器。然而,當LC濾波器被用來驅動高速模擬數字轉換器(ADC)的模擬輸入引腳時,必須特別考慮ADC輸入阻抗。不考慮ADC輸入阻抗常常

2018-05-16 14:06:38 13

13 該應用報告討論了在高速流水線模數轉換器(ADC)的模擬輸入中無源和有源接口的性能相關方面。該報告簡化了許多可能性分為兩大類:無源和有源接口電路。該報告的第一部分給出了緩沖和無緩沖ADC輸入電路

2018-05-16 16:48:12 7

7 本應用注釋討論了如何通過設計正確的時鐘電路和良好的模擬輸入網絡,來優化高速流水線ADC的性能,以及如何將ADC的高速不失真的數據輸送到FPGA或ASIC上。

2018-05-18 10:34:32 10

10 本應用注釋討論了如何通過設計正確的時鐘電路和良好的模擬輸入網絡,來優化高速流水線ADC的性能,以及如何將ADC的高速不失真的數據輸送到FPGA或ASIC上。

2018-05-18 10:41:22 0

0 許多采用一個精準模數轉換器進行信號數字化處理的系統都需要在信號源和 ADC 之間布設某種信號調理電路。除了它的其他功能之外,該電路還必須準確地驅動 ADC 的輸入。由于同時需要高性能和高速度以處理

2018-06-04 13:47:00 3864

3864 該應用報告討論了在連接通用放大器和模數轉換器時必須考慮的各種考慮因素。該報告討論了帶寬,分辨率,模擬ADC輸入驅動器和電源考慮這兩個部分。

2018-05-28 09:46:12 19

19 在信號源和 ADC 之間布設某種信號調理電路。除了它的其他功能之外,該電路還必須準確地驅動 ADC 的輸入。由于同時需要高性能和高速度以處理 ADC 輸入電流,因而會提出一項實質性的額外設計挑戰。

2018-06-28 09:23:00 5143

5143

包含千兆采樣率ADC的系統設計會遇到許多復雜情況。面臨的主要挑戰包括時鐘驅動、模擬輸入級和高速數字接口。本文探討了如何才能克服這些挑戰,并給出了在千兆赫茲的速度下進行系統優化的方法。在討論中,時鐘

2019-05-30 08:18:00 3781

3781

了解模/數轉換背后過程的更多信息,以及選擇和使用ADC設計時需要考慮的重要技術指標和條件。

2018-10-09 03:49:00 5468

5468 器件預期性能的最大化。一個頗具挑戰性的輸入條件是:對ADC輸入模擬信號進行測量、驅動和接口連接。本文將探討一些對于高速 ADC進行有效接口連接的技術,從而使ADC實現性能最佳化。

2020-04-12 11:18:46 3069

3069

來源:羅姆半導體社區? 模擬系統設計不僅需要選擇正確的IC元件,還必須準確地預測這些元件在系統內的相互影響。從這點來看,模數轉換器的設計是一個巨大挑戰,因為它具有必須在系統級加以考慮的各種不同的輸入

2022-11-15 15:52:12 428

428 MT-228:高速ADC模擬輸入接口考慮

2021-03-21 00:23:19 7

7 DN1013-了解時鐘抖動對高速ADC的影響

2021-05-11 18:22:19 0

0 MS-2124:了解高速ADC的交流行為

2021-05-17 19:16:54 0

0 AVR教程---模擬比較器和ADC接口(電源技術投稿格式要求)-該文檔為AVR教程---模擬比較器和ADC接口總結文檔,是一份不錯的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-23 13:42:16 3

3 列文章探討ADC的基礎知識及其類型、應用。本文將探討SAR ADC的輸入驅動難題。 許多數據采集、工業控制和儀表應用都需要超高速模數轉換器 (ADC),而逐次逼近寄存器(SAR) 轉換器則能完全滿足這一要求。然而,我們必須確保SAR轉換器周圍的外部電路也能勝任這

2021-11-05 14:17:41 1778

1778

一個逐次逼近寄存器 (SAR) 模數轉換器 (ADC) 通常需要一個驅動器來驅動其模擬輸入,以獲得所需的精度效果。但是在較低數據吞吐量和較低分辨率應用中,你也許不需要驅動器。讓我們來看一看SAR ADC的采樣過程和模擬輸入結構來了解驅動器的要求。

2022-01-28 09:32:00 2769

2769

使用檢測算法來評估高精度模數轉換器(ADC)在太空中的表現,將ADC置于一組實際工作條件下,以符合其實際使用情況的方式測試器件。應用此方法要求ADC在其輸入電壓范圍的中間使用模擬輸入工作。這種格式

2022-11-14 16:44:40 573

573 本文介紹了在低功耗系統中降低功耗同時保持測量和監控應用所需的精度的時序因素和解決方案。它解釋了當所選ADC是逐次逼近寄存器(SAR)ADC時影響時序的因素。對于Σ-Δ(∑-Δ)架構,時序考慮因素有所不同(請參閱本系列文章的第1部分)。本文探討了模擬前端時序、ADC時序和數字接口時序中的信號鏈考慮因素。

2022-12-13 11:20:18 1057

1057

隨著ADC分辨率和采樣速率的不斷提高,模擬輸入的驅動器電路(而不是ADC本身)日益成為決定整體電路精度的限制因素。除了用于噪聲輸入信號的簡單1極點RC低通濾波器(LPF1)(圖1)之外,緩沖器

2023-01-03 16:39:12 1420

1420

在采樣或子采樣接收器設計中使用高性能奈奎斯特模數轉換器(ADC)時,RF設計人員需要了解ADC在小信號和大信號輸入下的噪聲性能。接收器必須滿足這兩個信號電平極端下的靈敏度和阻塞(高電平干擾)要求

2023-03-02 15:15:10 930

930

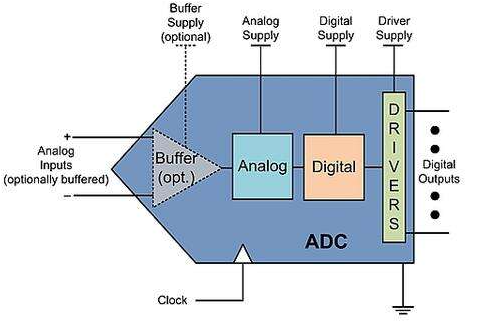

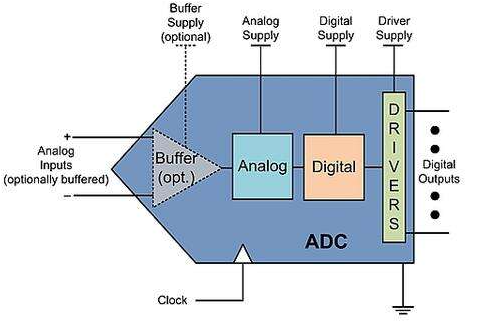

在討論如何驅動各種電源域之前,讓我們回顧一下高速ADC上通常可以找到的電源輸入。有一個可選的輸入緩沖電源域(并非在所有ADC上)、一個模擬電源域、一個數字電源域和一個驅動器電源域。

2023-06-30 16:40:35 757

757

采用高速模數轉換器(ADC)的系統設計 非常困難,本筆記簡要介紹基本設計考慮。

2023-07-03 15:10:45 0

0 點擊上方 藍字 關注我們 ADC硬件特性分析 首先必須通過datasheet分析其核心參數、接口定義和時序要求。ADC9481的采樣率為250MSPS,精度8bit。其原理結構圖如下: 主要引腳說明

2023-08-28 14:30:01 956

956 ,我們來了解一下ADC的基本原理。ADC的輸入是一個連續模擬信號,它通過采樣和量化兩個步驟轉換為離散的數字信號。采樣過程將模擬信號按照一定的頻率進行抽樣,將其離散化。量化過程將每個采樣值映射為最接近的數字值。這個數字值的精度決定了

2023-11-09 09:50:53 402

402

電子發燒友App

電子發燒友App

評論