我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是與FPGA獨(dú)立的,只是集成在了一起呢,還是占用了FPGA的資源來(lái)形成一個(gè)RAM?如果我以ROM的形式調(diào)用該IP核,在

2013-01-10 17:19:11

可編程邏輯業(yè)對(duì)微處理器核的報(bào)道層出不窮,包括與ARM和MIPS的協(xié)議,這些討論已經(jīng)持續(xù)了數(shù)年。然而,討論的主題大體上沒(méi)什么改變,諸如采用硬核還是軟核?采用供應(yīng)商的特定標(biāo)準(zhǔn)還是行業(yè)標(biāo)準(zhǔn)?這些核如何用來(lái)全方位地支持生態(tài)系統(tǒng)?如何根據(jù)成本、功耗和性能來(lái)選擇微處理器?如何根據(jù)應(yīng)用來(lái)選擇核?

2019-08-08 06:43:03

傳統(tǒng)的、基于通用DSP處理器并運(yùn)行由C語(yǔ)言開(kāi)發(fā)的算法的高性能DSP平臺(tái),正在朝著使用FPGA預(yù)處理器和/或協(xié)處理器的方向發(fā)展。這一最新發(fā)展能夠?yàn)楫a(chǎn)品提供巨大的性能、功耗和成本優(yōu)勢(shì)。

2011-09-29 16:28:38

有誰(shuí)知道現(xiàn)在國(guó)內(nèi)外有哪些公司賣(mài)FPGA的圖像處理相關(guān)的IP核?

2015-04-28 21:34:24

是具有知識(shí)產(chǎn)權(quán)核的集成電路芯核總稱(chēng),是經(jīng)過(guò)反復(fù)驗(yàn)證過(guò)的、具有特定功能的宏模塊,與芯片制造工藝無(wú)關(guān),可以移植到不同的半導(dǎo)體工藝中。到了SOC 階段,IP 核設(shè)計(jì)已成為ASIC 電路設(shè)計(jì)公司和FPGA

2018-09-03 11:03:27

FPGA硬核與軟核處理器有什么區(qū)別和聯(lián)系?

2023-05-30 20:36:48

如何根據(jù)成本、功耗和性能來(lái)選擇微處理器?FPGA結(jié)構(gòu)中硬核和軟核的特點(diǎn)是什么?處理器IP有什么重要性?

2021-04-08 06:16:37

你好,我已經(jīng)在micrlaze中建立了用于SPI ip核心的EDK平臺(tái)。我正在使用Spartan6 FPGA以及如何使用Isim模擬edk中的SPI ip core以及如何驗(yàn)證spi ipcore。謝謝&問(wèn)候Madhu B

2020-04-03 09:57:48

處理器中斷處理的過(guò)程是怎樣的?處理器在讀內(nèi)存的過(guò)程中,CPU核、cache、MMU如何協(xié)同工作?

2021-10-18 08:57:48

龍芯1B處理器用戶手冊(cè),對(duì)龍芯有點(diǎn)興趣的朋友可以看看。

2011-09-29 15:42:40

龍芯1B 芯片是基于GS232處理器核的片上系統(tǒng), 具有高性價(jià)比,可廣泛應(yīng)用于工業(yè)控制、家庭網(wǎng)關(guān)、信息家電 、醫(yī)療器械和安全應(yīng)用等領(lǐng)域。1B采用SMIC0.13微米工藝實(shí)現(xiàn),采用Wire Bond

2021-07-23 08:36:40

迅為iTOP-LS2K0500開(kāi)發(fā)采用龍芯LS2K0500處理器,基于龍芯自主指令系統(tǒng)(LoongArch)架構(gòu),片內(nèi)集成64位LA264處理器核、32位DDR3控制器、2D GPU、DVO顯示接口

2023-03-23 10:03:14

,其性能相當(dāng)于桌面級(jí)英特爾處理器i5-7200U,支持統(tǒng)信UOS、麒麟U(xiǎn)OS等國(guó)產(chǎn)操作系統(tǒng)。緊接著龍芯3D5000完成初樣芯片驗(yàn)證,純國(guó)產(chǎn)服務(wù)器芯片即將誕生!據(jù)悉,3D5000(12nm)芯片首次采用

2023-02-15 09:43:59

片上系統(tǒng)SoC(Sytem。n Chip),即是將整個(gè)系統(tǒng)集成在單個(gè)的芯片上。與傳統(tǒng)的板級(jí)電路不同,SoC集成的完整系統(tǒng)一般包括系統(tǒng)級(jí)芯片控制邏輯模塊、微處理器/微控制器CPU內(nèi)核模塊、數(shù)字信號(hào)

2019-08-30 08:27:15

片上系統(tǒng)SoC(Sytem。n Chip),即是將整個(gè)系統(tǒng)集成在單個(gè)的芯片上。與傳統(tǒng)的板級(jí)電路不同,SoC集成的完整系統(tǒng)一般包括系統(tǒng)級(jí)芯片控制邏輯模塊、微處理器/微控制器CPU內(nèi)核模塊、數(shù)字信號(hào)

2019-09-02 07:06:58

龍芯處理器iTOP-2K1000開(kāi)發(fā)板安裝python安裝完成如下圖所示:

2023-01-31 11:21:57

基于龍芯自主指令系統(tǒng)(LoongArch)架構(gòu),片內(nèi)集成64位LA264處理器核、32位DDR3控制器、2D GPU、DVO顯示接口、兩路PCle2.0、兩路SATA2.0、四核USB2.0、一路USB3.0、兩路GMAC、PCI總線、彩色黑白打印接口、HDA及其他常用接口

2023-03-24 16:28:54

ARM公司開(kāi)發(fā)了很多系列的ARM處理器核,目前最新的系列已經(jīng)是ARM11了,而ARM6核及更早的系列已經(jīng)很罕見(jiàn)了,ARM7以后的核也不是都獲得廣泛應(yīng)用。目前,應(yīng)用比較多的是ARM7系列、ARM9系列

2019-07-23 07:08:18

Banana Pi推出基于龍芯2K1000LA處理器的信創(chuàng)工業(yè)控制開(kāi)發(fā)平臺(tái):BPI-5202信創(chuàng)工業(yè)控制開(kāi)發(fā)平臺(tái)

BPI-5202 龍芯2K1000LA 信創(chuàng)工業(yè)控制開(kāi)發(fā)平臺(tái)

1.1 工控機(jī)

2023-09-04 12:30:42

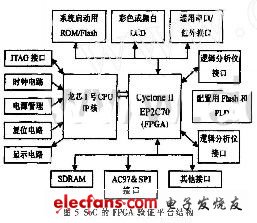

在其業(yè)內(nèi)領(lǐng)先的低成本Cyclone TM FPGA系列和Nios軟核嵌入式處理器成功的基礎(chǔ)上,Altera現(xiàn)在推出了第二代產(chǎn)品系列。Cyclone II器件為用戶提供更高的邏輯密度和新增硬件性能,比

2019-07-18 07:43:25

,國(guó)際上只有I-Shou大學(xué)的Yu-Jung Huang等人設(shè)計(jì)了可驅(qū)動(dòng)不同規(guī)模LCD的驅(qū)動(dòng)電路IP核,通過(guò)在系統(tǒng)中植入嵌入式微處理器來(lái)實(shí)現(xiàn)這一功能。但是,這種嵌入式微處理器使系統(tǒng)更復(fù)雜,而且成本更高

2012-08-12 12:28:42

NioslI嵌入式處理器是A1tera公司提出的SOPC解決方案,是一種用戶可隨意配置和構(gòu)建的32位嵌入式處理器,結(jié)合豐富的外設(shè)可快速、靈活地構(gòu)建功能強(qiáng)大的SOPC系統(tǒng)。Altera公司提供了一些

2019-08-06 08:29:14

本期文章目錄一個(gè)小型RISC-V開(kāi)源處理器核介紹!#SOC#FPGA#RISC-V點(diǎn)擊閱讀數(shù)字積木從零開(kāi)始寫(xiě)RISC-V處理器(超詳細(xì))#RISC-V點(diǎn)擊閱讀數(shù)字積木為什么說(shuō)模擬工程...

2021-07-23 09:42:00

基于NiosII微處理器的SOPC系統(tǒng)與基于MicroBlaze微處理器的SOPC系統(tǒng)等。它們功能強(qiáng)大,而且配有相應(yīng)的開(kāi)發(fā)環(huán)境與系統(tǒng)集成的IP核。但每個(gè)器件廠商的SOPC系統(tǒng)只適用于自己開(kāi)發(fā)的器件,同時(shí)需要支付相應(yīng)的使用費(fèi)用且沒(méi)有源代碼,所以在學(xué)習(xí)以及普通設(shè)計(jì)開(kāi)發(fā)驗(yàn)證中使用起來(lái)會(huì)有諸多的不便。

2019-10-11 07:07:07

`Xilinx系列FPGA芯片IP核詳解(完整高清書(shū)簽版)`

2017-06-06 13:15:16

我用quartus II調(diào)用modelsim仿真fft ip核,仿真結(jié)束后我想驗(yàn)證下數(shù)據(jù)是否正確,結(jié)果是:我用matlab生成同樣的整形數(shù)據(jù),然后用modelsim仿出的結(jié)果txt文件與用

2012-09-20 12:48:37

有沒(méi)有大神可以提供xilinx FPGA的FFT IP核的調(diào)用的verilog 的參考程序,最近在學(xué)習(xí)FFT的IP核的使用,但是仿真結(jié)果有問(wèn)題,所以想找些參考設(shè)計(jì),謝謝

2016-12-25 17:05:38

日前,龍芯展示了新版國(guó)產(chǎn)自主筆記本電腦。該P(yáng)C產(chǎn)品運(yùn)行最新的龍芯3A3000處理器,系統(tǒng)是基于深度Linux開(kāi)發(fā)版打造的龍芯鏡像,集成深度應(yīng)用商店。核心CPU參數(shù)上,龍芯3A3000基于中芯28nm

2017-09-19 08:54:26

龍芯中科龍芯中科面向國(guó)家信息化建設(shè)需求,面向國(guó)際信息技術(shù)前沿,以創(chuàng)新發(fā)展為主題、以產(chǎn)業(yè)發(fā)展為主線、以體系建設(shè)為目標(biāo),堅(jiān)持自主創(chuàng)新,全面掌握CPU指令系統(tǒng)、處理器IP核、操作系統(tǒng)等計(jì)算機(jī)核心技術(shù),打造

2022-12-12 09:51:08

直播簡(jiǎn)介:慧睿思通于12月9日成為國(guó)內(nèi)第一家成功將OpenHarmony輕量系統(tǒng)移植到龍芯平臺(tái)的公司。本次突破得益于慧睿思通研發(fā)團(tuán)隊(duì)和龍芯廣東本地團(tuán)隊(duì)的協(xié)作,對(duì)應(yīng)的是龍芯1C300處理器平臺(tái),為構(gòu)建

2021-12-20 16:05:37

講,主要通過(guò)演示FPGA數(shù)字邏輯設(shè)計(jì)中除Verilog代碼方式設(shè)計(jì)外另外一種最常用的設(shè)計(jì)方式——使用IP核進(jìn)行系統(tǒng)設(shè)計(jì)。本教程講解了如何在Quartus II軟件中調(diào)用一個(gè)基本的免費(fèi)IP核——計(jì)數(shù)器IP核

2015-09-22 14:06:56

個(gè)能執(zhí)行幾條指令的處理模塊ip核。它的功能將很簡(jiǎn)單。三、把處理器的框圖構(gòu)建出來(lái),分模塊寫(xiě)出較為完善的IP核。其中存儲(chǔ)器暫時(shí)不用SDRAM,寫(xiě)驅(qū)動(dòng)IP還是有難度的。四、如果時(shí)間允許,給寫(xiě)好的處理器擴(kuò)展外部模塊如SDRAM,VGA,TFT等等。五、給FPGA燒寫(xiě)nios系統(tǒng)。

2017-07-25 18:02:36

多個(gè)蝶形處理器并行運(yùn)算,能對(duì)較高的數(shù)據(jù)采樣率進(jìn)行運(yùn)算,但其硬件規(guī)模較大,當(dāng)在FPGA上要實(shí)現(xiàn)較大點(diǎn)數(shù)的FFT時(shí)較為困難。(2)串行方法,采用一個(gè)蝶形處理器完成運(yùn)算,使用的邏輯資源較少,但運(yùn)算速度較慢

2019-07-03 07:56:53

可編程邏輯業(yè)對(duì)微處理器核的報(bào)道層出不窮,包括與ARM和MIPS的協(xié)議,這些討論已經(jīng)持續(xù)了數(shù)年。然而,討論的主題大體上沒(méi)什么改變,諸如采用硬核還是軟核?采用供應(yīng)商的特定標(biāo)準(zhǔn)還是行業(yè)標(biāo)準(zhǔn)?這些核如何用來(lái)全方位地支持生態(tài)系統(tǒng)?如何根據(jù)成本、功耗和性能來(lái)選擇微處理器?如何根據(jù)應(yīng)用來(lái)選擇核?

2019-08-13 07:52:46

本文介紹在使用Arm DesignStart計(jì)劃開(kāi)放的處理器核搭建SoC并通過(guò)FPGA實(shí)現(xiàn)的過(guò)程中所用工具軟件(不介紹如何操作),理清“軟件編程”和“硬件編程”的概念,熟悉SoC設(shè)計(jì)的流程。軟硬件

2022-04-01 17:48:02

DesignStart時(shí)間軸ARM Cortex-M0和Cortex-M3是全球使用最廣泛的ARM處理器核,合計(jì)出貨量超過(guò)200億。DesignStart包括多個(gè)版本,如面向個(gè)人的Eval和FPGA版本,面向

2022-07-27 16:58:55

架構(gòu)雙核ARM Cortex-A9 處理器:一個(gè)應(yīng)用級(jí)的處理器,能運(yùn)行完整的像Linux 這樣的操作系統(tǒng)傳統(tǒng)的現(xiàn)場(chǎng)可編程門(mén)陣列(Field Programmable Gate Array,FPGA

2021-07-23 09:23:34

支持。龍芯 2K0500 開(kāi)發(fā)板龍芯2K0500是一款高集成度處理器芯片,主要面向工控互聯(lián)網(wǎng)應(yīng)用、打印終端、BMC等應(yīng)用場(chǎng)景。片內(nèi)集成64位LA264處理器核、32位DDR3控制器、2D GPU、DVO

2022-10-11 18:27:24

國(guó)產(chǎn)工業(yè)處理器,龍芯2K1000核心板,可以實(shí)現(xiàn)全國(guó)產(chǎn)化方案可實(shí)現(xiàn)100%國(guó)產(chǎn)元器件方案,國(guó)產(chǎn)處理器迅為2k1000開(kāi)發(fā)板采用龍芯 2k1000處理器,處理器集成 2 個(gè) GS264 處理器核,主頻

2022-07-19 15:10:42

基于FPGA的IP核8051上實(shí)現(xiàn)TCPIP的設(shè)計(jì)

2012-08-06 12:18:28

我畢業(yè)設(shè)計(jì)要做一個(gè)基于FPGA的IP核的DDS信號(hào)發(fā)生器,但是我不會(huì)用DDS的IP核,有沒(méi)有好人能發(fā)我一份資料如何用IP核的呀。我的瀏覽器下載不了網(wǎng)站上的資料,所以只能發(fā)帖求幫忙了。

2015-03-10 11:46:40

基于FPGA的FFT和IFFT IP核應(yīng)用實(shí)例AT7_Xilinx開(kāi)發(fā)板(USB3.0+LVDS)資料共享騰訊鏈接:https://share.weiyun.com/5GQyKKc百度網(wǎng)盤(pán)鏈接

2019-08-10 14:30:03

的RISC CPU設(shè)計(jì)是一個(gè)從抽象到具體的過(guò)程,本文根據(jù)FPGA的結(jié)構(gòu)特點(diǎn),圍繞在FPGA上設(shè)計(jì)實(shí)現(xiàn)八位微處理器軟核設(shè)計(jì)方法進(jìn)行探討,研究了片上系統(tǒng)的設(shè)計(jì)方法和設(shè)計(jì)復(fù)用技術(shù),并給出了指令集和其調(diào)試方法,提出

2021-07-11 08:00:01

核的分類(lèi)和特點(diǎn)是什么?基于IP核的FPGA設(shè)計(jì)方法是什么?

2021-05-08 07:07:01

兩個(gè)方面的內(nèi)容:IP核生成和IP核復(fù)用。文中采用IP核復(fù)用方法和SOC技術(shù)基于AVR 8位微處理器AT90S1200IP Core設(shè)計(jì)專(zhuān)用PLC微處理器FSPLCSOC模塊。

2019-07-26 06:19:34

SOC,其中FPGA SOC選用的是APEX20K,MCU SOC選用的是具有ARM IP核的ARM7 TDMI-S 微處理器。該智能傳感器的樣機(jī)已經(jīng)完成。FPGA 的片上芯片經(jīng)硬件仿真測(cè)試,其A/D采樣

2008-08-26 09:38:34

)。為此.我們利用VHDL設(shè)計(jì)一種嵌入式RISC8微處理器及應(yīng)用芯片.設(shè)計(jì)后的IP核下載到FPGA(Field Programmable Gate Array.現(xiàn)場(chǎng)可編程門(mén)陣列)芯片上做驗(yàn)證,并在

2021-09-01 19:32:45

如何調(diào)試Zed板702的雙核臂處理器。

2019-10-30 09:29:20

可編程門(mén)陣列FPGA具有可編程特性,用戶根據(jù)特定的應(yīng)用定制電路結(jié)構(gòu),因此其處理速度大大超過(guò)通用處理器。與ASIC相比,FPGA的缺點(diǎn)是在提供靈活的可編程同時(shí),則以芯片的面積、功耗和速度做為代價(jià)。

2019-09-03 07:44:22

嵌入式龍芯處理器HS3210 User-Manual HS3210系列芯片是高集成度的高性能系統(tǒng)級(jí)芯片(System-On-Chip),能夠滿足家庭網(wǎng)關(guān)(SOHO/SME

2009-11-23 11:48:02

我想將8位軟核處理器與EMAC連接以進(jìn)行TCP / IP通信。請(qǐng)建議我哪個(gè)IP核必須去EMAC控制器。如果可能的話,請(qǐng)給我指導(dǎo)其實(shí)施TCP / IP的參考設(shè)計(jì)。以上來(lái)自于谷歌翻譯以下為原文I

2019-01-24 10:58:20

你好 我對(duì)Saprtan 3E有一些疑問(wèn)。 (1)當(dāng)試圖將軟處理器嵌入到傳統(tǒng)FPGA中時(shí),主要問(wèn)題是什么以及如何解決它。(2)Saprtan 3E如何解決這個(gè)問(wèn)題,因?yàn)樗枰獙④?b class="flag-6" style="color: red">核處理器嵌入到傳統(tǒng)

2019-06-05 07:48:29

的其它設(shè)計(jì)部分盡量不相關(guān)。為了滿足上述的要求, 在FPGA中嵌入一個(gè)比較理想的選擇, 而這個(gè)即通用又控制簡(jiǎn)單的IP核最好選擇8051微處理器。

2019-08-26 06:27:15

一個(gè)以上的嵌入式處理器IP(Intellectual Property,知識(shí)產(chǎn)權(quán))核,具有小容量片內(nèi)高速RAM資源,豐富的IP核資源可供靈活選擇,有足夠的片上可編程邏輯資源,處理器高速接口和FPGA

2020-03-13 07:03:54

,龍芯仍然是唯一能支持多路服務(wù)器的自主CPU。在最近國(guó)外CPU企業(yè)對(duì)中國(guó)企業(yè)的CPU技術(shù)授權(quán)中,支持多路服務(wù)器的技術(shù)受美國(guó)政府限制還是不能給中國(guó)的。龍芯3A1000的處理器核沿襲了龍芯2E和龍芯2F

2016-10-28 09:58:23

深圳明德?lián)P科技教育有限公司,是一家高科技民營(yíng)公司,主營(yíng)業(yè)務(wù)為IC/FPGA設(shè)計(jì)、開(kāi)發(fā)、培訓(xùn)。旗下包括廣州健飛集成電路設(shè)計(jì)有限公司(辦公設(shè)在廣州市南沙自貿(mào)區(qū))、龍核集成電路IP核交易平臺(tái)。明德?lián)P

2018-06-02 17:35:40

處理器間通信和中斷方面仍需進(jìn)一步的研究。本文在處理器間通信和中斷控制方面進(jìn)行了深入的研究。MicroBlaze是一個(gè)被優(yōu)化過(guò)的可以在Xilinx公司FPGA中運(yùn)行的軟核處理器,可以和其他外設(shè)IP核一起完成

2021-03-16 07:44:35

本文介紹了一種基于FPGA及NiosII軟核處理器與TFT-LCD接口的方法。它直接采用CPU對(duì)存貯器的讀寫(xiě),實(shí)現(xiàn)了對(duì)TFT-LCD屏的實(shí)時(shí)操作。它具有直接、有效和速度快等特點(diǎn)。該設(shè)計(jì)使CPU對(duì)TFT-LCD的控制極其簡(jiǎn)單化。

2021-05-08 07:21:11

本文根據(jù)FPGA的結(jié)構(gòu)特點(diǎn),圍繞在FPGA上設(shè)計(jì)實(shí)現(xiàn)八位微處理器軟核設(shè)計(jì)方法進(jìn)行探討,研究了片上系統(tǒng)的設(shè)計(jì)方法和設(shè)計(jì)復(fù)用技術(shù),并給出了指令集和其調(diào)試方法,提出了一種基于FPGA的微處理器的IP的設(shè)計(jì)方法。

2021-04-29 06:38:37

這是我們一個(gè)小比賽的題面:設(shè)計(jì)一個(gè)簡(jiǎn)易的電子計(jì)算器電路,包括輸入數(shù)據(jù)處理電路,算數(shù)運(yùn)算電路(包含加法、減法、乘法、除法等算數(shù)運(yùn)算),運(yùn)算結(jié)果處理電路,所有運(yùn)算電路的設(shè)計(jì)均不可使用IP核及查找表進(jìn)行

2018-04-06 20:46:11

賽靈思Zynq-7000可擴(kuò)展處理平臺(tái)(EPP)將雙ARM Cortex-A9 MPCore處理器系統(tǒng)與可編程邏輯和硬IP外設(shè)緊密集成在一起,提供了靈活性、可配置性和性能的完美組合。圍繞其剛剛推出

2019-05-16 10:44:42

處理器上有更多的選擇,Altera公司宣布,F(xiàn)reescale將為SOPC Builder工具推出32位V1 ColdFire軟核。為迅速方便的使用Altera? Cyclone? III FPGA建立

2008-06-17 11:40:12

設(shè)計(jì)周期,提高設(shè)計(jì)質(zhì)量。現(xiàn)場(chǎng)可編程門(mén)陣列FPGA具有可編程特性,用戶根據(jù)特定的應(yīng)用定制電路結(jié)構(gòu),因此其處理速度大大超過(guò)通用處理器。與ASIC相比,FPGA的缺點(diǎn)是在提供靈活的可編程同時(shí),則以芯片的面積、功耗和速度做為代價(jià)。

2019-07-29 08:33:45

包含一個(gè)以上的嵌入式處理器IP(Intellectual Property,知識(shí)產(chǎn)權(quán))核,具有小容量片內(nèi)高速RAM資源,豐富的IP核資源可供靈活選擇,有足夠的片上可編程邏輯資源,處理器高速接口和FPGA編程接口共用或并存,可能包含部分可編程模擬電路,單芯片、低功耗[1]。

2019-08-23 08:18:51

的RFID系統(tǒng),用FPGA原型驗(yàn)證平臺(tái)替代上述的電子標(biāo)簽芯片(Tag),使用上層的應(yīng)用軟件開(kāi)發(fā)驗(yàn)證激勵(lì)。通過(guò)閱讀器與FPGA原型驗(yàn)證平臺(tái)進(jìn)行通信來(lái)實(shí)現(xiàn)對(duì)FPGA中的數(shù)字邏輯進(jìn)行驗(yàn)證的目的。圖1是典型的RFID芯片的FPGA原型驗(yàn)證環(huán)境原理圖。

2019-05-29 08:03:31

基于龍芯2E的AMC處理器模塊設(shè)計(jì)摘要:介紹基于國(guó)產(chǎn)通用處理器的嵌入式高級(jí)夾層卡(AMC)處理器模塊的設(shè)計(jì)和實(shí)現(xiàn)。該模塊以龍芯2E CPU 為核心,板卡設(shè)計(jì)符合AMC

2010-06-04 16:46:56 29

29 摘要:在使用傳統(tǒng)的動(dòng)態(tài)仿真方法對(duì)通用微處理器這樣大規(guī)模的設(shè)計(jì)進(jìn)行功能驗(yàn)證時(shí)仿真速度成為了瓶頸,而使用FPGA物理原型驗(yàn)證又不能提供很好的可調(diào)試性。本文主要介紹了基于

2010-06-07 11:20:54 0

0 FPGA中的處理器IP概述

可編程邏輯業(yè)對(duì)微處理器核的報(bào)道層出不窮,包括與ARM和MIPS的協(xié)議,這些討論已經(jīng)持續(xù)了數(shù)年。然而,討論的主題大體上沒(méi)什么改變,諸如采用硬

2010-03-10 10:38:14 917

917

引言

自主研發(fā)高性能處理器芯片對(duì)于經(jīng)濟(jì)和國(guó)家安全方面具有重要意義。龍芯系列處理器的成功研制填補(bǔ)了我國(guó)自主研發(fā)高性能通用處理器的空白,龍芯2號(hào)采

2010-11-03 10:17:52 1672

1672

技術(shù)方法,驗(yàn)證了SoC系統(tǒng)、DSP指令、硬件IP等。實(shí)驗(yàn)證明,此FPGA驗(yàn)證平臺(tái)能夠驗(yàn)證SoC設(shè)計(jì),提高了設(shè)計(jì)效率。

2017-11-17 03:06:01 13138

13138

為了能夠靈活地驗(yàn)證和實(shí)現(xiàn)自主設(shè)計(jì)的基于NoC的多核處理器,縮短N(yùn)oC多核處理器的設(shè)計(jì)周期,提出了設(shè)計(jì)集成4片Virtex-6—550T FPGA的NoC多核處理器原型芯片設(shè)計(jì)/驗(yàn)證平臺(tái)。分析和評(píng)估

2017-11-22 09:15:01 4137

4137 龍芯 3A6000 處理器采用龍芯自主指令系統(tǒng)龍架構(gòu)(LoongArch)。龍架構(gòu)從頂層架構(gòu),到指令功能和 ABI 標(biāo)準(zhǔn)等,全部自主設(shè)計(jì),無(wú)需國(guó)外授權(quán)。

2023-08-02 11:09:41 2661

2661

龍芯3A6000處理器是龍芯第四代微架構(gòu)的首款產(chǎn)品,集成4個(gè)最新研發(fā)的高性能6發(fā)射64位LA664處理器核。

2023-08-04 11:37:17 270

270

Banana Pi推出基于龍芯2K1000LA處理器的信創(chuàng)工業(yè)控制開(kāi)發(fā)平臺(tái):BPI-5202信創(chuàng)工業(yè)控制開(kāi)發(fā)平臺(tái)

2023-09-04 09:40:01 908

908

11月28日,2023龍芯產(chǎn)品發(fā)布暨用戶大會(huì)在國(guó)家會(huì)議中心盛大召開(kāi)。本次活動(dòng)以“砥礪前行,中流擊水”為主題,揭曉了中國(guó)自主品牌龍芯的最新產(chǎn)品——龍芯3A6000通用處理器和龍芯2P0500打印機(jī)主控芯片。此外,還公開(kāi)宣布了龍芯處理器核心知識(shí)產(chǎn)權(quán)(IP)以及龍芯自主指令系統(tǒng)架構(gòu)的授權(quán)方案。

2023-12-27 15:04:37 332

332

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論