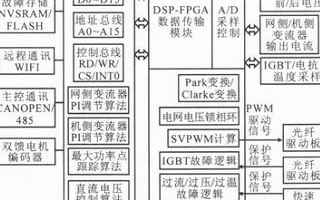

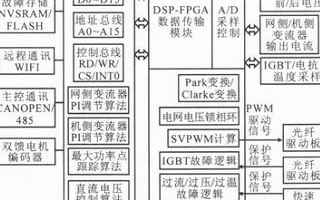

DSP+FPGA+AD控制系統,FPGA負責AD7606的采集,將電機參數采集后,傳輸至DSP ,DSP將數據進行變換后輸出PWM進而控制電機的轉速。DSP采用TI公司的TMS320F28335

2016-07-18 16:59:22

本帖最后由 yicunyu 于 2016-7-18 16:45 編輯

DSP28335+FPGA的數據采集系統,DSP采用TI公司的TMS320F28335,FPGA使用 ALTERA

2016-07-16 14:32:23

DSP Builder V7.2安裝程序下載,安裝之前請確保已安裝Quartus II Version 7.2 。點擊下載

2019-05-05 11:39:16

DSP Builder V9.0安裝程序,使用前請先安裝 Quartus II V9.0軟件。點擊下載

2019-04-22 16:37:48

DSP Builder V9.1安裝程序,請配合Quartus II V9.1軟件使用。點擊下載

2019-05-05 11:38:31

`我參照潘松主編的《現代DSP技術》設計FIR數字濾波器做畢業設計,請求各位大神幫忙看下我這個是什么問題,使用的DSP Builder 13.0版本,破解和軟件匹配都是沒有問題的,運行時

2021-03-07 00:42:07

1 引言在信息技術高速發展的今天,電子系統數字化已經成為有目共睹的趨勢,從傳統應用中小規模芯片構造電路系統到廣泛地應用單片機,到今天DSP及FPGA在系統設計中的應用,電子設計技術已邁入了一個全新

2021-10-29 08:55:40

介紹DSP的基礎知識,DSP builder的直奔概念,介紹如何用DSPBuild來進行設計,并配合相應的實例

2016-04-08 00:54:42

FPGA CPLD同步設計若干問題淺析摘要:針對FPGA/CPLD同步設計過程中一些容易被忽視的問題進行了研究,分析了問題產生的原因、對可靠性的影響,并給出了解決方案。關鍵詞:FPGA/CPLD

2009-04-21 16:42:01

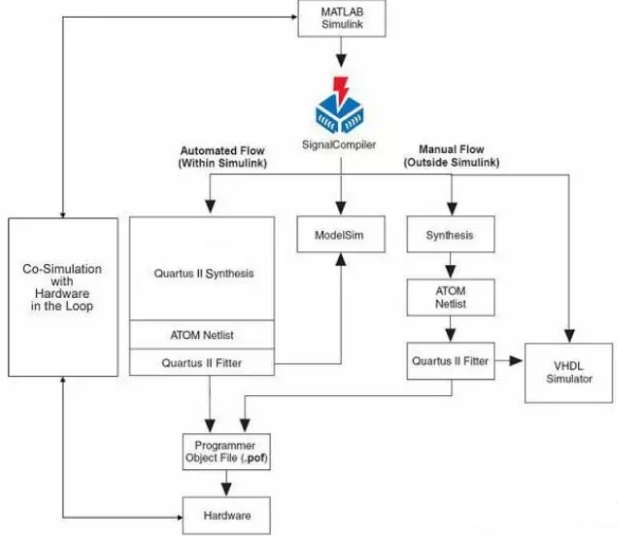

和Quartus II開發軟件的DSP開發工具。在DSP Builder的無縫設計流程中,設計人員首先在MATLAB軟件中進行算法設計,然后在Simulink軟件中進行系統集成,最后將設計輸出為硬件描述

2010-03-10 17:50:30

以及最新的DSP系統工具的概況;接著主要介紹了計算機算法的概念、理論、有限字長效用、FIR和IIR濾波器的實現、多速率和自適應信號處理的FPGA實現;最后,介紹了System Genrerator

2009-07-21 09:22:42

,但也需要設計編程技巧。FPGA制造商不斷改進這一流程,開發專門的軟件,與第三方軟件供應商建立伙伴關系,從而簡化編程過程,并提供最大的靈活性。 FPGA核心與系統級模型工具的集成為設計人員提供了創建

2011-02-17 11:21:37

ARM、DSP及FPGA的技術特點和區別

2019-10-12 07:13:50

系統升級或除錯。DSP VS FPGADSP是通用的信號處理器,用軟件實現數據處理;FPGA用硬件實現數據處理。DSP成本低,算法靈活,功能性強,而FPGA的實時性好,成本較高,FPGA適合于控制功能算法

2021-09-08 17:49:20

本帖最后由 qzq378271387 于 2012-8-15 16:56 編輯

Altera的DSP_Builder現支持FPGA協處理器

2012-08-15 16:37:33

以及最新的DSP系統工具的概況;接著主要介紹了計算機算法的概念、理論、有限字長效用、FIR和IIR濾波器的實現、多速率和自適應信號處理的FPGA實現;最后,介紹了System Genrerator

2009-07-21 09:20:11

以及最新的DSP系統工具的概況;接著主要介紹了計算機算法的概念、理論、有限字長效用、FIR和IIR濾波器的實現、多速率和自適應信號處理的FPGA實現;最后,介紹了System Genrerator

2009-07-24 13:07:08

dsp builder 是在我最近安裝的Quartus ii 12.0網絡免費版時同時安裝的,安裝時候也制定了MATLAB安裝路徑,matlab是2010b版本,自己破解的,在simulink 庫就是沒有DSP builder ......請高手指教,多謝

2012-08-23 09:32:48

quartus2全功能破解版,含nios 、DSP Builder、modulsim ase

2009-08-12 09:00:47

申請理由:學習DSP 和FPGA DSP優越的計算能力 超高的編解碼速度 和FPGA 聯合使用 取長補短 快速實現視頻傳輸不是夢 。第一次申請。現在進行FPGA 的視頻傳輸部分項目描述:項目描述:先

2015-09-10 11:18:56

本帖最后由 cytechsunsong 于 2017-12-17 02:27 編輯

DSP Builder 和DSP Builder Advance 的64位破解器,通吃過去、現在、未來的版本

2017-12-10 17:26:52

Configuration Parameters點擊后matlab就會自動關閉不知道是怎么回事,是因為安裝的DSP builder有問題嗎

2013-04-12 09:54:11

dsp builder按網上教程破解安裝。quartus 9.0+dsp builder9.0+MATLABr2012b在quartus看應該是正確的但是MATLAB的simulink工具箱里dsp builder block為空 點擊時發生錯誤如圖。求大神指導

2013-11-14 10:10:46

哪位壇友有DSP BUILDER 9.1 的破解器,求發給我一份!萬分感謝!QQ1145387296

2015-01-03 12:05:59

成長,CIC低通濾波器得到了廣泛的應用。長期以來,CIC梳狀濾波器一般是在通用DSP處理器上實現的,由于DSP處理器的順序執行特性的限制,其速度很難滿足一些高速抽取與插值系統的需要。FPGA具有優良的全硬件并行執行的特性,研究CIC梳狀濾波器的設計及其FPGA實現具有重要的現實意義。

2019-09-23 07:22:30

FIR濾波器的原理是什么?基于DSP Builder的FIR濾波器該如何去設計?

2021-06-02 06:26:02

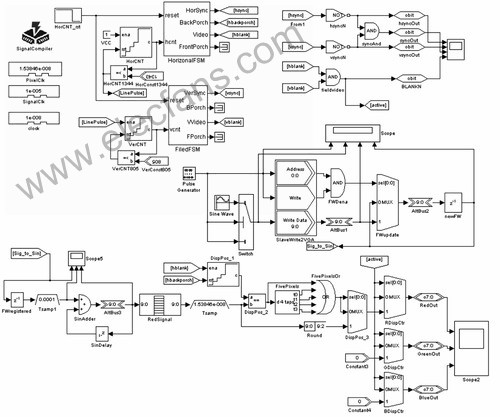

,而對濾波器的輸出信號有移15位即得到實際輸出。以DSP Builder為平臺,對式(7)、式(8)和式(13)算法進行系統級建模、仿真,再利用Signal Compiler生成HDL文件,然后利用

2021-05-13 07:00:00

,而對濾波器的輸出信號有移15位即得到實際輸出。以DSP Builder為平臺,對式(7)、式(8)和式(13)算法進行系統級建模、仿真,再利用Signal Compiler生成HDL文件,然后利用

2021-06-04 07:00:00

基于DSP和FPGA的專業級音頻處理開發板

2012-08-17 14:03:39

基于DSP和FPGA的機器人聲控系統設計

2012-08-17 23:54:05

基于DSP和FPGA的高速串行通信系統設計

2015-03-16 15:47:04

基于FPGA 的DSP 數據采集分析系統設計

2012-08-20 15:35:41

本系統采用基于FPGA與DSP協同工作進行視頻處理的方案,實現視頻采集、處理到傳輸的整個過程。 實時視頻圖像處理中,低層的預處理算法處理的數據量大,對處理速度要求高,但算法相對比較簡單,適合于

2019-06-19 06:12:05

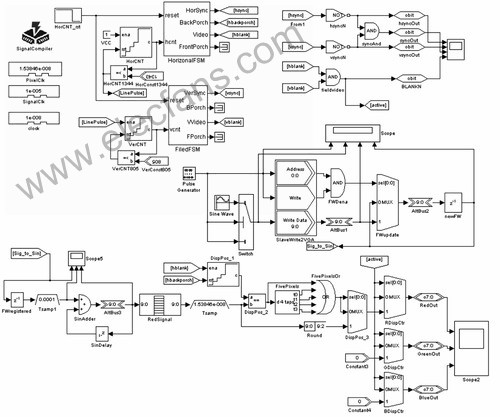

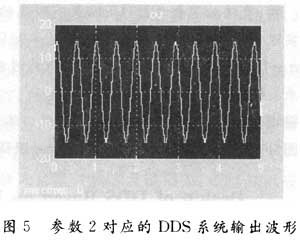

本文采用了Altera公司推出的FPGA的DSP開發工具DSP Builder軟件,基于DDS(直接數字頻率合成)技術原理,設計了一種適合于軟件無線電使用的可控數字調制器,可以完成FSK、PSK、ASK等調制方式,并采用此方法在FPGA芯片上進行系統實現。

2021-04-25 07:25:17

請問如何用DSP和FPGA構建多普勒測量系統?

2021-04-14 06:41:02

最近在安裝DSP Builder11.0+Matlab2011a+Quratus II 11.0安裝完成后沒有找到Altera DSP Builder Blockset;求大神指教。

2015-06-04 16:01:12

求dsp builder破解

2011-06-11 10:33:16

下圖是我畫的simulink圖但是在運行仿真的過程中報錯了,報錯窗口如下[attach]***[/attach]請各位大神指點一下這是什么錯誤,該如何修改啊?我的DSP builder破解成功了,而且和quartus、matlab版本匹配,求大神指點迷津

2018-01-04 11:04:22

的修改方面缺乏靈活性。本文介紹一種嶄新的基于Matlab與QuartusII的DSP處理器的設計軟件DSP Builder,詳細介紹了其設計流程與優點,并以DDS直接數字合成器的實現為例說明用該軟件來設計DSP處理器的方法以及與Matlab、QuartusÊ之間的關系。

2011-03-03 10:05:43

本帖最后由 mr.pengyongche 于 2013-4-30 02:22 編輯

請問誰有與quartersII9.0搭配使用的dsp_builder9.0啊?我下的破解器破解后桌面也不出

2011-08-03 11:16:29

; 2008年6月11號,為幫助系統級設計人員在FPGA軟核

2008-06-17 11:40:12

DSP Builder用戶手冊

2006-03-25 13:24:33 32

32 Twin Builder是ANSYS公司系統仿真單元的核心產品,是一款專業的跨學科多領域系統仿真軟件和數字孿生平臺。能夠做到統領建模、仿真和驗證,并與IIoT物聯網平臺

2021-12-02 10:29:55

本文介紹了電視導引頭跟蹤控制系統的工作原理和組成。通過利用基于FPGA 的現代DSP設計方法,對信號處理電路進行系統模型設計,功能、時序仿真。最后通過對目標信號的現場

2009-08-05 15:05:49 24

24 本文介紹了DSP 和FPGA 在數字電子設計中的優勢,并結合雷達模擬系統的硬件設計實例,重點闡述了相應的硬件與軟件實現方法。關鍵詞:DSP FPGA 數字電路設計雷達模擬系統

2009-08-25 14:33:01 15

15 文中首先分析了MATLAB/Simulink 中DSP Builder 模塊庫在FPGA 設計中優點,然后結合FSK 信號的產生原理,給出了如何利用DSP Builder 模塊庫建立FSK 信號發生器模型,以及對FSK 信號發生器模

2009-08-27 12:07:35 87

87 EP4CE10F17C8N,Cyclone IV FPGA設備,INTEL/ALTERAEP4CE10F17C8N,Cyclone IV FPGA設備,INTEL

2023-02-20 17:00:57

EP4CE10F17I7N,Cyclone IV FPGA設備,INTEL/ALTERAEP4CE10F17I7N,Cyclone IV FPGA設備,INTEL

2023-02-20 17:03:19

EP4CE6F17C8N ,Cyclone IV FPGA設備,INTEL/ALTERAEP4CE6F17C8N ,Cyclone IV FPGA設備,INTEL

2023-02-20 17:05:47

一種基于DSP Builder 的軟件無線電調制器的設計與實現::針對基于FPGA 的DSP 技術,本文提出了一種基于DSP Builder 的軟件無線電調制器的設計方法,在DDS 的理論基礎上,采用DSP Builder 軟

2009-12-14 11:08:03 34

34 DSP Builder Reference Manual:The blocks in the AltLab library are used to manage design hierarchy

2010-02-16 12:14:25 14

14 介紹了一種基于DSP和FPGA的GPS-B碼時統終端系統的設計方案,提出了一種利用FPGA對IRIG-B碼進行解碼的設計方法。詳細論述了具體的設計方案及軟硬件的實現。通過將快速的DSP與FPGA相結

2010-02-24 13:48:49 22

22 FPGA實現DSP應用

摘要:具有系統級性能的FPGA在半導體工藝的線寬達到深亞微米后更進一步按信號處理的要求改進器件結構和性能,不僅可實現VLSI DSP,且具有系統

2010-04-01 15:39:54 14

14 DSP無線電調制器的設計與實現

摘要:針對基于FPGA 的DSP 技術,本文提出了一種基于DSP Builder 的軟件無線電調制器的設計方法,在DDS 的理論基礎上,采用DSP Builder

2010-04-01 15:48:46 16

16 提出了一種基于中國地面數字電視廣播傳輸標準的星座映射與解映射器的設計方法。使用DSP Builder的各種模塊搭建系統,并利用Signal Compiler生成HDL工程。在完成對所生成工程的優化后

2010-07-05 16:08:23 18

18 系統(HPS)來評估SoC的特性及性能。Intel Agilex? F系列FPGA開發套件提供了一個完整的設計環境,其中包括采用PCI Express(PCIe)

2024-02-27 11:51:58

DSP和FPGA組成的伺服控制系統能夠滿足復雜的控制算法要求。通過對TI公司的DSP控制芯片TMS320F2812和ALTERA公司的FPGA芯片EP1C3T144的功能和特點分析,給出了一種基于DSP和FPGA的光電經緯儀

2010-11-11 15:57:56 35

35 針對使用硬件描述語言進行設計存在的問題,提出一種基于FPGA并采用DSP Builder作為設計工具的數字信號處理器設計方法。并按照Matlab/Simulink/DSP Builder/QuartusⅡ設計流程,設計了一個12

2010-11-22 16:21:08 53

53 基于DSP Builder的Chirp信號源設計

DSP Builder是Ahera公司提供的一個系統級(或算法級)設計工具。它架構在多個軟件工具之上,并把系統級(算法仿真建模)和RTL級(硬件實現)兩

2009-10-04 09:47:11 1104

1104 基于DSP Builder的16階FIR濾波器實現

0 引 言

FIR數字濾波器在數字信號處理的各種應用中發揮著十分重要的作用,它能夠提供理想的線性相位響應,在

2009-11-26 09:18:51 866

866 基于DSP Builder的DDS設計及其FPGA實現

直接數字合成器,是采用數字技術的一種新型頻率合成技術,他通過控制頻率、相位增量的步長,產生各種不同頻率的信號。他具

2010-01-14 09:43:55 1292

1292

淺析DSP智能攝像機發展的必然方向 (1)

隨著現代科學技術的發展,視頻監控系統也向智能化發展,而監控用的攝像機也必須智能化。DSP攝像機有普通

2010-03-25 14:23:30 979

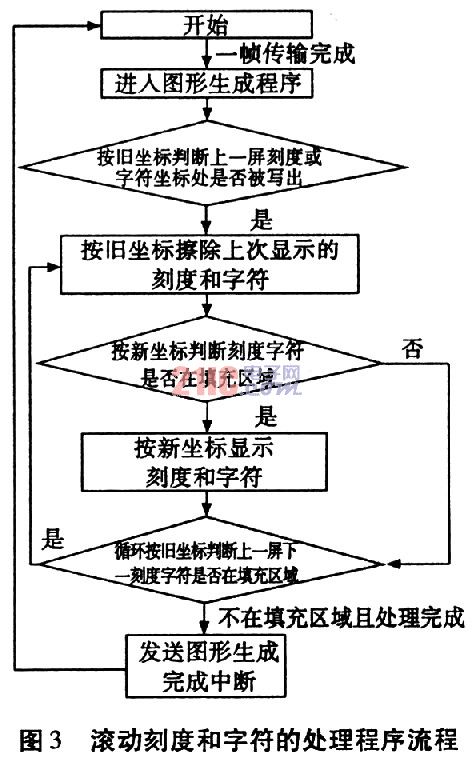

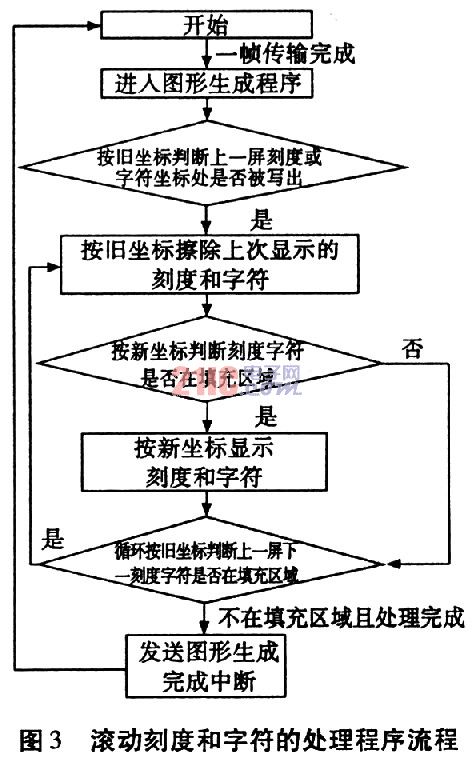

979 本文設計了基于DSP與FPGA的系統結構,采用了軟硬件填充的圖形處理方法,先由DSP軟件完成圖形輪廓生成,然后FPGA硬件圖形處理器根據圖形輪廓完成耗時的圖形填充,使系統在實時性

2010-07-01 11:02:38 988

988

本文基于DSP Builder的VGA接口設計方法,對VGA接口時序和系統設計需求進行了介紹,并在硬件平臺下實現一維與二維信號的顯示。 VGA接口標準 VGA顯

2010-08-03 10:23:40 1209

1209

摘 要:不斷發展的DSP技術迅速地拓寬擴展到了各應用領域,但傳統的DSP處理器由于以順序方式工作而數據處理速度較低,且在功能重構及應用目標的修改方面缺乏靈活性。本文介紹一種嶄新的基于Matlab與QuartusII的DSP處理器的設計軟件DSP Builder,詳細介紹了其設計

2011-02-24 17:19:34 44

44 應用MATLAB/DSP Builder可以對多種類型的電子線路模塊或系統進行建模、分析和硬件實現,且更擅長于一些較復雜的功能系統,及偏向于高速算法方面的模塊的設計和實現,還能利用HDL LMPORT模塊將HDL文本設計轉變成為DSP Builder元件。 本章將給出一些DSP及數字

2011-02-28 10:18:07 54

54 DSP Builder下載入口

2011-06-14 18:00:20 116

116 DSP Builder7.2 SP3補丁下載。

2011-06-14 18:02:32 49

49 本文采用DSP Builder 開發工具,實現利用混沌信號對通信數字信號的加密與解密。首先在Simulink里面利用DSP Builder開發工具建立系統通信模型,采用FM對混沌信號進行差分鍵控形成FM-DCSK信號

2011-09-01 14:35:49 28

28 為滿足導航系統設計的小型化、實時性要求,本文提出了一種基于FPGA + DSP 的實現方案。該方案的設計思路是:將FPGA 映射到DSP EMIF 的一段地址空間,并用FPGA 來完成多通道信號的采集; DSP 根

2011-09-13 14:32:08 77

77 提出了一種基于DSP和FPGA 的通用型運動控制系統!大大降低了系統成本

2013-09-23 17:49:37 59

59 基于fpga的dsp開發教程,供初學者使用與參考

2015-11-24 14:31:14 1

1 dsp builder 11.1的破解文件,親測12和13版也能用

2015-12-24 10:52:43 35

35 采用DSP和FPGA直驅閥用音圈電機驅動控制系統。

2016-05-04 14:37:01 16

16 基于DSP和FPGA技術的細胞圖像采集系統設計

2016-08-26 12:57:52 15

15 基于DSP和FPGA的多頻聲納采集系統設計_劉寅

2017-03-19 11:45:23 0

0 基于FPGA和DSP網絡單向時延測量系統設計與實現_唐旭

2017-03-19 11:38:26 0

0 基于雙DSP和雙FPGA的高速圖像處理系統設計_吳雷

2017-03-16 09:28:51 2

2 基于DSP_FPGA的LFMCW雷達測距信號處理系統設計_陳林軍

2017-03-19 19:07:17 4

4 基于FPGA和DSP的高速圖像處理系統

2017-10-19 13:43:31 19

19 基于FPGA_DSP的智能車全景視覺系統

2017-10-19 13:52:03 7

7 ,說明這種方法在簡化設計難度、提高設計速度和靈活性等方面的優點和應用價值。并提出了其仿真和FPGA實現的基本方法。 關鍵詞: DSP Builder;m序列;Gold序列;平衡Gold碼 在擴展頻譜通信系統中,偽隨機序列起著十分關鍵的作用。在直接序列擴頻系統的發射端,偽隨機序列擴

2017-10-30 10:37:11 0

0 。 Altera DSP Builder是一款系統級的設計工具,依賴于Mathworks公司的數學分析工具Matlab/Simulink,可以在Sireulink中進行圖形化設計和仿真,同時又可以通過signalCompiler把Matlab/Simulink的模型文件(.mdl)轉換成相應的硬件描述語言VHDL,本文用兩種

2017-10-30 15:39:03 5

5 對幀同步的檢出進行研究,設計了一種基于DSP Builder的幀同步檢出模型,具體以常用的幀同步碼組巴克碼為例,詳細介紹了該模型的設計實現方法,通過軟硬件測試驗證,該檢出模型切實可行。

2017-11-13 16:16:55 3

3 針對噴油器霧化粒徑測量系統實時數據處理的特點,將FPGA技術與DSP技術相結合,研究一種基于FPGA和DSP的電控噴油器粒徑檢測系統;為滿足動態測量的要求,設計了應用高性能的多路開關和超低輸入偏置電流運放的多通道微電流高速采集板;詳細介紹了檢測系統中基于FPGA和DSP的軟硬件設計和工作原理。

2017-12-06 17:03:04 1728

1728

FPGA+DSP的數字硬件系統正好結合了兩者的優點,兼顧了速度和靈活性。本文以導引頭信號處理系統為例說明FPGA+DSP系統中FPGA的關鍵技術。

2019-01-08 08:36:00 2449

2449

This video shows you how to install the Python* Client and Intel? Knowledge Builder Mobile Data

2018-09-27 05:34:00 2182

2182 時間 美高森美公司(Microsemi) 宣布SmartFusion 2 SoC FPGA用戶現在可以獲益于其新近發布的系統創建器(System Builder)設計工具。System Builder

2018-09-25 09:07:01 513

513 本文檔的主要內容詳細介紹的是FPGA視頻教程之SOPC builder的詳細基礎知識說明。主要目的是:1.在嵌入式系統中使用PLD,2.SOPC Builder 工具,3.SOPC Builder

2019-03-21 16:54:29 8

8 變流器系統。控制系統平臺采用主頻300 MHz的DSP芯片與FPGA共同控制,大大提高了系統的穩定性以及實時性。控制系統采用矢量控制技術和功率閉環的變速控制策略。最后在自主研發的2 MW雙饋式風電變流器的樣機上進行了實驗和現場試運行,驗證了控制系統的可靠性。

2019-05-20 16:32:37 1744

1744

基于Dsp Builder的DDS實現及其應用總結說明。

2021-04-27 09:40:10 0

0 基于FPGA和DSP的機載圖形顯示系統

2021-06-08 10:48:08 36

36 電子發燒友網站提供《基于DSP和FPGA的水聲定位系統主控機設計.pdf》資料免費下載

2023-10-19 10:26:33 0

0

電子發燒友App

電子發燒友App

評論