大家好,歡迎Vivado的一個快速演示,它是xilinx新的設計套件,應用到7系列和以上的系列器件。

2012-04-25 08:55:55 2192

2192 Xilinx的新一代設計套件Vivado相比上一代產品ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。

2022-09-14 09:09:56 1526

1526 雙擊桌面圖標打開Vivado 2017.2,或者選擇開始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 403

403

21-36]從C:/Xilinx/Vivado/2013.1/data/parts/arch.xmlParsing RTL基元文件[C:/Xilinx/Vivado/2013.1/data/parts

2018-11-27 14:30:08

嗨,我們剛剛將實施工具從Vivado 2013.1更新到2013.2。使用2013.2軟件,我們無法運行實施流程。該工具在綜合時崩潰,在安全IP的許可證檢查中出現致命錯誤。請參閱隨附的屏幕截圖。通常

2018-11-30 11:12:34

[0x3b0060ebe0] /pkg/xilinx-vivado-/2013.4/Vivado/2013.4/lib/lnx64.o/librdi_timing.so(HASTNetworkImpl

2018-10-18 14:40:02

嗨,我下載Vivado2014.3并嘗試申請30天的評估許可證!當我通過vivado許可管理器工具連接到xilinx許可證網站時,我將網站顯示為附件。1)基于證書的許可證只有3個:ISE

2018-12-06 11:31:19

此消息:bp @ bp:/opt/Xilinx/Vivado/2016.1$ source settings64.shbp@bp:/opt/Xilinx/Vivado/2016.1$ bin

2018-12-21 10:58:20

操作系統:Debian 8工具:Vivado 2016.2(系統設計)我已經下載了xilinx.lic并將許可證復制到我的vivado工具,“查看許可證狀態”沒有問題,完成塊設計后,運行Synthesis,然后合成失敗!!附加是信息,是否有人可以修復它!?

2020-05-25 13:25:05

我們非常高興地宣布Vivado 2017.3的發布 - 包含許多功能。您可以從Xilinx的下載頁面下載Vivado 2017.3版本,并參考以下用戶指南,了解有關Vivado 2017.3版本

2018-12-28 10:52:15

個圖標,我可以成功打開它以啟動一個新項目。當我下載vivado 2017.4更新1并雙解壓縮并運行安裝程序時,它會返回一條消息:“沒有有效的Xilinx安裝,可以應用此更新。”。我已卸載軟件并多次重新

2019-01-04 11:14:26

我對Vivado工具如何決定如何映射(例如,從GPIO外部制作的“led”端口到實際引腳而不指定XDC文件中的名稱感到困惑。在我看來,只要指定一個引腳,vivado就會以某種方式將一個陣列中的所有

2018-10-30 18:02:44

的。來獲取關于原始的 ISE 設計套件以及 Xilinx 在 Vivado 中對這些開發工具做改進的理由的討論。值得重申的是,Vivado 支持 7 系列和 Zynq-7000 以及之后的設備,但是

2021-01-08 17:07:20

Vivado中xilinx_courdic IP核(求exp指數函數)使用

2021-03-03 07:35:03

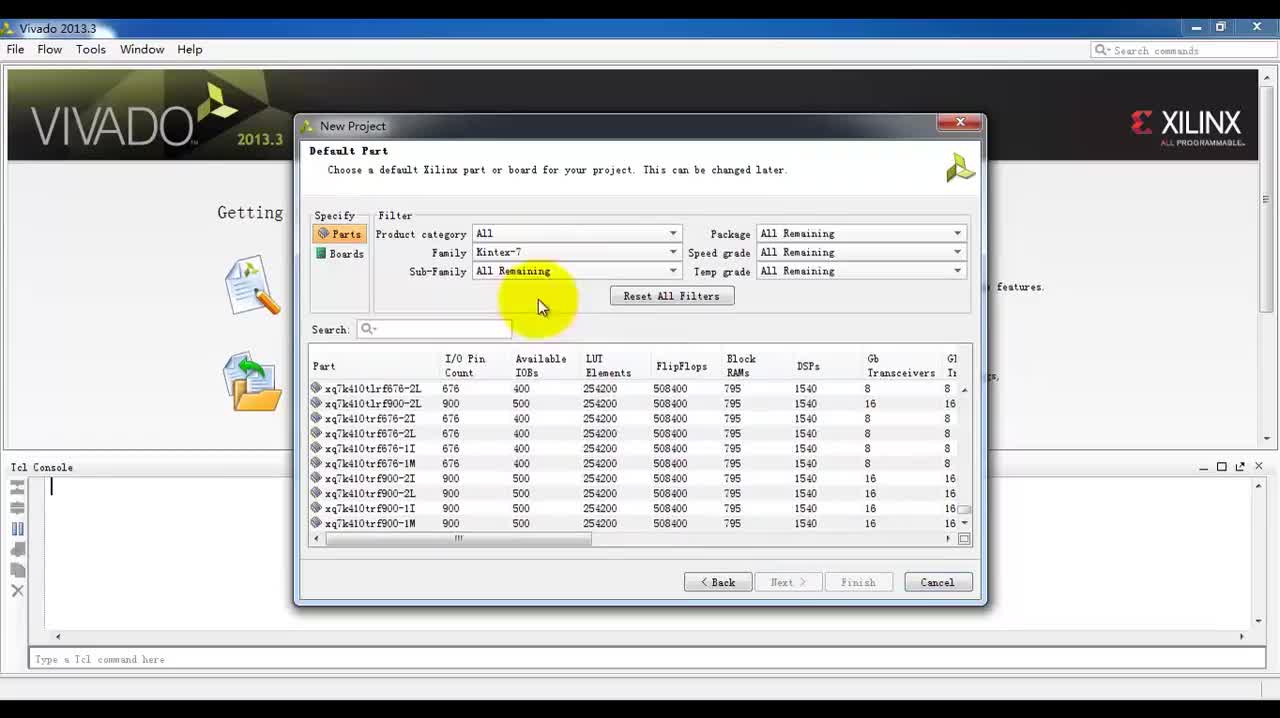

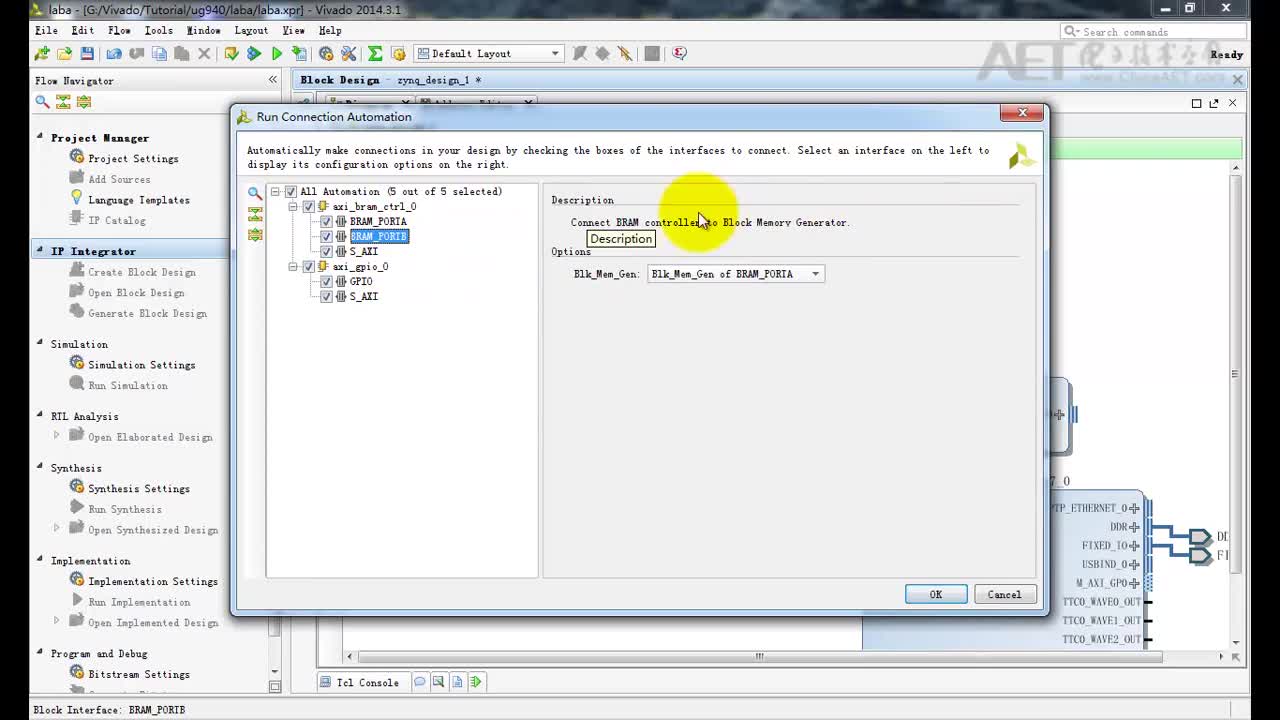

的的Vivado 工具把各類可編程技術結合在一起,能夠擴展多達1 億個等效ASIC 門的設計。Vivado設計界面如下圖:圖1. Vivado設計界面1.2芯片支持Vivado支持Xilinx的IC如下

2019-07-18 15:40:33

的的Vivado 工具把各類可編程技術結合在一起,能夠擴展多達1 億個等效ASIC 門的設計。Vivado設計界面如下圖:圖1. Vivado設計界面1.2芯片支持Vivado支持Xilinx的IC如下

2023-09-06 17:55:44

Vivado工具(2016.2)可以獨立路由Xilinx IP核DDR3 SDRAM控制器(rdf0223-ac701-mig-c-2015-1.zip)。將mydesign添加到路由可以在合成階段

2020-05-06 10:32:02

Xilinx設計工具ISE設計套件系統版+ Vivado系統版14.3是否可以為此版本的軟件進行靜默安裝?任何意見,將不勝感激干杯以上來自于谷歌翻譯以下為原文Xilinx Design Tools

2018-12-28 10:53:04

你好,我們在2016年3月購買了Xilinx-Vivado / Ise的完整版本。我的同事將我添加為“管理員”,因此我也可以創建許可證。但它沒有顯示在我的xilinx帳戶中,因此我無法生成許可證。我

2018-12-21 11:00:57

嗨,我的同事為我添加了“admin”作為許可證(Vivado / ISE-System) -2016年3月購買的產品。當我登錄Xilinx許可時,它沒有顯示出來。我收到了Xilinx發送的關于將我

2018-12-21 10:58:55

親愛的Xilinx, 我有一臺Windows 8.1聯想G500筆記本電腦,我試圖安裝最新的Xilinx Vivado Webpack + SDk。安裝成功完成,但是當我嘗試安裝許可證時,許可證

2019-11-08 08:56:31

我現在運行了幾個項目我觀察到安裝了程序Xilinx ISE和Vivado的目錄高達50 GB,因為我想在運行項目期間生成的文件。我不記得一開始是不是那么多。請告訴我哪些可以刪除的“運行時”文件以及

2018-12-20 11:20:46

Xilinx工具:vivado在該圖中,TX_CLK_i連接到pll_x1模塊的輸入時鐘。然后,pll_x1的輸出時鐘連接到ODDR。接下來,ODDR的輸出引腳將連接到I / O引腳

2020-05-04 08:04:41

您好。我無法運行Xilinx許可證管理器以使用Ise 14.7加載我的許可證(_xlmc.exe已停止..)。安裝Vivado Design Suite 2014.1后出現此錯誤。我該如何解決?,我可以使用vivado許可證管理器使用Ise工具加載我的許可證嗎?

2020-03-12 06:39:47

哪位大神能夠分享一下關于xilinx vivado 2013.4 的教程啊,小弟感激不敬!!!

2014-03-26 21:38:02

xilinx EDF已經綜合過的網表文件怎樣添加到Vivado工程中?買了一個第三方的IP,給出了端口列表和核心模塊發射機的.edf已經綜合過的網表文件,該網表文件里面富含了大量的信息,我想知道edf文件怎樣添加到Vivado工程中去?要不然的話,總是提示核心模塊實例化失敗!

2016-09-07 11:34:10

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

申請理由:項目描述:本人之前一直從事Altera FPGA的學習套件的教程資料研發,如今轉向Xilinx,考慮Xilinx現在主推的工具是vivado,而S6系列芯片無法使用,為了使自己的教程資料

2016-10-11 18:15:20

關于Xilinx Vivado工具,相信對于接觸FPGA開發的工程師應該并不陌生。今天來講講Vivado的安裝詳細步驟。 Vivado設計套件,是FPGA廠商Xilinx(賽靈思)公司2012年發布

2020-05-31 10:20:03

您好,我想下載Xilinx Vivado 2017.1但是,每次我收到以下錯誤:“由于您的帳戶導出合規性驗證失敗,我們無法滿足您的要求。”誰能幫我?提前致謝以上來自于谷歌翻譯以下為原文Hello

2018-12-27 10:41:52

嗨,我正在尋找有關如何使用Xilinx Vivado創建Hard宏的示例。了解如何在設計中修復路由并在閱讀pdf(下面)時,提到可以根據要求提供示例,這將非常有幫助。我是否可以收到一些此實施的示例

2018-11-12 14:42:01

請問一下Xilinx公司發布的vivado具體的作用是什么,剛剛接觸到,以前一直用quartus ii,沒有使用過ise,后來今天聽說了vivado,不知道是做什么用的,希望大家都能參與討論中,謝謝。

2015-04-15 16:51:00

Vivado工具使用流程和Basys3板卡使用Xilinx FPGA基礎知識簡介以計數器(或流水燈)實驗為例,完成Vivado設計流程Basys3板卡簡介Vivado設計在Basys3上的實現2

2019-02-19 10:56:07

,但現在有了Vivado,我沒有看到這樣的應用程序我希望Xilinx不要像許多其他應用程序那樣放棄這個應用程序以上來自于谷歌翻譯以下為原文Hello everyone Can I Install

2018-12-27 10:57:02

.Vivado 2016.4與Spartan-6不兼容。據Xilinx稱,Vivado不支持任何早于7系列的設備系列。)根據以下說明,Xilinx System Generator可以嵌套在ISE Design

2018-12-27 10:55:34

你好,我在CentOS 7中安裝了Vivado v2015.2(64位)。但是,Vivado工具在第二次出現時出現以下錯誤消息。 /opt/Xilinx/Vivado/2015.2/bin

2018-12-13 10:36:45

盡管Debian是Xilinx工具不受支持的平臺,但如果我們使用其衍生工具(Ubuntu等),它就是一個widley分發版。經過一些工作,我已經能夠在Debian上使用Vivado。這是我所做的以防

2018-12-05 11:00:34

/Xilinx/Vivado/2013.2/tps/lnx64/jre/lib/amd64/server/ libjvm.so /opt/Xilinx/Vivado/2013.2/tps/lnx64

2018-12-10 10:29:37

`基于 FPAGxilinx vivado 仿真模式介紹本文介紹一下xilinx的開發軟件 vivado 的仿真模式, vivado的仿真暫分為五種仿真模式。分別為:1. run

2018-01-24 11:06:12

嗨,我正在使用Xilinx Vivado工具對帶有MCS文件的Spansion配置閃存進行編程,并且需要以0x100(256)的偏移對其進行編程。我需要最初的256個字節來編程其他信息,并要求從地址

2020-06-09 10:28:14

你好,我對Xilinx工具的自下而上合成流程有一些疑問。由于我對這個領域很新,所以我只知道ISE和XST。在我的頂級設計中,我實例化了幾個優化的多線程(不是庫中的標準乘法器),但我不希望它們在綜合

2019-03-22 06:51:51

當我試圖在Ubuntu的Synplify中調用xilinx for P& R時,它說XILINX變量尚未設置。我把它分配到vivado中的bin文件夾,但似乎是錯誤的。看起來Synplify

2018-12-19 11:04:40

大家好,在將vivado 2016.1安裝到d:\ xilinx時,發生以下錯誤:提取存檔D時遇到錯誤:\ Xilinx_Vivado_SDK_2016.1_0409_1 \ payload

2018-12-20 11:23:44

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高層次綜合)工具支持將C、C++等語言轉化成硬件描述語言,同時支持基于OpenCL等框架

2021-11-11 09:38:32

xilinx[email protected] with the ‘get license’ links. The installation steps require

Vivado Design Suite\

Vivado 2018-12-19 11:21:19

:Edition選擇安裝:Vivado HL WebPACKWARN:指定的值在InstallOptions的配置文件中(啟用WebTalk for SDK將使用情況統計信息發送到Xilinx)丟失或無效。警告

2018-12-19 11:16:14

嗨,我是Xilinx工具的新手,現在正在學習FPGA設計。如果Xilinx Vivado是使用和學習的最佳工具,有人可以指導我嗎?如果是這樣,哪個版本可以免費使用,如果可能的話鏈接。謝謝,

2020-04-17 07:38:59

that is compatible with the version of Xilinx software that you are using. Please note that Vivado

2019-01-04 11:06:38

我在Digilent論壇上看到有關于學習Vivado軟件菜單基礎知識的Xilinx PDF,我在哪里可以找到PDF?此外,當我安裝Vivado時,我安裝了所有內容,我是初學者,如果我只是安裝一個簡單的Vivado菜單,那將是最好的,但我如何恢復它,這會以任何方式搞砸我的許可證?traymond

2020-04-30 09:32:35

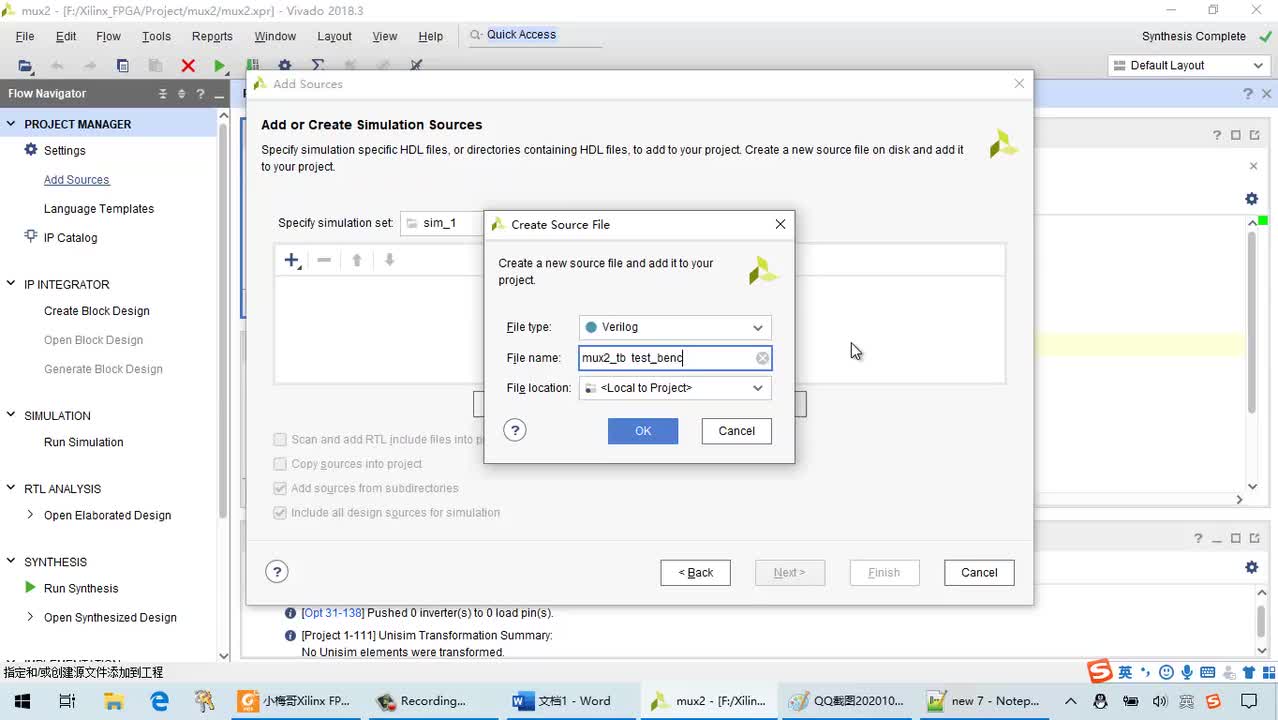

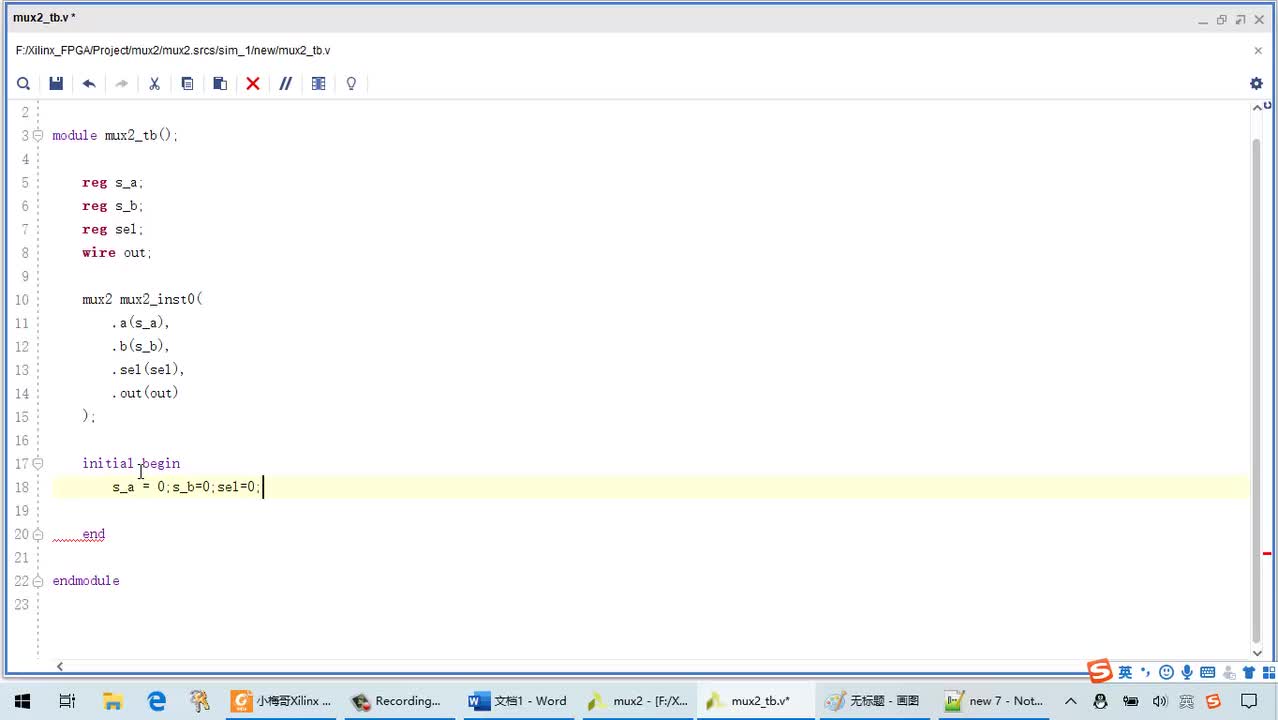

由各自的testbench,分類管理更一目了然。圖2 Vivado中testbench文件管理 2. Vivado自帶的Simulation/Simulator工具與Altera索性放棄自己的內置

2016-01-13 12:04:16

嗨,你能告訴我在閃存存儲器MT29F1G08ABADAWP-IT:D的vivado工具中設置的設置,來自制造商Micron與Xilinx Zynq Soc XC7Z020-2CLG400I一起

2019-03-27 10:14:33

你好,我安裝了Xilinx vivado 2015.2,我將開始為USRP x310編寫計算引擎。為此,我需要一個完整的Xilinx設計許可證。首先,我想澄清一下本網站末尾發布的許可是否合適,因為我

2020-05-06 07:58:17

RIO設備的FPGA編程,安裝了LabVIEW 2015 FPGA Module Xilinx Tools Vivado 2014.4安裝此工具包時選擇了評估版本,目前正常使用,不知道評估期是多久。LV已經激活了專業版,請問怎樣徹底激活這個編譯工具包啊?LV Licence管理器中沒有出現這個模塊。

2015-08-28 22:20:22

Xilinx發布Vivado Design Suite 2013.3版本,新增最新UltraFast設計方法及新一代即插即用IP和部分重配置功能,豐富設計流程,實現前所未有的IP易用性, 進一步提高設計生產力

2013-12-24 17:51:23 1193

1193 Xilinx采用先進的 EDA 技術和方法,提供了全新的工具套件Vivado,面向未來“All-Programmable”器件。Vivado開發套件提供全新構建的SoC 增強型、以IP和系統為中心

2017-02-08 04:10:11 457

457 一年一度的 Club Vivado 用戶群大會即將在全球 9 大城市舉行。Xilinx 誠摯歡迎全球的 Vivado 用戶參與到這一免費活動中。您將有機會與 1,000 多位設計工程師同行

2017-02-08 06:04:03 204

204 美國賽靈思官方授權培訓伙伴依元素科技,以賽靈思最新的客戶培訓課程,通過Webex在線舉辦免費培訓。近期推出的在線免費培訓是 “Vivado設計套件工具流程”。 Xilinx采用先進的 EDA 技術

2017-02-08 11:58:12 423

423 Virtex和Kintex UltraScale架構的FPGA和Vivado開發工具的一些主要的看點: ? 基于UltraScale架構的FPGA實現數據傳輸機制是通過將高性能的并行專用IO接口和高速的串行收發器結合起來實現的,UltraScale架構的串行

2017-02-08 12:33:07 495

495 很久沒有更新vivado+zedboard系列的博客了。前面的十篇博客主要介紹了Xilinx vivado工具的使用流程,vivado+zedboard裸機開發的方法以及部分Xilinx官網的實例

2017-02-08 16:20:11 1058

1058 眾所周知 Hackaday.com 網站上聚集著眾多極客(Geeker),他們打破傳統,標新立異,敢于嘗試新的東西,今天這篇文章搜集了這些極客對Xilinx Vivado HLS工具使用經驗和心得

2017-02-08 20:01:59 550

550

? 無縫集成在其設計中的工作。該 ?IP? 集成工具支持針對所有 ?Xilinx? 器件提供,其中包括最新 ?UltraScale? 器件系列,可充分滿足 ?Vivado? 設計套件工具 ?2014.4? 以及更高版本的要求。 了解更多 ??

2017-02-09 08:12:36 319

319

隨著xilinx公司進入20nm工藝,以堆疊的方式在可編程領域一路高歌猛進,與其配套的EDA工具——新一代高端FPGA設計軟件VIVADO也備受關注和飽受爭議。

2017-02-11 19:08:00 4986

4986 Xilinx Vivado工具支持僅將系統設計的一部分進行綜合,即OOC(out of context)綜合方式。OOC綜合方式的流程就是將設計的某個模塊單獨完成綜合操作,這會帶來如下可能性

2017-03-21 09:50:30 5424

5424 無論此刻你是一個需要安裝Xilinx Vivado工具鏈的入門菜鳥,還是已有license過期的Vivado老鐵,今兒咱就借著這篇文章,把學習「Vivado如何獲取License」這檔子事兒給說通透咯~ 手把手教程,分三部分講述。

2018-07-03 09:54:00 58889

58889

在ISE中稱為ChipScope而Vivado中就稱為in system debug。下面就介紹Vivado中如何使用debug工具。 Debug分為3個階段: 1. 探測信號:在設計中標志想要查看的信號 2. 布局布線:給包含了debug IP的設計布局布線 3. 分析:上板看信號。

2017-11-17 14:05:02 56687

56687

使用Xilinx Vivado HLS(Vivado 高層次綜合)工具實現浮點復數QRD矩陣分解并提升開發效率。使用VivadoHLS可以快速、高效地基于FPGA實現各種矩陣分解算法,降低開發者

2017-11-17 17:47:43 3293

3293

資源、速度和功耗是FPGA設計中的三大關鍵因素。隨著工藝水平的發展和系統性能的提升,低功耗成為一些產品的目標之一。功耗也隨之受到越來越多的系統工程師和FPGA工程師的關注。Xilinx新一代開發工具Vivado針對功耗方面有一套完備的方法和策略,本文將介紹如何利用Vivado進行功耗分析和優化。

2017-11-18 03:11:50 4873

4873 Xilinx公司講述:Getting Started with Vivado High-Level Synthesis

2018-06-04 13:47:00 3416

3416

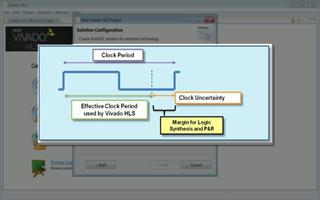

Vivado HLS 是 Xilinx 提供的一個工具,是 Vivado Design Suite 的一部分,能把基于 C 的設計 (C、C++ 或 SystemC)轉換成在 Xilinx 全可編程芯片上實現用的 RTL 設計文件 (VHDL/Verilog 或 SystemC)。

2018-06-05 10:31:00 6326

6326

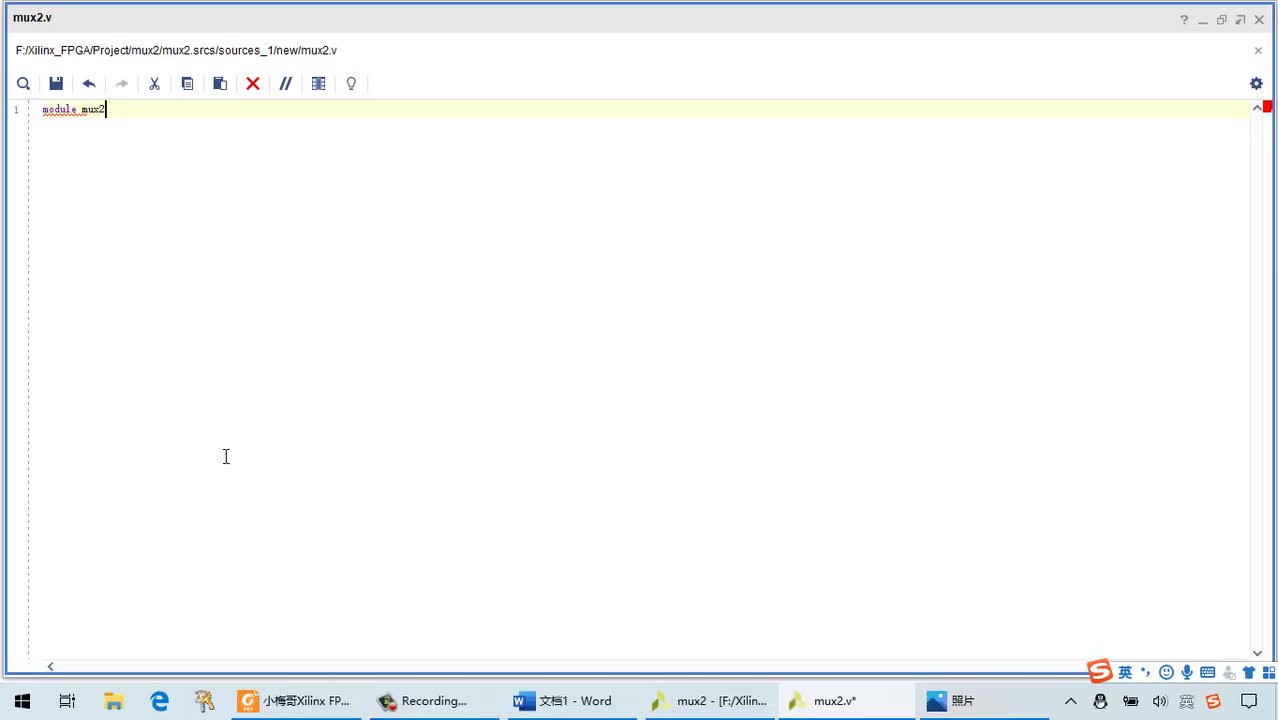

Vivado不僅是xlinx公司的FPGA設計工具,用它還可以學習Verilog描述,你造嗎?

2018-09-20 09:29:22 9427

9427 本文通過一個簡單的例子,介紹Vivado 下的仿真過程。主要參考了miz702的教程,同時也參考了Xilinx的ug937, xapp199.。

2018-11-10 10:53:51 37132

37132 了解如何使用Vivado設計套件的電路板感知功能快速配置和實施針對Xilinx評估板的設計。

2018-11-26 06:03:00 3062

3062 了解如何使用新的激活許可為Vivado工具生成浮動或基于服務器的許可證。

此外,了解如何查看,提供甚至將這些許可證返還給Xilinx

2018-11-22 07:06:00 3563

3563 介紹了如何利用Vivado HLS生成FIR濾波算法的HDL代碼,并將代碼添加到ISE工程中,經過綜合實現布局布線等操作后生成FPGA配置文件,下載到FPGA開發板中,Darren采用的目標板卡是Spartan-3 FPGA。

2019-07-30 17:04:24 4554

4554 xilinx的Vivado工具也一直在更新,到本人記錄此文的時候,Vivado已經有2017.3版本了,建議大家使用最新的Vivado工具。

2021-01-12 17:31:53 10

10 Xilinx_Vivado_zynq7000入門筆記說明。

2021-04-08 11:48:02 70

70 LOCK_PINS 是 Xilinx Vivado 做物理約束的屬性之一。用來將LUT的邏輯輸入(I0,,I1,I2...)綁定到其物理輸入pin上(A6,A5,A4...)。

2023-01-11 10:52:24 768

768 Xilinx LabTools工具是Xilinx FPGA單獨的編程和調試工具,是從ISE或Vivado中獨立出來的實驗室工具,只能用來下載FPGA程序和進行ILA調試,支持所有的FPGA系列,無需

2023-03-28 10:46:56 4755

4755 Xilinx的新一代設計套件Vivado相比上一代產品 ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言 XDC 以及腳本語言 Tcl 的引入則成為

2023-04-15 09:43:09 958

958 今天推出Xilinx已發布的《Vivado使用誤區與進階》系列:用TCL定制Vivado設計實現流程。

2023-05-05 09:44:46 674

674

電子發燒友網站提供《為EBAZ4205創建Xilinx Vivado板文件.zip》資料免費下載

2023-06-16 11:41:02 1

1 Vivado是Xilinx公司2012年推出的新一代集成開發環境,它強調系統級的設計思想及以IP為核心的設計理念,突出IP核在數字系統設計中的作用。

2023-09-17 15:37:31 1060

1060

Xilinx Vivado工具的配置約束隱藏得比較深,如圖1所示,在進入配置頁面前,首先需要點擊PROGRAM AND DEBUG->Generate Bitstream執行工程的全編譯,然后點擊IMPLEMENTATION->OpenImplemented Design進入實現頁面。

2023-12-02 12:19:19 220

220

電子發燒友網站提供《使用P4和Vivado工具簡化數據包處理設計.pdf》資料免費下載

2024-01-26 17:49:11 0

0

電子發燒友App

電子發燒友App

評論