ICARUS-Q:一種基于RFSoC的可擴展超導量子計算機控制系統

Park, Kun Hee ; Szen Yap, Yung ; Tan, Yuanzheng Paul ; Hufnagel, Christoph ; Hoang Nguyen, Long ; Lau, Karn Hwa ; Efthymiou, Stavros ; Carrazza, Stefano ; Budoyo, Rangga P. ; Dumke, Rainer

eprint arXiv:2112.02933,December 2021?

摘要

本文基于Xilinx射頻片上系統器件(RFSoC)給出了超導量子比特的控制和測量裝置。裝置分為四個部分:多個RFSoC FPGA板、多板DAC和ADC通道同步裝置、給量子位提供偏置的低噪聲直流電流源以及用于支撐遠程實驗的云訪問能力。該系統不需要微波混頻器。FPGA板的16個DAC通道在第三Nyquist區直接生成微波脈沖,八個ADC通道則在第五和第九區之間直接采樣。

I.?概述

稀釋制冷機中的超導量子比特需要依靠工作在室溫中電子器件來控制和測量。典型的超導量子比特的躍遷能的變化頻率為GHz量級,需要可變且精準的微波信號生成和檢測來進行控制和測量。量子比特的數量增加時,需要的微波通道數量也線性增加。所以,必須設計一個可擴展、緊湊、有性價比,同時保有精度、速度和功能的量子比特控制系統。

除了傳統的上下變頻的微波電路外,基本量子比特控制系統還有由數模轉換器(DAC)、模數轉換器(ADC)和恒流源組成的;DAC生成的微波脈沖會進入制冷機,ADC把從制冷機出來的模擬信號數字化,電流源給量子比特提供偏置。一些早期的用于電子旋轉和超導量子比特的微波控制系統選用臺式的任意波形發生器(AWG)來生成微波[2-7]。而近來大家更喜歡使用現場可編程門陣列FPGA[8-15],因為它的通道數更多(即每個通道的成本更低),功能多,形態也更靈活。一般來說,每個量子比特需要兩個DAC通道來驅動;五個或以上的量子比特會共享一個額外的DAC通道,用于頻率復用讀出方案[16-18]。

Xilinx的FPGA家族——Zynq Ultrascale+片上射頻系統(RFSoC)[19]擁有很多適用于量子比特的控制和測量的特色,包括:單個芯片內多路獨立DAC和ADC通道、高采樣率、通道間同步能力。該器件內部還具備包含正交混頻器和48位數控振蕩器的數字上下變頻器。出于較高的集成度,RFSoC成本低、占用空間小,特別適合雷達[20]通信[21]和量子計算[22-24]等應用。

這里,我們基于多個互相同步的XCZU29DR FPGA板開發了一個可擴展系統,每個單板擁有16個6.554GS/s的DAC通道和16個2.058GS/s的ADC通道,工作時無需模擬I/Q混頻器。

II. 實現

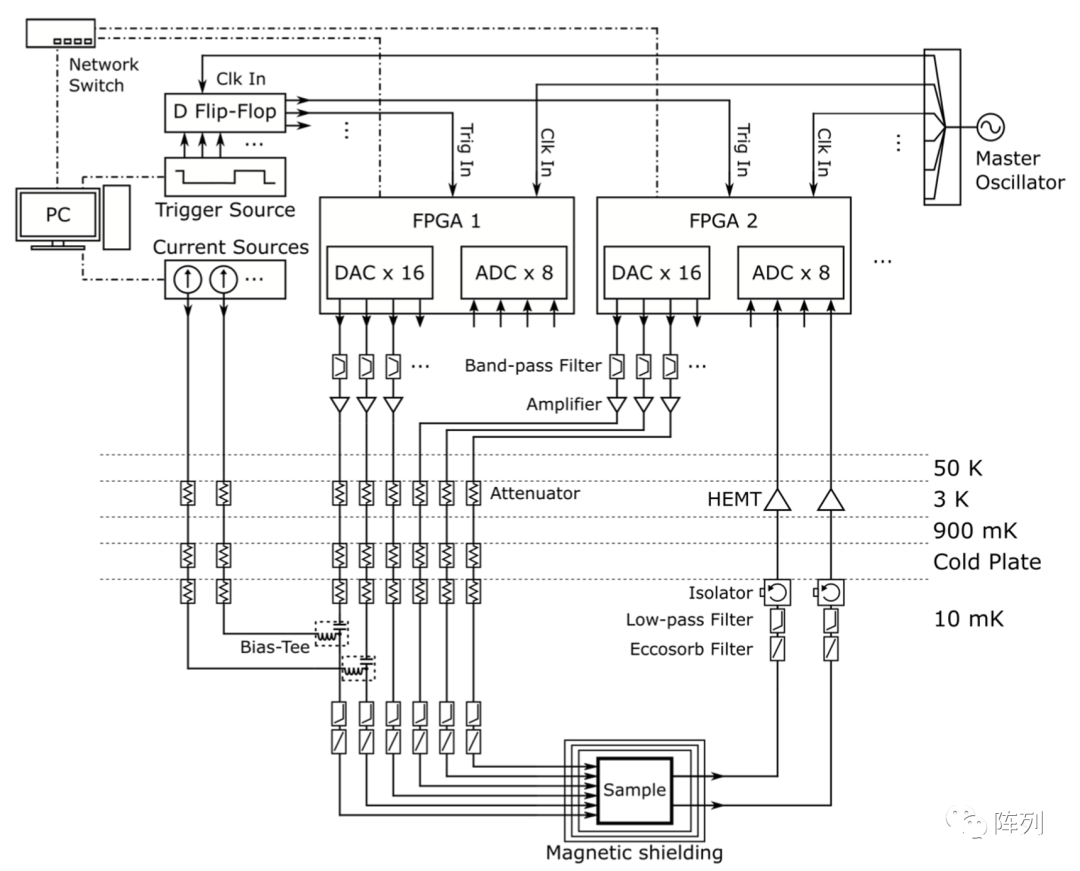

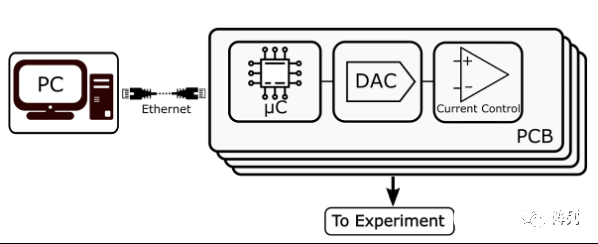

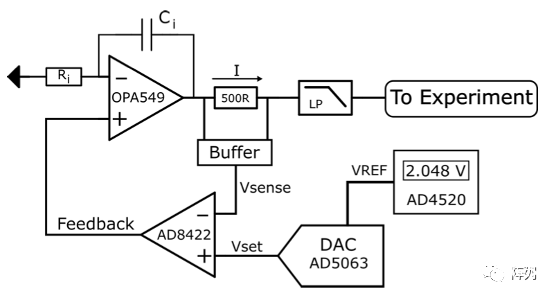

圖1. 總體電路示意圖

如圖1所示,裝置由若干部分組成。代號ICARUS-Q(可擴展量子處理器集成控制讀出單元)的FPGA板,運行Linux嵌入式內核,通過以太網接收命令和收發數據。在實驗中,DAC信號在高階Nyquist區[13]的鏡像實現GHz范圍的量子位轉換,并用ADC以較低采樣率對高頻信號直接采樣。使用一個主振蕩器和同步到該主振蕩器的觸發信號來讓多個FPGA板相互同步。對于可調超導量子比特,約瑟夫森結用DC-SQUID環來替代。這讓量子比特可用磁通量來偏置,該磁通量由靠近環路的一根電流線耦合過來的。為了支持這些特征,系統集成了低噪聲DC電流源來進行量子位偏置。FPGA板、觸發源和電流源都連接到計算機上。計算機上的監控程序負責與和云服務器通信以進行遠程實驗。

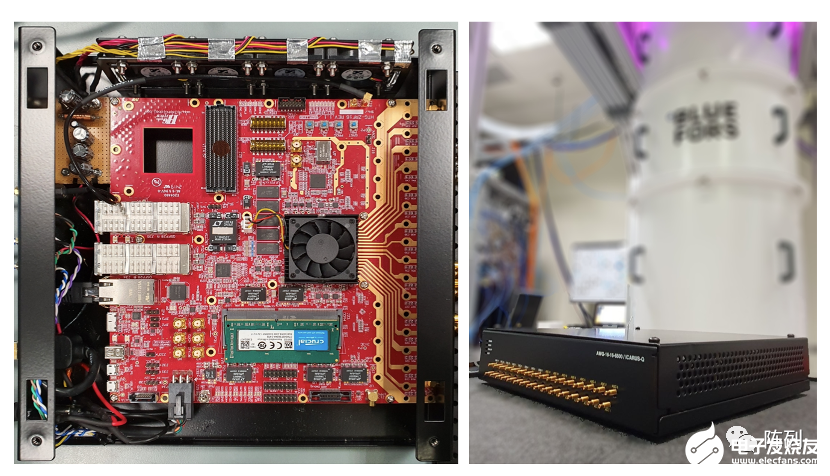

FPGA板采用貨架產品,單板包含一片XCZU29DR RFSoC器件(圖2)。該器件有16個十四位DAC差分接口和16個十二位ADC差分接口。所有DAC和ADC通道都使用巴倫(支持頻率10MHz-8GHz)和SSMC端口(支持頻率最高12.4GHz)轉換成單端信號接口。

圖2. ICARUS-Q的FPGA板

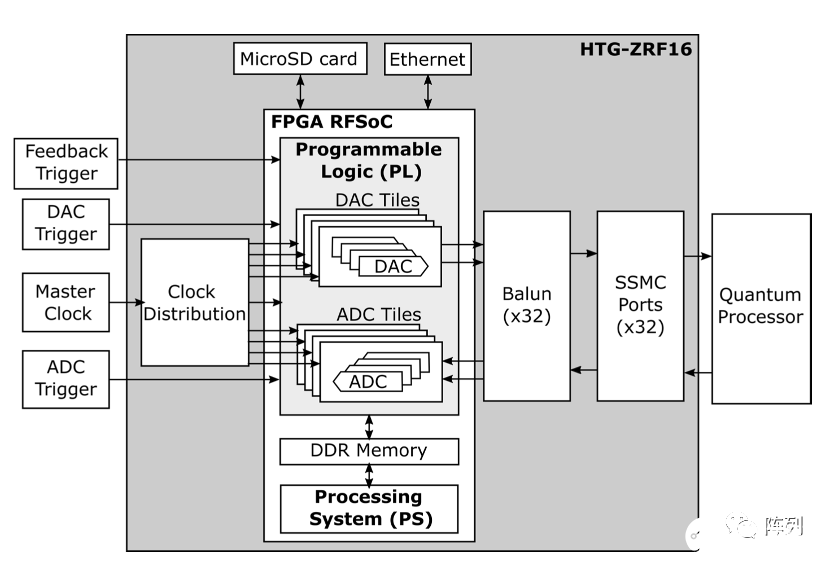

圖3. FPGA板的框圖和對外接口

在本裝置中,需要的DAC通道比ADC通道多。為了把更多有限的FPGA BlockRAM資源分配到DAC,我們把ADC活躍通道的數量減少到8個。FPGA板也有固定內存(4G)和SODIMM DDR4模塊(可達到16GB),在目前的設計中并沒有用到。

A. FPGA邏輯

FPGA邏輯負責讓數據在計算機和量子處理器之間流動(圖3)。在外觸發的激勵下,ADC和DAC執行數據和信號之間的轉換。系統中包含一個二級時鐘分配邏輯,用于ADC和DAC的相位同步。FPGA還連接到以太網、micro-SD卡、板上的DDR內存等設備和接口。

1. DAC波形生成的FPGA邏輯

任意波形產生依靠RFSoC DAC實現(見圖4)。芯片內的四個DAC片(DAC tiles)提供了總共16個DAC通道。為了在單個板內確保所有DAC的同步輸出,利用RFSoC內的多片同步邏輯來校準片間傳輸斜移。

波形數據載入PL-DDR內存后,開始產生DAC數據流。PL-DDR內存是一個硬件SODIMM內存模塊,和PL-FPGA相連。波形數據會進入每個DAC通道的AXI流型FIFO。由于內部BlockRAM的容量限制,單個FIFO能儲存的每通道波形樣本是65536個采樣點。

DAC波形回放支持環回功能。啟動后,它不需要從主機再次載入波形數據就能讓波形重新載入到FIFO,從而減少了一下次DAC回放重啟的時間。

波形數據載入到每個通道的FIFO后,系統會等待外部控制邏輯的外部觸發事件,然后開始DAC波形回放。外部控制邏輯的觸發信號適用所有DAC通道,所以所有信號可以從SSMC連接器同步輸出。外部控制邏輯同樣支持波形數據交換,8個上部通道的波形能交換到8個下部通道,以支持更高級的脈沖序列。

圖4. DAC波形生成的FPGA邏輯

2. ADC波形獲取的FPGA邏輯

波形獲取系統由RFSoC的8個ADC通道構成(圖5)。模擬輸入通過SSMC連接器注入RFSoC的ADC。ADC持續地把輸入波形數字化,并在外部觸發信號驅動下流入AXI流型FIFO。

圖5. ADC波形獲取的FPGA邏輯

每當外部觸發信號到達, 每個ADC通道的65536個數字化波形數據就會儲存在FPGA的FIFO中。儲存在FIFO中的數據會被轉移到外部DDR4 SODIMM,等待ZYNQ處理器系統(PS)的后續處理。根據后續分析的設置,數據可以以HEX或ASCII的文件格式儲存。獲取的數據完全轉移到ZYNQ處理器系統后,ADC會重新待命等待下一次觸發。

B. 微波的生成和檢測

DAC輸出的任意波形由65536個樣本以最大6.144GS/s的可變采樣率生成。在最大采樣率下,該數據量相當于波形時間長度約10μs。ADC會儲存同樣數量的樣本,但是采樣率為1.96608GS/s,相當于波形時長33μs。觸發DAC通道后,會有最小30μs的延遲,然后再觸發下一個脈沖。為了進一步評估DAC和ADC的性能,我們進行了相關的測試,以下是一些分析結果。

1. 任意波形生成

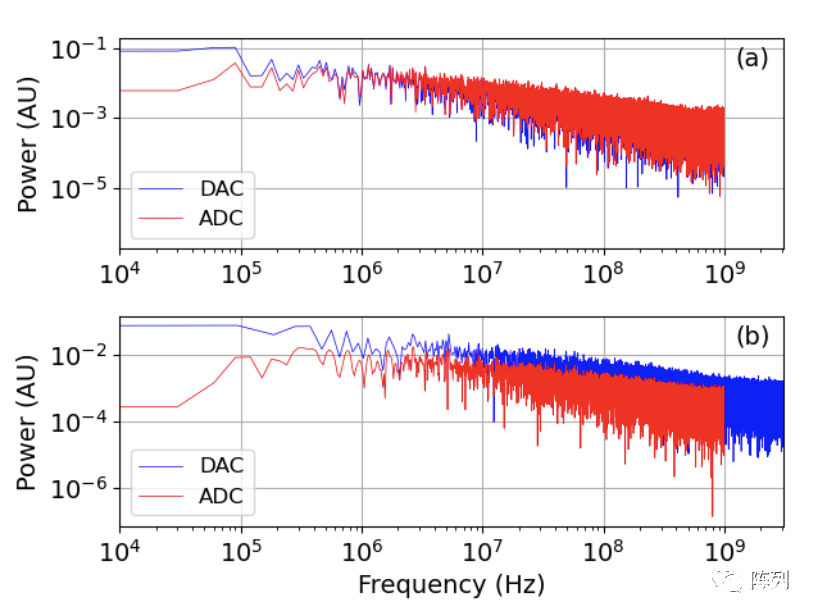

在一個典型的量子計算機實驗裝置中,通常會使用矩形或高斯形脈沖,但任意相位和振幅信號[27,28]的脈沖也會經常使用。一些量子信息處理應用要求使用無門控信號,比如最優控制理論[29-31]、絕熱量子計算、持續可變量子計算等[32]。為了驗證真實的任意波形生成能力,我們用粉紅噪聲測試了DAC,并把生成的信號和計算出來的波形數據點進行了比較(圖6)。粉紅噪聲波形是用Voss算法[33]生成的,DAC以兩個不同的采樣率1.96608GS/s、6.144GS/s生成信號。兩種波形都由ADC以1.96608GS/s進行采樣。

圖6. 粉紅噪聲的DAC生成和ADC采樣效果

在圖6(a) (b),DAC樣本和ADC數據分別在頻域內標出。除了1MHz以下,兩個頻譜包絡基本吻合。這主要是因為電路中巴倫器件的支持頻率范圍是10MHz-8GHz,低于10MHz的頻率都減弱了,類似于高通濾波器。在圖6(b)中,當DAC以6.0144GS/s運行時,DAC噪聲譜會達到3.072GHz的Nyquist頻率,而ADC因為欠采樣,其噪聲譜只能達到983.04MHz。此外,以6.144GS/s生成的信號只持續10μs左右(其余的ADC數據都接近0),這讓ADC頻域幅度偏低。

2. 高Nyquist區的性能評估

Shannon-Nyquist采樣理論指出可以在頻率低于一半采樣率的情況下正常生成或采樣一個信號。這個頻率閾值叫做Nyquist頻率。離散時間生成或采樣信號會產生鏡像,這些鏡像會在Nyquist頻率的倍數范圍重復反射展開[13,34]。頻域的每一段通常被叫做一個Nyquist區。經過精心設計,可以在不升級現有器件的情況下利用第一區以上的頻率區間[13,23,35]。

然而,其中會有一些掣肘因素。設時域內的電壓為:

受到重建波形r(t)的影響[13],v(t)的傅里葉變換是:

其中,R(ω)是一個由DAC運行模式決定的sinc函數[36]。這里使用的RFSoC支持兩個模式:非歸零(NRZ)模式和混合模式。傅里葉空間中相應的重建波形是兩個不同的sinc函數:

和

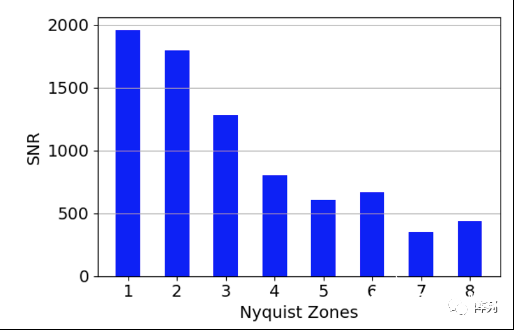

所以,使用ADC的高Nyquist區時,我們認為信噪比(SNR)會有一定程度的降低。為了研究這個問題,我們用ADC以1.96608GS/s去采樣高頻率區的各種信號,并在ADC的第一區內生成800MHz的鏡像。我們比較了微波合成器生成信號和RFSoC DAC發出信號的SNR。在這些測試中,DAC模式被設為普通模式(NRZ)。

RFSoC DAC的800MHz信號在ADC采樣率的第一Nyquist區,測得SNR≈2×103(見圖7)。7.06432GHz的信號,800MHz的第八Nyquist區鏡像,在典型量子比特躍遷頻率的相似范圍。在這個頻率下,測出的SNR約為4×102,第一區800MHz低5倍左右。

圖7. 用ADC測得的SNR

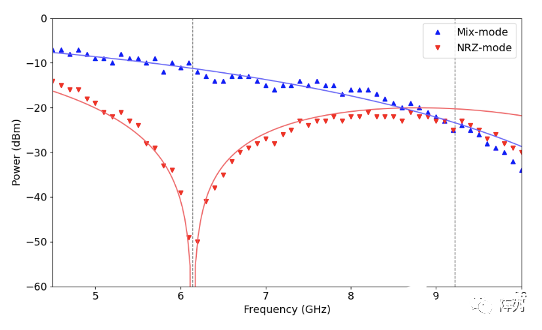

3. 功率和頻率的關系

使用高Nyquist區的方法會導致信號功率與頻率之間有關聯。超導量子比特需要在特定的頻率下控制和讀出的。我們需要研究DAC Nyquist區之間的功率變化關系。我們使用譜頻分析器測量了DAC輸出功率,譜頻分析器的范圍是4.5GHz到10GHz,這是超導量子比特及其諧振器的典型范圍[37,38]。結果如圖8。虛線是實測結果,實線是理論參考值。

圖8. 不同DAC工作模式的跨區間功率/頻率特性

對于普通模式(NRZ),如我們所預料,輸出功率在6.0144GHz時開始明顯下降。在7-10GHz之間,平均功率是-24.1±2.4dBm;在7-9GHz之間(按照標準偏差),會略微上升到-23.1±1.5dBm。與微波合成器或高端任意波形發生器相比,這樣的功率變化有點大,然而這種誤差幅度不會造成很大問題,因為量子比特會在固定頻率下周期性的被測量和校準。對于混合(Mix)模式,功率下降發生在12.288GHz(采樣率的兩倍)。這個模式的平均功率是7-10GHz之間-20.4±5.7dBm,7-9GHz之間-16.9±2.3dBm。輸出功率實測值在高頻率比理論值有明顯下降,主要原因是板上巴倫的支持頻率范圍(10MHz-8GHz)較低。

C. 反饋控制

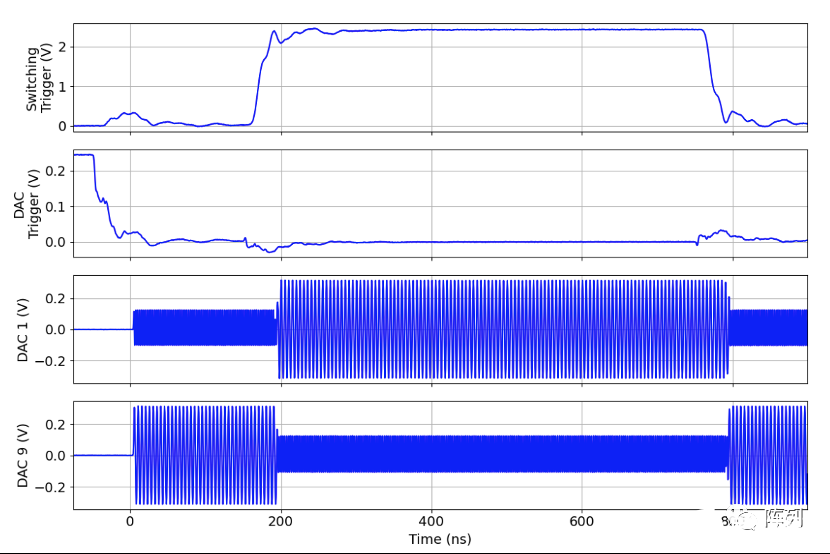

如果能實時切換波形(納秒級別),就能在量子電路運行時糾正量子比特狀態。RFSoC整合了硬件觸發信號切換波形的能力。收到切換觸發信號后,上部(0-8)DAC通道的輸出會在幾納秒內切換到下部(9-16)DAC通道(圖9)。使用快速讀出系統來激活切換觸發信號,糾正脈沖能根據量子比特狀態發送到合適的通道。

圖9. 用硬件觸發信號進行DAC回放切換

D. 多通道和多板操作

多個DAC和ADC通道需要在時間和相位同步的情況下輸出波形。我們必須做到兩種同步:(1)板內、通道間同步;(2)板間同步。

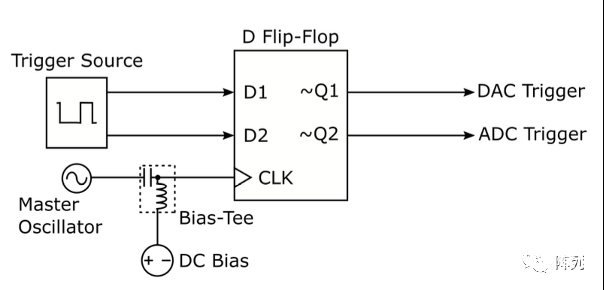

在板內,通道間同步是通過固件中的多片同步邏輯實現的,利用板上鎖相環把通道輸出鎖到外部基準時鐘。板間同步是通過把單個主振蕩器分配給所有板,這樣它們就有相同的基準時鐘信號來進行同步。用DAC和ADC同步生成和采樣波形,會用到硬件觸發器。使用D型觸發器把觸發信號同步到基準時鐘信號,這樣,收到觸發信號后,DAC(ADC)輸出波形的時間是一致、可預測的。

圖10. 同步電路

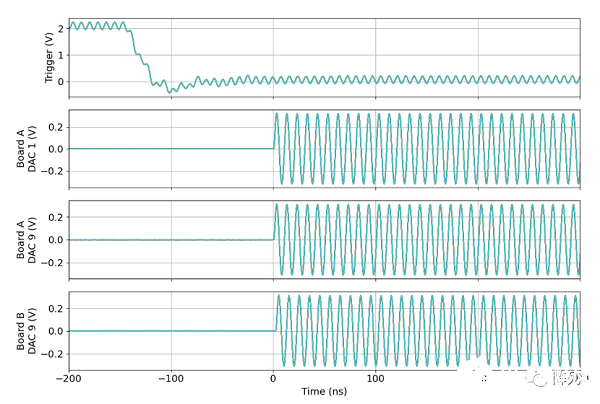

通過D觸發器驅動多片同步邏輯和觸發信號,兩塊RFSoC板上的DAC輸出是同步的(圖11)。觸發信號中的振蕩是時鐘信號從觸發器漏出造成的,但不影響RFSoC板的觸發接收。板B的微延遲是觸發分配路徑的長度不同造成的——通過精確匹配纜線長度就能糾正(或者在軟件中引入延遲)。

圖11. 示波器測得的同步觸發信號和多路DAC輸出

E. 低噪聲直流偏置電路

為了驅動用于調諧量子比特空閑頻率的偏置電流,我們開發了一個低噪聲雙極性電源,可通過主計算機的軟件控制。設計過程中我們考慮了這些因素:(1)超低噪聲:電流中的任何噪聲都會直接影響量子比特的相干性,電源的噪聲應該盡可能小。(2)超低電流漂移:電流中的任何漂移都會直接改變量子比特的特性,所以應該抑制漂移。(3)電流帶寬:基于設計,通過SQUID環的單位磁通量變化基本上會造成電流亞毫安到幾毫安之間的變化。電流源的電流范圍需要能夠支持生成至少一個單位的磁通量。此外,電流源應該是雙極的。(4)自動化:通過USB或以太網這樣的標準協議能控制電流源,這樣才能把它整合到軟件工作流程中。

圖12. 電流源的工作機理

1. 電流控制電路

在設計中,我們按照了文獻39,并作了一些修改。圖13是裝置的簡化圖,為了表達更清楚,供電電源、去耦電容、連接器等都省略了。

圖13.電流控制電路

電流控制器的核心是一個設置為積分器的運算放大器。使用取樣電阻Rsense來取樣放大器的輸出電流,把電流轉換成電壓Vsense。電壓Vset減去Vsense得到反饋信號,用于對電流的積分控制。此處,放大器自身就是一個積分器。電路的每個部分都必須低噪聲、低漂移。為了取樣電流,我們選擇500Ω溫度系數為±2ppm/℃的金屬箔電阻。為了獲取Vsense,首先使用零漂移運算放大器緩沖感測電阻的兩端。

為了生成設定電壓Vset,我們使用了分辨率為16位的串行接口DAC。并在雙極模式下運行該DAC,可把輸出電壓設定為-Vref到+Vref。這里Vref是提供給DAC的基準電壓。Vref要低噪聲、低漂移,這非常重要,因為它直接影響輸出電流。

2. 電流供給性能

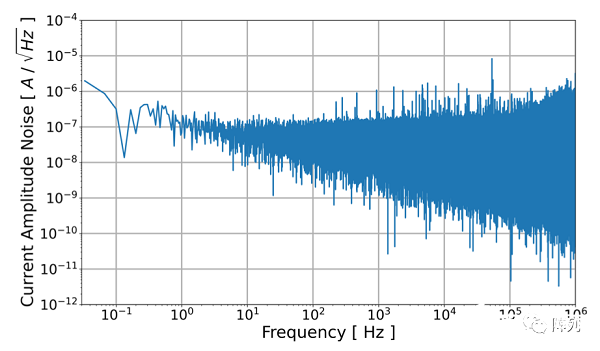

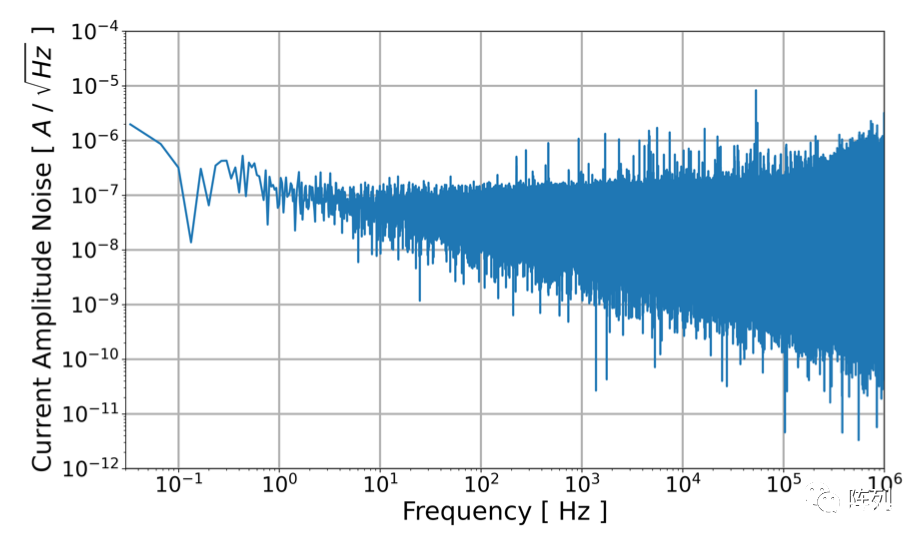

圖14. 電流源的高頻幅度噪音

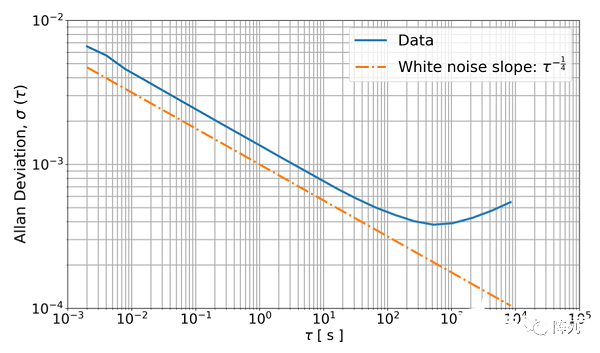

為了確定電源的噪音和穩定性,對電流幅度噪音進行了測量,并通過測量電源的艾倫偏差來觀察其長期表現。進一步的,我們通過調節超導量子比特的頻率驗證了電源性能。

把1mA的電流DC耦合到12位數字示波器的50Ω輸入端,以此來評估電流噪音和艾倫偏差。為了確定電流噪音,測得電壓以2MS/s的采樣率和30s的測試時間數字化。示波器的幅度范圍設為80mV,對應的電流分辨率為390nA。我們根據時域數據用快速傅里葉變換(FFT)計算了電流幅度噪音。圖14顯示了一個典型的電流幅度噪音頻譜。

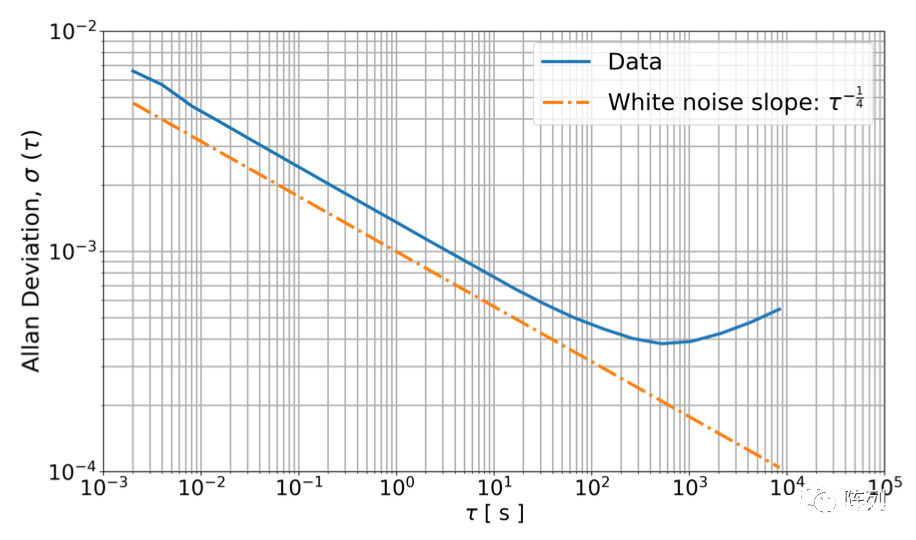

圖15. 電流源的穩定性

為了評估電源的穩定性,我們以500S/s的采樣率對電流進行了長期測量。示波器的滿幅度范圍設為40mV,對應的電流分辨率為195nA。根據時域數據計算了分數重疊阿倫偏差。圖15(藍線)顯示了18小時長期測量的電流阿倫偏差。可以看出來,平均500s的時間,源的零偏穩定性約為4×10-4。為了比較,我們還繪出了白噪音源斜線(點劃線)。對于較小的平均時間,電流源的阿倫偏差和白噪音是一致的。

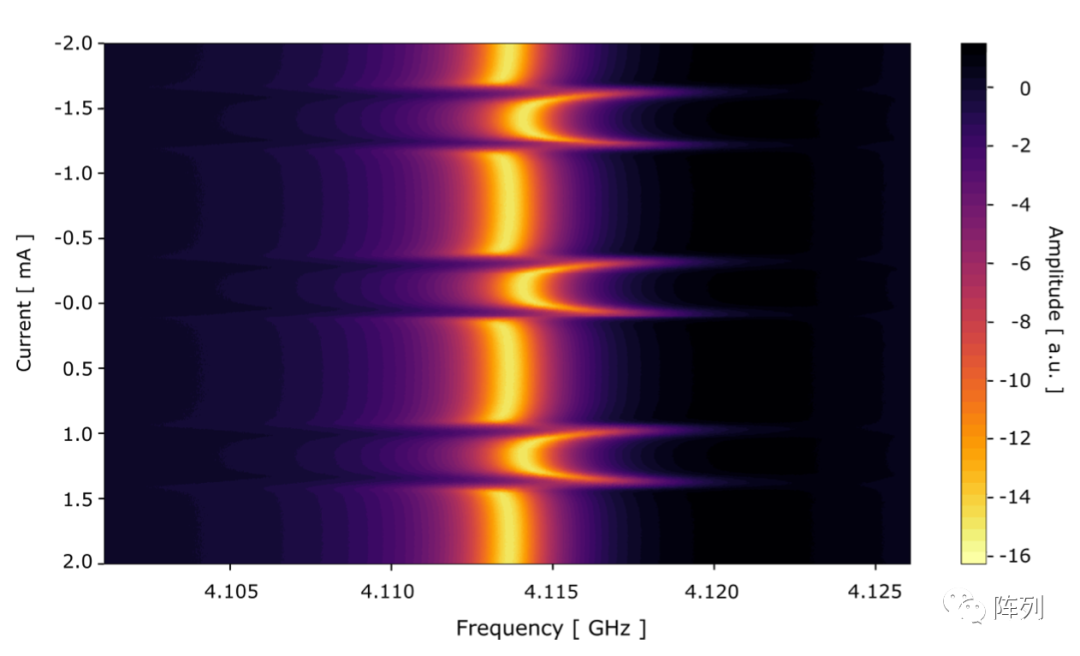

圖16. 超導Transmon量子位在不同偏置電流下的透射譜

確定了電源的噪聲表現后,我們測試了其偏置超導電路的能力。此例中,我們測量了一個腔的傳輸,這個腔被分散耦合到一個可調超導transmon量子位。由于是分散耦合,量子位頻率的變化會直接造成腔共振頻率的變化。我們測試了各種量子位偏置電流的腔透射譜。圖16是電流范圍-2.0mA到+2.0mA的腔透射2D圖。可以看到,共振器的頻率隨施加的偏置電流而發生變化[40]。在測試的電流范圍,我們觀察到大概有3個量子位頻率振蕩周期。這說明該電源適用于線性偏置超導量子位,而且噪音很低。

F.軟件控制和云訪問

本節介紹基于云端的RFSoC脈沖序列控制軟件的實現。

1.?軟件控制

如第II部分所述,本項目中的RFSoC板具有板卡配置、外時鐘鎖定、通道同步、FPGA啟動等命令。

這些命令由一臺中央計算機通過SSH協議執行。我們定義一個叫IcarusQ的Python類來完成用戶自定義波形數據的注入RFSoC、處理來自ADC的數據以及執行其它命令。這個類就成為了遠控端與RFSoC之間的接口。因為是Python寫的,所以可以與Python下的各種儀器包,例如PyVISA[41]、QCoDeSp[42]和PythonIVI[43]等,一起使用。

工作軟件與其它設備,例如RFSoC板的觸發源,通過特定的接口連接,能夠觸發ADC和DAC工作。在其上有定義了一個Python函數IcarusQ-Executor來運行脈沖實驗。該函數先設置用戶自定義觸發時序、重復次數和脈沖序列。然后,它啟動設備工作并且發出脈沖序列。最后,它返回FPGA ADC的數據。

2.云訪問

IcarusQ-Executor的輸入輸出被妥善定義后,我們就可以將其運行為云服務以實現遠程實驗。圖17中展示了云平臺遠程控制實驗裝置的方式。我們使用了Flask服務器[44]和Redis數據庫[45]作為用戶與工作機之間的媒介。當前的軟件部署還用到了Qibo框架[48]。

圖17. 云訪問軟件部署

III. 結論

我們的超導量子比特控制和測量裝置基于如下的設計思想:可擴展、盡量減少微波元件和儀器、可遠程控制。最終,我們選用了RFSoC器件,基于其16通道ADC和DAC實現高采樣率下的5-8GHz微波信號直接產生和檢測。這使得我們避免使用模擬IQ混頻器并省去了對混頻器的反復校準工作。我們還設計了一套將多個FPGA板同步在一個主時鐘并觸發所有ADC和DAC通道的電路。遠程訪問能力依靠服務器上的數據庫API實現,使得用戶可以遠程發送命令和獲取結果。

在短期內,有若干項改進正在被考慮。RFSoC上更多的功能將被用起來。隨著大量功能被集成入單芯片中,可以開始考慮將設備從室溫環境移入稀釋制冷機中[48]以獲得更好的信噪比并簡化與室溫系統的連接關系。為了獲得更多的采樣數據,我們還將研究內存優化技術,嘗試更快的DDR RAM。這些工作將在下一代更先進的器件發布后開展。

參考文獻

該文共列出48篇參考文獻,此處略。

——————————————————————

譯文就是這樣,聊聊感想。相信不少朋友會一拍大腿,哎呀這不就是一臺沖著冰箱發功的雷達嘛。

除了低噪聲電流源以外,這套裝置本質上是一個多通道的高速射頻信號播放和采集系統,而類似的技術在雷達、通信、儀器儀表等領域中是普遍用到的。文中提到的RFSoC器件當下就在各種陣列化高速信號采集播放和處理的相關領域中被廣泛用到,貨架產品形態層出不窮。

?

從學習和研究的角度看,通過本文,我們發現一臺量子計算的控制和測量裝置中除了量子本身相關的理論以外基本都是電子工程師耳熟能詳的概念,ADC、DAC、FPGA、奈奎斯特采樣定理、傅里葉變換、功率譜、白噪聲、阿倫偏差、恒流源、運算放大器、巴倫、偏置器等等。如果回望大學時所學,那不就是模擬電路、數字電路、可編程邏輯、數字信號處理、概率和統計等等課程嘛。所以,如前所說,科學是結構化的體系,先進的裝置和前沿的研究終究都會落實到各項成熟且具體的技術和工具。可以相信,我們過去和現在所學所想在未來也必有其價值。

審核編輯:黃飛

電子發燒友App

電子發燒友App

評論