Altera的Cyclone V FPGA目前是業(yè)界系統(tǒng)總成本和功耗最低的FPGA,那我們該怎樣為自己的設(shè)計選擇Altera Cyclone V FPGA?參考本文...

2013-02-26 10:34:36 2469

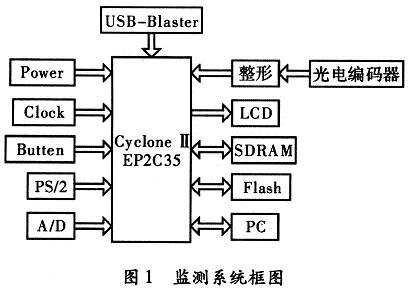

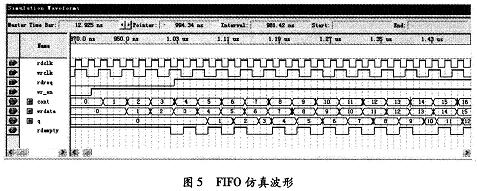

2469 為了實現(xiàn)激光-水聲淺海地形遙感探測中水聲信號的實時解調(diào)與處理,本文提出了一種基于FPGA的激光多普勒測振計信號采集與處理系統(tǒng)的設(shè)計方案。以Cyclone Ⅱ系列FPGA為核心控制模塊,結(jié)合

2013-10-29 10:10:02 2157

2157

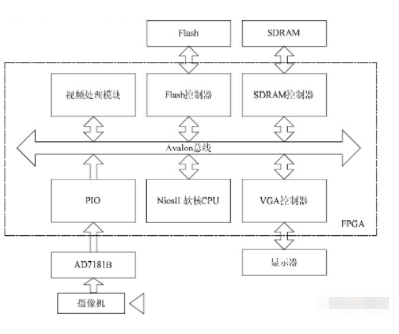

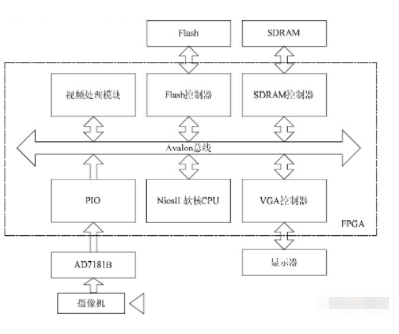

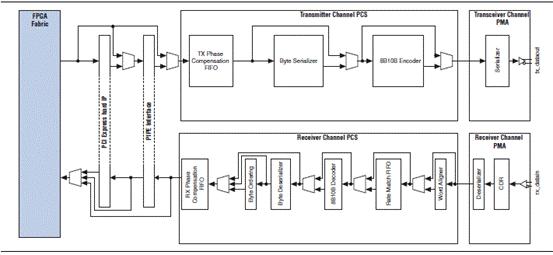

。整個系統(tǒng)除A/D 和D/A 采用專用芯片外,其余部分均在FPGA 上實現(xiàn)。視頻監(jiān)控系統(tǒng)的硬件設(shè)計框圖如下圖1 所示:

2020-12-30 09:48:37 780

780

Cyclone+IV+FPGA+器件系列概述

2012-08-18 00:11:05

本資料為:Cyclone II EP2C20原理圖_整張圖紙

2012-04-19 11:16:13

Altera 新的 Cyclone? IV 系列 FPGA 器件鞏固了 Cyclone 系列在低成本、低功耗 FPGA市場的領(lǐng)導(dǎo)地位,并且目前提供集成收發(fā)器功能的型號。Cyclone IV 器件旨在

2017-11-13 11:22:50

初學(xué),還請各位莫吐槽正在用EP4CE設(shè)電路原理圖,需要實現(xiàn)光纖通信,能否用EP4CE+光纖收發(fā)器芯片+光模塊實現(xiàn)?或者是中間還需要電路進行轉(zhuǎn)換?我知道Cyclone IV GX系列可以實現(xiàn),但沒有QFP封裝的求明白人給解釋一下,謝謝

2015-08-19 16:37:21

1、Cyclone IV E系列命名規(guī)則1、首先是EP4C,這是Cyclone IV的代號簡稱,只要是Cyclone IV系列都以EP4C開頭2、然后是一個字母E,E代表是E系列,Enhanced

2021-07-23 10:14:25

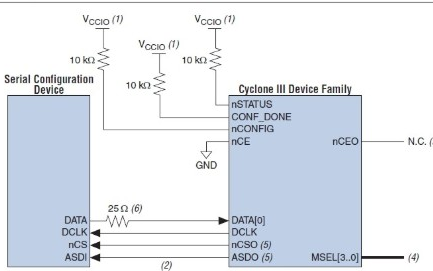

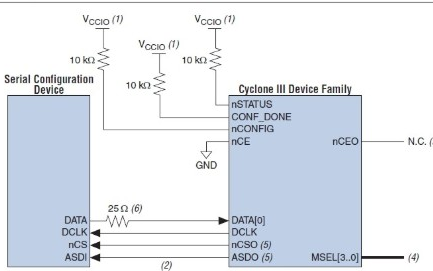

本章節(jié)介紹了 Cyclone? IV 器件的配置和遠(yuǎn)程系統(tǒng)更新。Cyclone IV (Cyclone IV GX和 Cyclone IV E)器件使用 SRAM 單元存儲配置數(shù)據(jù)。由于 SRAM

2017-11-14 10:13:30

本帖最后由 mr.pengyongche 于 2013-4-30 02:58 編輯

Cyclone_II_EP2C20_原理

2012-08-11 09:25:37

EP2C5型 FPGA/SOPC(NiosII)學(xué)習(xí)開發(fā)套件 V3.0 一、FPGA核心板:多種核心板供選擇,所采用的FPGA分別

2009-10-23 15:15:24

一、FPGA核心板:多種核心板供選擇,所采用的FPGA分別有:(1)Cyclone核心:EP1C12Q240C8、EP1C6Q240C8;(2)CycloneII核心

2009-11-02 18:55:54

我是FPGA初學(xué)者,想買塊板子學(xué)習(xí),各位大神來給建議吧,還有EP4CE15 CYCLONE4代這款芯片哪些稍微難一點項目?能做視頻處理嗎?謝謝

2012-09-14 20:16:33

我是剛剛開始學(xué)習(xí)FPGA,希望各位大蝦指教,EP2C35選用配置芯片EPCS16加載,時鐘選用40MHz,那么MSEL0,MSEL1應(yīng)該怎么接?我把兩個全部接到GND上,不能啟動,請指教一二。

2014-03-15 18:45:01

使用Cyclone3,或4系列的FPGA的LVDS接口,接AD輸出的并行信號,AD的采樣頻率250M,請問Cyclone3,或4系列的FPGA能否實現(xiàn),工作頻率能否達(dá)到,如EP4CE22F17I8或者EP3C25F256I7

2018-06-15 09:38:32

cyclone2 EP2C70內(nèi)部結(jié)構(gòu)原理圖誰有能奉獻一張嗎謝啦

2014-08-27 15:17:11

cyclone2 EP2C70內(nèi)部結(jié)構(gòu)原理圖誰有能奉獻一張嗎謝啦

2014-08-27 18:12:45

做了個cyclone4的板子,板上按鍵,led,232,fpga是ep4ce622c8,選擇中密度eqfp144封裝,在布局電源線的時候設(shè)置線寬20mil發(fā)現(xiàn),fpga的引腳寬度只有12mil,這種情況大家怎么處理?目前嘗試的2層板

2017-08-18 16:51:14

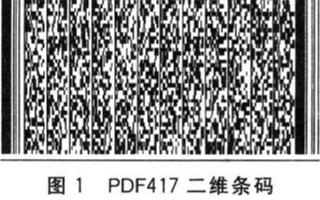

的要求和FPGA芯片設(shè)計的靈活性結(jié)合起來,采用Alter公司的CycloneⅡ系列FPGA芯片EP2C35F672C8,用VHDL語言編程,最后分別使用Quartus Ⅱ和Matlab軟件開發(fā)工具驗證實現(xiàn)

2010-05-28 13:38:38

FLASH、EMMC、SD卡等),在每次上電時讀取程序進行配置。2、功能分析項目中使用的FPGA型號是Altera公司(現(xiàn)屬于Intel)的Cyclone系列。在Altera的文檔[Cyclone

2021-12-27 07:32:47

本帖最后由 yicunyu 于 2016-2-29 16:04 編輯

DSP28335+FPGA(EP3C5E144C8N)cyclone 3系FPGA與DSP的完美結(jié)合尺寸僅比車票大一點

2016-02-29 15:41:44

主要內(nèi)容:在本課程設(shè)計中使用Altera公司的EP2C35系列的FPGA芯片,利用SOPC-NIOSII-EP2C35開發(fā)板的串口等資源,實現(xiàn)一個RS-232串口,通過串口線與PC相連,就可以完成

2014-07-08 09:21:32

日前,Altera發(fā)布新系列Cyclone IV FPGA ,延續(xù)其收發(fā)器技術(shù)的領(lǐng)先優(yōu)勢。當(dāng)前移動視頻、語音和數(shù)據(jù)訪問以及高質(zhì)量3D圖像對低成本帶寬需求與日俱增,與此同時,終端產(chǎn)品市場,如智能電話等

2019-07-31 06:59:45

從ASIC到FPGA的轉(zhuǎn)換系統(tǒng)時鐘設(shè)計方案

2011-03-02 09:37:37

本文以星載測控系統(tǒng)為背景,提出了一種基于 Actel Flash FPGA的高可靠設(shè)計方案。采用不易發(fā)生單粒子翻轉(zhuǎn)的 flash FPGA芯片,結(jié)合 FPGA內(nèi)部的改進型三模冗余、分區(qū)設(shè)計和降級重構(gòu),實現(xiàn)了高實時、高可靠的系統(tǒng)。

2021-05-10 06:58:47

靈活,能夠實現(xiàn)最佳成本和性能。LCD 電視生產(chǎn)商可以把Cyclone III FPGA 當(dāng)做協(xié)處理器,運行實時嵌入式操作系統(tǒng),控制所有的顯示設(shè)備。除了顯示中心控制以外,設(shè)計人員還可以在數(shù)據(jù)通道上結(jié)合

2008-10-16 15:44:08

Cyclone III系列型號為EP3C16F484C6N的FPGA作為控制器,以Micron公司生產(chǎn)的型號為MT47H16M16BG-5E(16M×16bit)的DDR2 SDRAM為存儲器。用一個IP核完成

2011-05-03 11:31:09

基于Cyclone系列芯片DDR實現(xiàn)

2012-08-17 11:22:34

基于EP1C3的進階實驗_Cyclone_PLL_Test2

2016-09-27 13:16:35

,減少了硬件資源的占用。該方案在Cyclone II FPGA 芯片EP2C35F484 上實現(xiàn),占用 20 070 個邏輯單元(少于60% 的資源),系統(tǒng)最高時鐘達(dá)到100 MHz 。與傳統(tǒng)的128 位數(shù)據(jù)路徑設(shè)計相比,更方便與處理器進行接口。

2012-08-11 11:53:10

,希望有興趣的同志和我聯(lián)系!FPGA以太網(wǎng)傳輸系統(tǒng)介紹:1)平臺:ALTERA FPGA,cyclone系列器件即可支持;2)系統(tǒng)架構(gòu):硬件:FPGA + PHY,其中MAC在FPGA中以IP方式實現(xiàn)

2014-06-19 12:04:25

,希望有興趣的同志和我聯(lián)系!FPGA以太網(wǎng)傳輸系統(tǒng)介紹:1)平臺:ALTERA FPGA,cyclone系列器件即可支持;2)系統(tǒng)架構(gòu):硬件:FPGA + PHY,其中MAC在FPGA中以IP方式實現(xiàn)

2014-06-19 12:06:43

設(shè)計中的分頻器沒有競爭冒險,可移植性強,占用的FPGA資源少。本設(shè)計在Al-tera公司的CycloneⅡ系列EP2C35型FPGA芯片中完全可實現(xiàn),結(jié)果表明設(shè)計是正確和可行的。由于分頻器應(yīng)用非常廣泛

2010-04-26 16:09:01

我目前在利用labview和cRIO9025、增量式光電編碼器進行發(fā)動機曲軸的扭振測量,前期主要是通過理論推導(dǎo)測量誤差的主要來源,然后就是測量軟件的編寫,希望各位大神多多交流,給小弟指導(dǎo)一下后續(xù)該從哪些方面入手。

2017-01-05 16:40:28

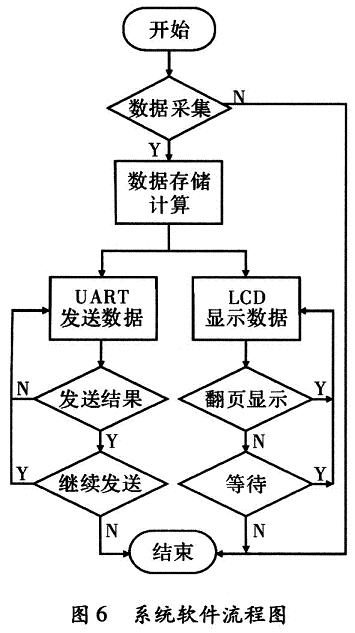

一種基于USB與藍(lán)牙芯片BC417143的無線溫度監(jiān)測系統(tǒng)的設(shè)計方案。并從硬件和軟件兩個方面介紹了系統(tǒng)的設(shè)計過程。實現(xiàn)了對溫度信息進行的無線數(shù)據(jù)采集。利用藍(lán)牙芯片作為無線收發(fā)模塊。DS18B20作為溫度數(shù)據(jù)采集。USB接口芯片作為與PC機的通信接口。簡化了電路設(shè)計并具有易擴展和組網(wǎng)的特點。

2021-02-01 06:10:45

如何用FPGA實現(xiàn)DVB碼流分析功能的嵌入式設(shè)計方案?

2021-04-28 06:19:10

本文提出了基于SOPC(System On Programmable Chip)的設(shè)計方案[2],利 用其配置靈活、擴展性強、接口豐富等優(yōu)點,以Altera 公司的Cyclone II 系列FPGA 為基 礎(chǔ),設(shè)計傳感器節(jié)點數(shù)據(jù)采集存儲系統(tǒng),降低了設(shè)計的風(fēng)險,完善了傳感器節(jié)點功能要求。

2021-05-06 08:28:58

買了一個FPGA板子,Cyclone IIIEP3C25F324 沒有視頻教程,也沒有電路圖,不知道如何構(gòu)建內(nèi)核,請各位大神指點哪里有我這個板子的教程嗎?

2013-08-28 16:27:31

誰知道FPGA CYCLONE IV E系列板上晶振的使用,我用了一個PLL,需要配置引腳 inclk0,怎么連接到開發(fā)板上的50Mhz晶振

2014-11-24 19:15:52

誰知道FPGA CYCLONE IV E系列板上晶振的使用,我用了一個PLL,需要配置引腳 inclk0,怎么連接到開發(fā)板上的50Mhz晶振

2014-11-24 19:22:56

本文給出了基于Altera公司的cyclone系列FPGA芯片EP1C12-240PQFP的2M誤碼測試儀的設(shè)計方案。

2021-05-06 08:32:38

討論了一種基于FPGA的64點FFT處理器的設(shè)計方案,輸入數(shù)據(jù)的實部和虛部均以16位二進制數(shù)表示,采用基2DIT-FFT算法,以Altera公司的QuartusⅡ軟件為開發(fā)平臺對處理器各個的模塊進行設(shè)計,在Stratix系列中的EP1S25型FPGA通過了綜合和仿真,運算結(jié)果正確。

2021-04-29 06:25:54

本文提出了一種基于FPGA的誤碼率測試儀的方案,使用一片Altera公司的Cyclone系列的FPGA(EP1C6-144T)及相關(guān)的外圍電路,實現(xiàn)誤碼測試功能,主控計算機可以通過FPGA內(nèi)建的異步串行接口(UART)配置誤碼測試儀并讀取誤碼信息,由計算機完成誤碼分析。

2021-05-08 06:13:47

TPMS主要有哪幾種實現(xiàn)方式?如何選用新型送器(遙控鑰匙)與接收器中幾種芯片?一種基于LIN總線分布式實時輪胎壓力監(jiān)測系統(tǒng)的設(shè)計方案

2021-05-13 06:03:12

本科畢業(yè)生要求設(shè)計一個基于fpga導(dǎo)航樣機設(shè)計,給了我一個ep2c35f484c6芯片原理圖,我看不,求幫助。

2017-03-28 10:44:19

求黑金開發(fā)板 FPGA CYCLONE IV E系列EP4CE15F17C8配套光盤資料?

2014-11-24 19:39:00

用Cyclone IV EP4CE6系列做串口通信,板子是自己畫的,50M晶振,用示波器打過,正常。程序是正點原子例程改編的。但是用Signal Tap 看波形時出現(xiàn)問題,在接收數(shù)據(jù)計數(shù)時發(fā)現(xiàn)比正常

2019-07-26 19:35:57

/1312205552_74783276.jpg][/url]本系統(tǒng)采用藍(lán)牙模塊實現(xiàn)與內(nèi)嵌藍(lán)牙功能的外部設(shè)備的數(shù)據(jù)交換。為減小系統(tǒng)體積、減輕系統(tǒng)質(zhì)量和降低功耗,本藍(lán)牙模塊采用Class-2設(shè)計方案,USB輸出,傳輸距離為10 m

2011-08-02 11:23:10

CAS。我們的設(shè)計(圖1)采用Altera公司Cyclone III系列型號為EP3C16F484C6N的FPGA作為控制器,以Micron公司生產(chǎn)的型號為MT47H16M16BG-5E(16M

2019-05-31 05:00:05

,采用核心板和底層板結(jié)合的硬件結(jié)構(gòu)。系統(tǒng)原理框圖如圖1所示,FPGA 芯片采用Atera 公司的Cyclone Ⅱ 系列EP2C5Q208C8N,它采用90 nm 工藝,具有4 608個邏輯單元。此外

2019-06-24 07:16:30

基FPGA Cyclone II_EP2C5 EP2C8的頻率計

基FPGA_Cyclone_II_EP2C5/EP2C8的頻率計

功能描述:按4*4鍵盤上的1,2,3...號按鍵可依次測出 25000000Hz ,12500000Hz ....的分

2008-11-30 12:17:01 87

87 介紹了一種基于FPGA 的LED 大屏設(shè)計方案,采用自頂向下的設(shè)計思想,設(shè)計了基于FPGA 的雙口RAM 和掃描控制電路,解決了傳統(tǒng)LED 大屏設(shè)計中,控制系統(tǒng)復(fù)雜﹑可靠性差的問題。關(guān)鍵

2009-06-15 09:34:14 26

26 EP4CE10F17C8N,Cyclone IV FPGA設(shè)備,INTEL/ALTERAEP4CE10F17C8N,Cyclone IV FPGA設(shè)備,INTEL

2023-02-20 17:00:57

EP4CE10F17I7N,Cyclone IV FPGA設(shè)備,INTEL/ALTERAEP4CE10F17I7N,Cyclone IV FPGA設(shè)備,INTEL

2023-02-20 17:03:19

EP4CE6F17C8N ,Cyclone IV FPGA設(shè)備,INTEL/ALTERAEP4CE6F17C8N ,Cyclone IV FPGA設(shè)備,INTEL

2023-02-20 17:05:47

本文介紹一種基于FPGA 和ARM9 的激光測距系統(tǒng)的硬件原理設(shè)計和軟件設(shè)計方案。該方案采用SICK 公司的戶外型激光傳感器LMS221,和ALTERA 公司cyclone 系列的EP1C12Q240I7 FPGA 芯片。控制系統(tǒng)

2009-12-19 16:00:25 89

89 本文使用FPGA芯片來模擬實際的乒乓球游戲。本設(shè)計是基于Altera公司的FPGA Cyclone II芯片EP2C35的基礎(chǔ)上實現(xiàn),運用Verilog HDL語言編程,在Quartus II軟件上進行編譯、仿真,最終在Altera公司的DE2

2010-02-24 14:51:17 86

86 本文使用FPGA芯片來模擬實際的乒乓球游戲。本設(shè)計是基于Altera公司的FPGA Cyclone II芯片EP2C35的基礎(chǔ)上實現(xiàn),運用Verilog HDL語言編程,在Quartus II軟件上進行編譯、仿真,最終在Altera公司的DE2

2010-07-17 18:08:41 56

56 本文介紹一種基于FPGA和ARM9的激光測距系統(tǒng)的硬件原理設(shè)計和軟件設(shè)計方案。該方案采用SICK公司的戶外型激光傳感器LMS221,和ALTERA公司cyclone系列的EP1C12Q240I7 FPGA芯片。控制系統(tǒng)采用ARM+

2010-07-21 17:38:26 46

46 摘要:本文討論了Cyclone系列器件的不同配置方法,提出一種單片機結(jié)合FLASH存儲器的被動串行配置方案。關(guān)鍵詞:FPGA;FLASH;PS;Cyclone

2010-08-13 12:04:09 64

64 Altera新Cyclone IV FPGA拓展了Cyclone FPGA系列

Altera拓展其成功的Cyclone FPGA系列并延續(xù)其收發(fā)器技術(shù)領(lǐng)先優(yōu)勢,于今天發(fā)布Cyclone IV FPGA新系列。在移動視頻

2009-11-04 08:46:38 1221

1221 低功耗Cyclone IV FPGA

Altera公司宣布,開始批量發(fā)售Cyclone IV FPGA。公司還宣布開始提供基于Cyclone IV GX的收發(fā)器入門開發(fā)套件。Altera的Cyclone IV FPGA設(shè)計用于無線、固網(wǎng)、廣播

2010-03-31 10:42:42 1432

1432 提出了一種基于FPGA并利用Verilog HDL實現(xiàn)的CMI編碼設(shè)計方法。研究了CMI碼型的編碼特點,提出了利用Altera公司CycloneⅡ系列EP2C5Q型號FPGA完成CMI編碼功能的方案。在系統(tǒng)程序設(shè)計中,首先產(chǎn)生m序列,然后程序再對m序列進行CMI碼型變換。在CMI碼型變換過程中

2011-01-15 15:44:04 67

67 本設(shè)計采用MCU和FPGA相結(jié)合的系統(tǒng)方案,以AVR單片機ATmega128和Altera公司的Cyclone系列EP1C3T100為核心,充分發(fā)揮各自的優(yōu)勢.

2011-08-04 10:39:32 2675

2675

本文將著重介紹運用FPGA技術(shù)實現(xiàn)基群與二次群之間復(fù)接與分接系統(tǒng)的總體設(shè)計方案。

2011-08-15 17:00:27 1300

1300 介紹了一種基于FPGA 的LED 大屏設(shè)計方案,采用自頂向下的設(shè)計思想,設(shè)計了基于FPGA 的雙口RAM 和掃描控制電路,解決了傳統(tǒng)LED 大屏設(shè)計中,控制系統(tǒng)復(fù)雜﹑可靠性差的問題。

2012-03-02 16:48:46 34

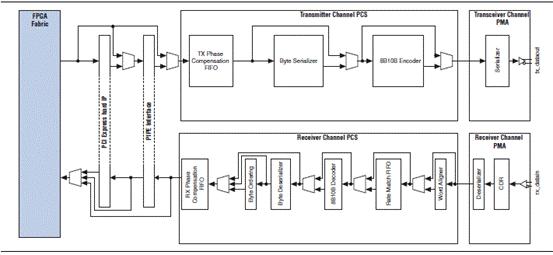

34 Altera 公司的Cyclone IV 系列 FPGA 包括兩個系列:Cyclone IV E和Cyclone IV GX,具有低成本、低功耗的FPGA 架構(gòu),6 K 到150 K 的邏輯單元,高達(dá)6.3 Mb 的嵌入式存儲器,小于1.5 W 的總功耗;Cyclone IV GX 器件提供

2012-05-31 09:08:54 8725

8725

Altera的Cyclone V FPGA實現(xiàn)了業(yè)界最低的系統(tǒng)成本和功耗,其性能水平滿足了您突出大批量應(yīng)用優(yōu)勢的需求。從三種型號中進行選擇: (1)只提供邏輯的Cyclone V E FPGA (2)具有3.125-Gbps收發(fā)

2012-09-04 14:34:07 13248

13248 針對傳統(tǒng)高爐TRT頂壓控制系統(tǒng)的不足,提出一種基于FPGA實現(xiàn)的系統(tǒng)設(shè)計方法,以EP2C35 FPGA作為主控芯片,采用模塊化的設(shè)計思想,實現(xiàn)了高爐頂壓的模糊自適應(yīng)PID控制。實驗結(jié)果表明,

2012-10-16 15:58:42 25

25 電子發(fā)燒友網(wǎng)核心提示:本文提出了基于FPGA的噴油器脈寬處理的設(shè)計方案。在QuatusII自帶的仿真軟件下可以觀測到設(shè)置不同的脈寬控制參數(shù)可以達(dá)到輸出信號的占空比可調(diào)。整個系統(tǒng)下

2012-11-09 16:04:05 2287

2287 通過分析電視測角儀的性能測試需求,結(jié)合視頻圖像圖像處理技術(shù),提出了以 EP2C35 為核心的視頻檢測系統(tǒng)設(shè)計方案,通過對CCD 采集到的模擬環(huán)境的視頻圖像信號進行數(shù)字化處理,結(jié)合

2013-05-06 18:21:57 21

21 基于EP1C3的進階實驗cyclone_PLL_Test2

2016-10-27 18:20:05 10

10 Cyclone FPGA系列簡介

2016-12-26 22:02:46 0

0 基于EP2C35的DSP陣列板通信接口設(shè)計與實現(xiàn)

2017-10-19 14:12:34 14

14 FPGA EP2C35A484開發(fā)試驗板說明

2017-10-28 16:05:33 0

0 。對設(shè)計進行綜合,下載到FPGA中就可以設(shè)計一個具有特定功能的嵌入式處理器。本設(shè)計采用Altera公司的FPGA—EP2C35,引人嵌入式軟核處理器NIOSⅡ作為系統(tǒng)的主控制器,結(jié)合ARINC429專用器件和其他外圍設(shè)備實現(xiàn)數(shù)據(jù)的收發(fā)功能

2018-07-17 15:56:00 776

776

于 Cyclone EP1C6240C8 FPGA的ADS2807接口程序,主要用來使用FPGA控制ADS2807的采集。 采用FPGA來模擬ADS2807的時序來實現(xiàn)控制功能。 提供采樣頻率控制、AD通道轉(zhuǎn)換、采樣數(shù)據(jù)緩存等功能。

2018-01-31 16:46:54 10

10 Altera 新的Cyclone?IV 系列 FPGA 器件鞏固了Cyclone 系列在低成本、低功耗FPGA市場的領(lǐng)導(dǎo)地位,并且目前提供集成收發(fā)器功能的型號。Cyclone IV 器件旨在用于大批量,成本敏感的應(yīng)用,使系統(tǒng)設(shè)計師在降低成本的同時又能夠滿足不斷增長的帶寬要求。

2018-11-19 08:35:00 9473

9473

Altera 新的Cyclone? IV 系列 FPGA 器件鞏固了Cyclone 系列在低成本、低功耗FPGA市場的領(lǐng)導(dǎo)地位,并且目前提供集成收發(fā)器功能的型號。Cyclone IV 器件旨在用于大批量,成本敏感的應(yīng)用,使系統(tǒng)設(shè)計師在降低成本的同時又能夠滿足不斷增長的帶寬要求。

2018-11-22 08:00:00 46

46 很多人第一次接觸Altera Cyclone系列FPGA的時候,可能會被其復(fù)雜的專用管腳給搞混淆,在這里我們Altera Cyclone系列FPGA的專用管腳一一列出供您參考,希望對您的設(shè)計有幫助。

2020-01-26 17:50:00 9729

9729

時,通過在NiosII處理器下編寫C程序運行,也可以使用硬件模塊來加速。本系統(tǒng)綜合兩種實現(xiàn)思路,采用高性價比的Cyclone II EP2C35系列FPGA實現(xiàn),系統(tǒng)總體結(jié)構(gòu)如圖2所示。

2020-07-21 17:14:20 1786

1786

基于FPGA的嵌入式信號處理系統(tǒng)設(shè)計方案

2021-06-02 11:04:33 0

0 基于FPGA的嵌入式信號處理系統(tǒng)設(shè)計方案

2021-06-02 11:04:33 0

0 本文詳細(xì)描述了FPGA實現(xiàn)圖像去霧的實現(xiàn)設(shè)計方案,采用暗通道先驗算法實現(xiàn),并利用verilog并行執(zhí)行的特點對算法進行了加速;

2023-06-05 17:01:45 862

862

齒輪的齒數(shù)為N,再測出轉(zhuǎn)n個齒的時間為tn,tn在時間內(nèi)軸系的扭角為

齒輪的齒數(shù)為N,再測出轉(zhuǎn)n個齒的時間為tn,tn在時間內(nèi)軸系的扭角為

電子發(fā)燒友App

電子發(fā)燒友App

評論