2.1 時域分析方法下面按著電容充放電和電感充放電進行時域分析。時域分析的過程是按著輸入電壓的高與低,分析電路里電容電壓和電感電流的變化過程。這個分析過程可以按著大多課本上面所講述的過程分析

2018-02-07 08:44:11 61294

61294

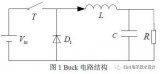

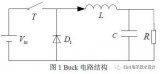

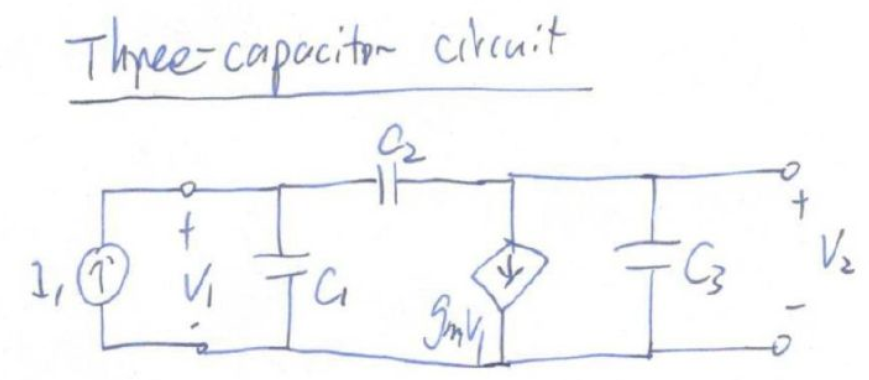

Buck 電路是最常見的電路,具體電路結(jié)構(gòu)如圖所示。

2023-04-12 09:04:20 715

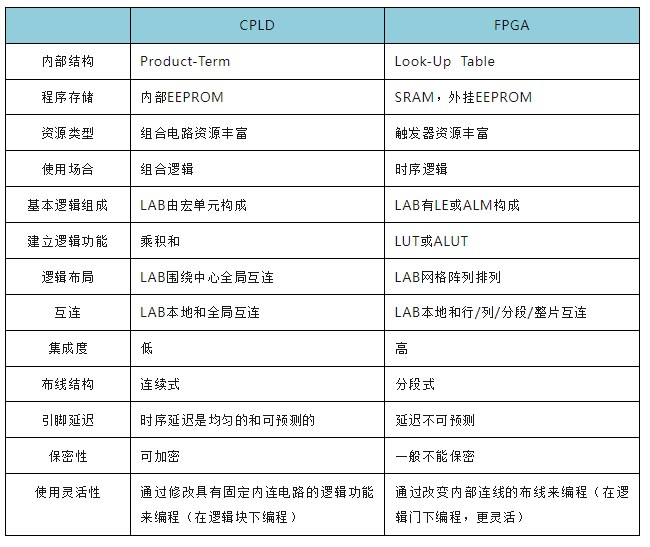

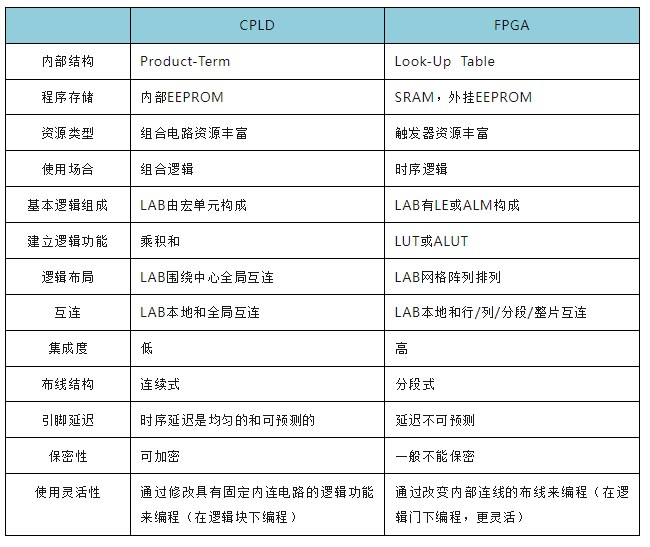

715 CPLD與FPGA區(qū)別有哪些?電子發(fā)燒友網(wǎng)編輯跟大家一起分享。本站小編將從結(jié)構(gòu)、系統(tǒng)、設(shè)計技巧、廠商命名法則等幾個方面來為大家闡述和分析CPLD與FPGA的區(qū)別。

2012-11-19 16:39:52 8651

8651 CPLD與FPGA對比分析哪個好?

2021-06-21 06:10:12

,CPLD發(fā)展更為迅速,不僅具有電擦除特性,而且出現(xiàn)了邊緣掃描及在線可編程等高級特性。較常用的有Xilinx公司的EPLD和Altera公司的CPLD。2. FPGAFPGA通常包含三類可編程資源:可編程

2009-09-29 09:38:32

CPLD與FPGA的對比分析哪個好?

2021-11-05 08:20:40

CPLD和FPGA的區(qū)別是什么?

2013-07-25 16:26:48

1.處理器上有64個可復(fù)用的IO口,我們需要64個IO口,因為是復(fù)用的,我么也會用到部分復(fù)用功能,所以IO口不夠用,有人提出用CPLD或FPGA擴展,這樣擴展的IO的速度與處理器的IO有區(qū)別嗎?

2023-04-23 14:10:40

FPGA CPLD同步設(shè)計若干問題淺析摘要:針對FPGA/CPLD同步設(shè)計過程中一些容易被忽視的問題進行了研究,分析了問題產(chǎn)生的原因、對可靠性的影響,并給出了解決方案。關(guān)鍵詞:FPGA/CPLD

2009-04-21 16:42:01

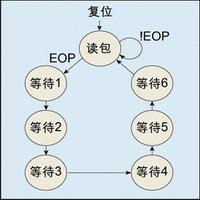

]圖1]3 基于CPLD 的FPGA 加載方案3.1]在 設(shè)備端通信產(chǎn)品中,基于CPLD 的FPGA 從并加載框如圖2 所示,配置數(shù)據(jù)存儲在FLASH 中,且在加載數(shù)據(jù)之前,CPU 通過局部總線和雙倍

2019-07-12 07:00:09

FPGA與CPLD的區(qū)別是什么,他與單片機的區(qū)別呢

2012-10-07 22:01:57

FPGA與CPLD的辨別和分類主要是根據(jù)其結(jié)構(gòu)特點和工作原理。通常的分類方法是:將以乘積項結(jié)構(gòu)方式構(gòu)成邏輯行為的器件稱為CPLD,如Lattice的ispLSI系列、Xilinx的XC9500系列

2019-07-01 07:36:55

FPGA與CPLD的區(qū)別

盡管很多人聽說過CPLD,但是關(guān)于CPLD與FPGA之間的區(qū)別,了解的人可能不是很多。雖然FPGA與CPLD都是“可反復(fù)編程的邏輯器件”,但是在技術(shù)上卻有一些差異。簡單

2011-09-27 09:49:48

可以很快進入市場。許多設(shè)計人員已經(jīng)感受到CPLD容易使用、時序可預(yù)測和速度高等優(yōu)點,然而,在過去由于受到CPLD密度的限制,他們只好轉(zhuǎn)向FPGA和ASIC。現(xiàn)在,設(shè)計人員可以體會到密度高達數(shù)十萬門

2012-10-26 08:10:36

和CPLD最大的區(qū)別是他們的存儲結(jié)構(gòu)不一樣,這同時也決定了他們的規(guī)模不一樣。但是從使用和實現(xiàn)的角度來看,其實他們所使用的語言以及開發(fā)流程的各個步驟幾乎是一致的。對于大多數(shù)的初學(xué)者來說,學(xué)FPGA還是

2019-02-21 06:19:27

FPGA與CPLD的區(qū)別是什么?Latch和Register區(qū)別在哪?行為描述中Latch如何產(chǎn)生的?

2021-09-22 07:55:00

FPGA與CPLD的概念及其區(qū)別

2018-08-15 15:46:16

器件。內(nèi)部基本結(jié)構(gòu)為“與或陣列”。因為任意一個組合邏輯都可以用“與—或”表達式來描述,所以該“與—或陣列”結(jié)構(gòu)有利于實現(xiàn)大量的組合邏輯功能。簡單的與或陣列 CPLD邏輯框圖 CPLD和FPGA

2020-08-28 15:41:47

范疇,它的硬件(FPGA)是可編程的,是一個通過硬件描述語言在FPGA芯片上自定義集成電路的過程;二者最大的區(qū)別:單片機(無論哈佛總線結(jié)構(gòu)或者馮諾依曼結(jié)構(gòu))均為取出指令->執(zhí)行,指令是順序執(zhí)行的(即使是中斷,其發(fā)生后的中斷服務(wù)程序也是順序執(zhí)行的);而FPGA(包括CPLD)是基于邏輯門和觸發(fā)器

2021-07-13 09:49:08

FPGA和CPLD到底有什么區(qū)別,還有VHDL,一直分不清他們有什么差別。求具體例子說明

2023-04-23 11:49:52

用“與—或”表達式來描述,所以該“與或陣列”結(jié)構(gòu)能實現(xiàn)大量的組合邏輯功能) 簡單的“與或”陣列:(PAL、GAL、CPLD) 含查找表的邏輯單元:(FPGA) CPLD和FPGA的主要區(qū)別

2020-07-16 10:46:21

和CPLD最大的區(qū)別是他們的存儲結(jié)構(gòu)不一樣,這同時也決定了他們的規(guī)模不一樣。但是從使用和實現(xiàn)的角度來看,其實他們所使用的語言以及開發(fā)流程的各個步驟幾乎是一致的。對于大多數(shù)的初學(xué)者來說,學(xué)FPGA還是

2015-03-12 13:54:42

規(guī)模時設(shè)計成本低以及設(shè)計周期短等優(yōu)勢。簡單地比較了現(xiàn)在市場上的電子器件之后,我們來詳細地分析一下MCU與FPGA之間的區(qū)別:MCU又稱為單片機,它為8位的微控制器,主要用在工業(yè)控制,FPGA則為

2020-06-23 15:04:14

用vhdl實現(xiàn)cpld配置fpga,配置成功后在usermode下設(shè)置一個重新配置信號,當(dāng)信號有效時對fpga進行重新配置;fpga配置程序放在flash內(nèi);現(xiàn)在遇到的問題是,上電cpld能夠正常配置fpga并且進入usermode ,但是加上重新配置語句過后就不能成功配置fpga,求高人指點~

2013-01-17 22:35:39

TVS管是一種限壓保護器件。其作用與壓敏電阻很類似。也是利用器件的非線性特性將過電壓鉗位到一個較低的電壓值實現(xiàn)對后級電路的保護。TVS管的主要參數(shù)有反向擊穿電壓、最大鉗位電壓、瞬間功率、結(jié)電容及響應(yīng)時間等。TVS管的響應(yīng)時間可以達到ps級,是限壓型浪涌保護器件中最快的。用于電子電路的過電壓保護時,其響應(yīng)速度都可滿足要求。TVS管的結(jié)電容根據(jù)制造工藝的不同,大體可分為兩種類型:1、高結(jié)電容型TVS管的結(jié)電容一般在幾百到幾千nF的數(shù)量級;2、低結(jié)電容型TVS管的結(jié)電容一般在pF到幾十pF的數(shù)量級。一般分立式TVS管的結(jié)電容都較高,表貼式TVS管中兩種類型都有。在高頻信號線路的保護中,應(yīng)主要選用低結(jié)電容的TVS管。TVS管的非線性特性比壓敏電阻好。當(dāng)通過TVS管的過電流增大時,TVS管的鉗位電壓上升速度比壓敏電阻慢,因此可以獲得比壓敏電阻更理想的殘壓輸出。在很多需要精細保護的電子電路中,應(yīng)用TVS管是比較好的選擇。TVS管的通流容量在限壓型浪涌保護器中是最小的,一般用于最末級的精細保護,因其通流量小,一般不用于交流電源線路的保護,直流電源的防雷電路使用TVS管時,一般還需要與壓敏電阻等通流容量大的器件配合使用。

2020-08-25 17:03:38

,從外觀上來看,都是同小異,但是對于功能與配置方面來說,還有是很大的區(qū)別的,正是因為其配置不同,所以其功能上也很大的區(qū)別的。 首先我們來分析下配置,我們從光源的角度來分析下微型投影儀,可以分成兩大類

2012-11-05 18:37:29

說到顯示技術(shù),人們最先想到的就是液晶顯示(LED背光技術(shù)。但是很多人會將LCD與冷陰極熒光燈管混為一談,這顯然是不正確的,應(yīng)該從背光原理的角度來進行區(qū)分,這樣才是最為正確的理解方式。希望大家在看過本文之后能夠有所收獲。

2020-10-30 09:57:26

成本 少了電刷,無刷電機的磨損主要是在軸承上了,從機械角度看,無刷電機幾乎是一種免維護的電動機了,必要的時候,只需做一些除塵維護即可。無刷電機控制原理電機驅(qū)動控制就是控制電機的轉(zhuǎn)動或者停止,以及轉(zhuǎn)動

2019-09-26 07:00:00

/cpld的設(shè)計和優(yōu)化技巧。在討論fpga/cpld設(shè)計指導(dǎo)原則的基礎(chǔ)上,介紹了altera器件的高級應(yīng)用;引領(lǐng)讀者學(xué)習(xí)邏輯鎖定設(shè)計工具,詳細討論了時序約束與靜態(tài)時序分析方法;結(jié)合實例討論如何進行設(shè)計優(yōu)化

2020-05-14 14:50:30

Altera FPGA/CPLD設(shè)計與Verilog數(shù)字系統(tǒng)設(shè)計教程從網(wǎng)上找到了一些Altera FPGA/CPLD經(jīng)典教材,包含夏宇聞老師的Verilog數(shù)字系統(tǒng)設(shè)計教程(第2版)Altera FPGA/CPLD設(shè)計與Verilog數(shù)字系統(tǒng)設(shè)計教程

2014-02-17 09:22:18

電壓幅值為Vin,即圖1輸入直流的電壓值,低電壓為0。由于圖1中D1的存在,使得電流只能單向流動,因此在圖2中等效為串聯(lián)二極管D2。 2.Buck電路的常規(guī)角度分析 2.1時域分析方法 下面按著電容

2020-06-16 08:04:16

DSP、MCU、ARM、CPLD/FPGA對比分析哪個好?

2021-10-22 07:17:10

我是新手,現(xiàn)在設(shè)計板子,需要采集AD數(shù)據(jù),其中需要采集AD前級的放大倍數(shù),為16位數(shù)據(jù),請問各位用什么接口和CPLD/FPGA相連,可以較為方便的讀取數(shù)據(jù),AD為AD7764,打算用MCASP接口與OMAPL138相連接,這個MCASP與MCBSP有什么區(qū)別沒??

2020-04-21 10:06:00

積木的方式進行學(xué)習(xí)、開發(fā),時時積極的分享試用心得體會。項目描述:我將以《【mBot試用體驗】多角度DIY》為題,多角度多方向的展示我的試用體驗,分為如下幾個方面:1.第一帖【mBot試用體驗】多角度

2015-10-29 14:13:46

`內(nèi)容簡介· · · · · ·CPLD/FPGA是目前應(yīng)用最為廣泛的兩種可編程專用集成電路(ASIC),特別適合于產(chǎn)品的樣品開發(fā)與小批量生產(chǎn)。本書從現(xiàn)代電子系統(tǒng)設(shè)計的角度出發(fā),以全球著名

2018-03-29 17:11:59

電壓幅值為Vin,即圖1 輸入直流的電壓值,低電壓為0。由于圖1 中D1 的存在,使得電流只能單向流動,因此在圖2 中等效為串聯(lián)二極管D2。2. Buck 電路的常規(guī)角度分析2.1 時域分析方法下面按著

2019-07-16 04:30:00

`回收柯尼卡美能達CM-M6多角度分光測色計/色差分析儀/色差對比儀專業(yè)二手儀器儀表出售+回收: 示波器,萬用表,頻譜分析儀,網(wǎng)絡(luò)分析儀,照度計,輝度計,等

2020-02-26 11:20:45

大家下午好,我計劃使用主fpga板的IO引腳配置目標(biāo)cpld板,即菊花鏈。我使用主fpga板的IO引腳連接cpld的JTAG頭。如何編程master fpga的IO引腳來配置目標(biāo)cpld?請發(fā)送與此相關(guān)的任何文件....謝謝問候Vimala

2020-03-24 06:43:09

正在學(xué)習(xí)FPGA,有幾點疑惑,請版上的各位網(wǎng)友指教: 1. FPGA與CPLD究竟有哪些區(qū)別?我用verilog寫的程序,燒到CPLD和FPGA上都可以實現(xiàn)功能,那么實際應(yīng)用的時候,這兩者有什么區(qū)別

2013-07-22 10:01:08

本文討論的四種常用FPGA/CPLD設(shè)計思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD 邏輯設(shè)計的內(nèi)在規(guī)律的體現(xiàn),合理地采用這些設(shè)計思想能在FPGA/CPLD設(shè)計工作種取得事半功倍的效果。

2021-04-29 06:04:14

數(shù)字系統(tǒng)的設(shè)計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標(biāo)準(zhǔn)的功能元件粘合在一起來實現(xiàn)數(shù)字設(shè)計。除了這些數(shù)字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數(shù)字邏輯單元實現(xiàn)共模功能,從而構(gòu)建模數(shù)轉(zhuǎn)換器(ADC)。

2019-08-19 06:15:33

《Altera FPGA/CPLD設(shè)計(高級篇)》結(jié)合作者多年工作經(jīng)驗,深入地討論了Altera FPGA/CPLD的設(shè)計、優(yōu)化技巧。在討論FPGA/CPLD設(shè)計指導(dǎo)原則的基礎(chǔ)上,介紹了Altera器件的高級應(yīng)用;引領(lǐng)讀者

2009-02-12 09:19:12 4799

4799 altera fpga/cpld設(shè)計 基礎(chǔ)篇結(jié)合作者多年工作經(jīng)驗,系統(tǒng)地介紹了FPGA/CPLD的基本設(shè)計方法。在介紹FPGA/CPLD概念的基礎(chǔ)上,介紹了Altera主流FPGA/CPLD的結(jié)構(gòu)與特點,并通過豐富的實例講解

2009-07-10 17:35:45 57

57 本文就web 服務(wù)存在的安全性問題進行分析,總結(jié)了現(xiàn)有的XML 與Web 服務(wù)安全相關(guān)技術(shù)的發(fā)展。在此基礎(chǔ)上提出了一個從多角度構(gòu)筑的web 服務(wù)安全解決方案。目前,web 服務(wù)技術(shù)正

2009-08-13 09:50:05 11

11 UART 是廣泛使用的串行數(shù)據(jù)通訊電路。本設(shè)計包含UART 發(fā)送器、接收器和波特率發(fā)生器。設(shè)計應(yīng)用EDA 技術(shù),基于FPGA/CPLD 器件設(shè)計與實現(xiàn)UART。關(guān)鍵詞 :FPGA/CPLD;UART;VHDLUART(即U

2009-09-29 08:01:20 23

23 cpld fpga 區(qū)別

系統(tǒng)的比較,與大家共享:盡管FPGA和CPLD都是可編程ASIC器件,有很多共同特點,但由于CPLD和FPGA結(jié)構(gòu)上的差異,具

2008-01-15 09:58:56 5406

5406

多角度透視中國IC設(shè)計公司發(fā)展現(xiàn)狀及趨勢

今年進行了第8次年度中國IC設(shè)計公司調(diào)查,本次調(diào)查對象涵蓋中國大陸地區(qū)419家IC設(shè)計企業(yè),地域分布覆蓋珠三角、長

2009-12-09 10:34:03 654

654 常用FPGA/CPLD四種設(shè)計技巧

FPGA/CPLD的設(shè)計思想與技巧是一個非常大的話題,本文僅介紹一些常用的設(shè)計思想與技巧,包括乒乓球操作、串并轉(zhuǎn)換、流水線操作和數(shù)據(jù)接口

2010-05-12 11:10:43 766

766

本文討論的四種常用FPGA/CPLD設(shè)計思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD邏輯設(shè)計的內(nèi)在規(guī)律的

2010-11-04 10:11:28 625

625

FPGA和CPLD的區(qū)別,以及設(shè)計思路思想

2016-02-17 11:20:56 38

38 CPLD和FPGA的區(qū)別,好東西,喜歡的朋友可以下載來學(xué)習(xí)。

2016-02-19 16:59:55 0

0 基于FPGA/CPLD的UART功能設(shè)計

2017-01-23 20:45:37 30

30 CPLD和FPGA都是我們經(jīng)常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區(qū)分,把他們都叫做FPGA。那么兩者到底有什么區(qū)別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區(qū)別。

2017-09-18 16:35:32 5

5 近些年,越來越多的半導(dǎo)體巨頭、互聯(lián)網(wǎng)科技公司以及整車廠都在高調(diào)進軍汽車電子領(lǐng)域,每年在拉斯維加斯舉行的消費電子展CES,現(xiàn)在也越來越多的成為了各個廠商們展示其最新汽車電子技術(shù)的平臺,可見汽車電子行業(yè)迎來了風(fēng)口。 那么,到底何謂汽車電子?汽車電子行業(yè)都有哪些特點和機會?以及汽車電子的未來發(fā)展趨勢是怎樣的?筆者通過這篇文章,給大家普及下相關(guān)知識,希望大家能對汽車電子行業(yè)有個初步的認識。 汽車電子相關(guān)概念: 從廣

2017-09-24 10:23:22 5

5 1.CPLD:CPLD主要是由可編程邏輯宏單元(LMC,LogicMacroCell)圍繞中心的可編程互連矩陣單元組成,其中LMC邏輯結(jié)構(gòu)較復(fù)雜,并具有復(fù)雜的I/O單元互連結(jié)構(gòu),可由用戶根據(jù)需要生成

2017-09-26 16:38:12 89281

89281 FPGA/CPLD能完成任何數(shù)字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA/CPLD來實現(xiàn)。 FPGA/CPLD如同一張白紙或是一堆積木,工程師可以通過傳統(tǒng)的原理圖輸入法

2017-10-09 09:52:20 14

14 中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。FPGA和CPLD的區(qū)別和優(yōu)缺點分析。

2017-10-24 10:04:00 46702

46702 數(shù)字編程是數(shù)字電路非常重要的一門課程,FPGA和CPLD是兩個重要的編程工具,本文帶您認識fpga和cpld的聯(lián)系和區(qū)別。 FPGA(Field-Programmable Gate Array

2017-12-01 10:07:59 18391

18391 本文討論的四種常用FPGA/CPLD設(shè)計思想與技巧:乒乓操作、串并轉(zhuǎn)換、流水線操作、數(shù)據(jù)接口同步化,都是FPGA/CPLD邏輯設(shè)計的內(nèi)在規(guī)律的體現(xiàn),合理地采用這些設(shè)計思想能在FPGA/CPLD設(shè)計工

2017-12-02 11:30:04 7152

7152

從概念提出、原型探索、技術(shù)積累到產(chǎn)品迭代和產(chǎn)業(yè)化發(fā)展,VR逐漸從軍用市場拓展到消費級市場,逐步向更多行業(yè)領(lǐng)域滲透。本文基于相關(guān)數(shù)據(jù),從歷程、特點、熱點、趨勢等多角度深度分析VR發(fā)展。

2018-02-08 11:15:50 3818

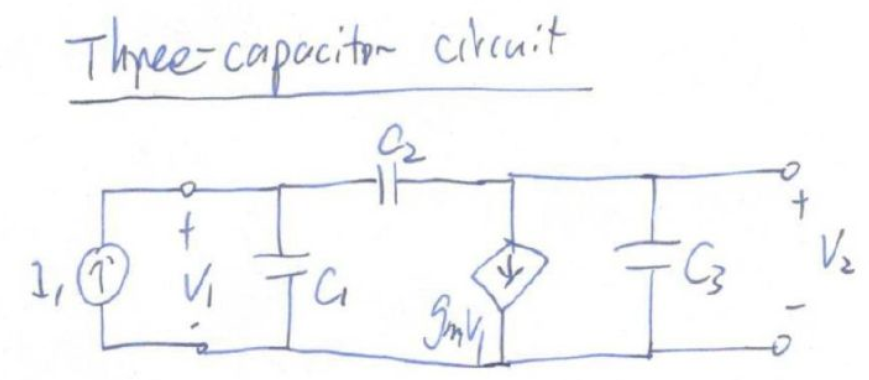

3818 三電容電路是基本π網(wǎng)絡(luò)的一種,多角度理解三電容電路是模擬電路設(shè)計入門的關(guān)鍵,本文將詳細解說三電容電路圖和三電容電路時域分析。

2018-02-21 10:51:00 10787

10787

FPGA LAB和CPLD的LAB設(shè)計不同。CPLD LAB由宏單元構(gòu)成,包括自己的本地可編程陣列,而FPGA LAB由大量的邏輯模塊構(gòu)成,這些模塊被稱為邏輯單元,即LE,而且本地互連和邏輯分開。LE看起來可能和CPLD宏單元相似,但更容易配置,有更豐富的特性來提高性能,減少邏輯資源的浪費。

2018-04-17 17:02:00 1979

1979

ARM,DSP,FPGA,CPLD,SOPC,SOC之間有什么區(qū)別和聯(lián)系 arm是一種嵌入式芯片,比單片機功能強,可以針對需要增加外設(shè)。類似于通用cpu,但是不包括桌面計算機。 DSP主要用來計算

2018-04-18 07:19:00 4350

4350 CPLD和FPGA都是我們經(jīng)常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區(qū)分,把他們都叫做FPGA。那么兩者到底有什么區(qū)別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區(qū)別。

2018-05-24 02:03:00 49472

49472

唐雄燕指出,5G三大業(yè)務(wù)特征分別是增強移動寬帶、海量物聯(lián)、超低時延。其市場價值主要在于,提供超高清視頻,人類交互方式再次升級;使能車聯(lián)網(wǎng)、智能制造、智慧醫(yī)療、智慧教育、智慧城市等垂直行業(yè);構(gòu)建物理世界對應(yīng)的數(shù)字世界,推動各行各業(yè)的數(shù)字化轉(zhuǎn)型。中國聯(lián)通從多角度入手,推動5G發(fā)展,共筑5G商業(yè)之路。

2018-11-29 09:26:52 752

752 本文檔詳細介紹的是FPGA教程之CPLD與FPGA的基礎(chǔ)知識說明主要內(nèi)容包括了:一、復(fù)雜可編程邏輯器件簡介二、CPLD的組成與特點三、FPGA的組成與特點四、CPLD與FPGA的異同五、主要的PLD廠商

2019-02-27 17:09:32 32

32 CPLD主要是由可編程邏輯宏單元(LMC,Logic Macro Cell)圍繞中心的可編程互連矩陣單元組成,其中LMC邏輯結(jié)構(gòu)較復(fù)雜,并具有復(fù)雜的I/O單元互連結(jié)構(gòu),可由用戶根據(jù)需要生成特定的電路

2019-04-03 11:08:47 12254

12254 據(jù)消息報道,2020版新iPhone11將在攝像頭方面全 main 升級,如拍攝更好的暗光照片、多角度Face ID面部識別、新的iPad、更便宜的家庭影院等新驚喜。報道稱,新一代iPhone將于9月10日發(fā)布會上亮相。

2019-08-27 14:11:27 11360

11360 CPLD和FPGA都是我們經(jīng)常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區(qū)分,把他們都叫做FPGA。

2019-09-13 14:58:00 5135

5135 FPGA與 CPLD的辨別和分類主要是根據(jù)其結(jié)構(gòu)特點和工作原理。通常的分類方法是:將以乘積項結(jié)構(gòu)方式構(gòu)成邏輯行為的器件稱為CPLD。

2020-03-24 10:15:40 5341

5341 本文主要介紹CPLD和FPGA的基本結(jié)構(gòu)。 CPLD是復(fù)雜可編程邏輯器件(Complex Programable Logic Device)的簡稱,FPGA是現(xiàn)場可編程門陣列(Field

2020-09-25 14:56:33 12233

12233

什么牌子的好用呢?今天我拿來了五款目前最主流的藍牙耳機,來多角度對比,大家一起來看看吧。 1.JEET ONE真無線藍牙耳機 近幾年來,一說到藍牙耳機最火的就是JEET這個品牌了,到處都能看到它身影,新推出的這款JEET ONE不僅擁有

2020-11-13 10:45:54 2671

2671 南卡新品runner pro骨傳導(dǎo)耳機與韶音as800多角度測評大對比 骨傳導(dǎo)耳機一直以來都是定位為運動耳機,頭戴式耳機運動時悶熱,且隔音效果好,有線耳機束縛容易脫落,入耳式耳機也是一樣容易脫落丟失

2021-02-07 10:27:23 1101

1101 多角度偏振成像儀探測器非均勻性體現(xiàn)在高頻和低頻兩個方面,高頻差異體現(xiàn)在相鄰像素點間的快速變化,低頻差異體現(xiàn)在不同視場區(qū)域的整體緩慢變化。研究團隊利用探測器綜合測試系統(tǒng),分析了影響非均勻校正的暗電流

2021-02-20 14:23:20 1535

1535

CPLD/FPGA的基本知識講解。

2021-03-30 09:55:18 27

27 美能達高精度多角度光澤度計MG268A,在每次測量時記錄樣品的溫度數(shù)據(jù),以便分析熱色效應(yīng)。其還有一項實用功能,即通過紅外線將數(shù)據(jù)傳輸至外部計算機。

2021-07-01 14:22:40 491

491 Altera FPGA CPLD學(xué)習(xí)筆記(肇慶理士電源技術(shù)有限)-Altera FPGA CPLD學(xué)習(xí)筆記? ? ? ? ? ? ? ? ?

2021-09-18 10:54:41 79

79 FPGA CPLD數(shù)字電路設(shè)計經(jīng)驗分享.(電源技術(shù)發(fā)展怎么樣)-FPGA CPLD數(shù)字電路設(shè)計經(jīng)驗分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 51

51 FPGA CPLD中的Verilog設(shè)計小技巧(肇慶理士電源技術(shù)有限)-FPGA CPLD中的Verilog設(shè)計小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 35

35 日前,東芝能源系統(tǒng)株式會社(以下稱東芝)宣布,其交付給日本山形大學(xué)(以下簡稱山形大學(xué))的重離子治療注1裝置的旋轉(zhuǎn)機架注2治療室已開始用于需要多角度照射的頭頸部腫瘤治療。

2022-05-20 16:35:39 2027

2027 能夠多角度探測目標(biāo)。傳統(tǒng)雷達只能獲取目標(biāo)的后向雷達散射特性。而使用雙基構(gòu)型,可以從前向、側(cè)向、后向多角度對目標(biāo)進行探測。尤其是對隱身目標(biāo)的探測能力,大大強于傳統(tǒng)雷達。

2022-11-24 20:06:27 943

943 都是FPGA/CPLD邏輯設(shè)計的內(nèi)在規(guī)律的體現(xiàn),合理地采用這些設(shè)計思想能在FPGA/CPLD設(shè)計工作種取得事半功倍的效果。

2023-05-18 08:56:57 350

350

CPLD和FPGA都是由邏輯陣列模塊構(gòu)成的,但是CPLD的LAB基于乘積和宏單元,而FPGA的LAB使用基于LUT的邏輯單元。

2023-06-28 11:28:04 862

862

可編程邏輯包括 PAL、GAL、PLD 等。通過不斷發(fā)展,它已經(jīng)發(fā)展成為現(xiàn)在的CPLD/FPGA。CPLD(復(fù)雜可編程邏輯器件)和FPGA(現(xiàn)場可編程門陣列)的功能基本相同,只是實現(xiàn)原理略有不同

2023-07-03 14:33:38 6041

6041

從多角度看,TVS、壓敏、放電管哪個效果更好? TVS、壓敏、放電管是常用的過電壓保護元件,它們在電子設(shè)備中起到防止電壓過高而對電路元件造成損壞的作用。從多個角度來看,這三種保護元件的效果

2024-01-03 11:31:30 230

230 CPLD和FPGA都是由邏輯陣列模塊構(gòu)成的,但是CPLD的LAB基于乘積和宏單元,而FPGA的LAB使用基于LUT的邏輯單元。CPLD的LAB圍繞中心全局互連排列,隨著器件中邏輯數(shù)量的增加,呈指數(shù)

2024-01-23 09:17:04 280

280 FPGA(現(xiàn)場可編程門陣列)和CPLD(復(fù)雜可編程邏輯器件)都是可編程邏輯器件,但它們在多個方面存在顯著的區(qū)別。

2024-03-15 14:56:58 93

93

電子發(fā)燒友App

電子發(fā)燒友App

評論