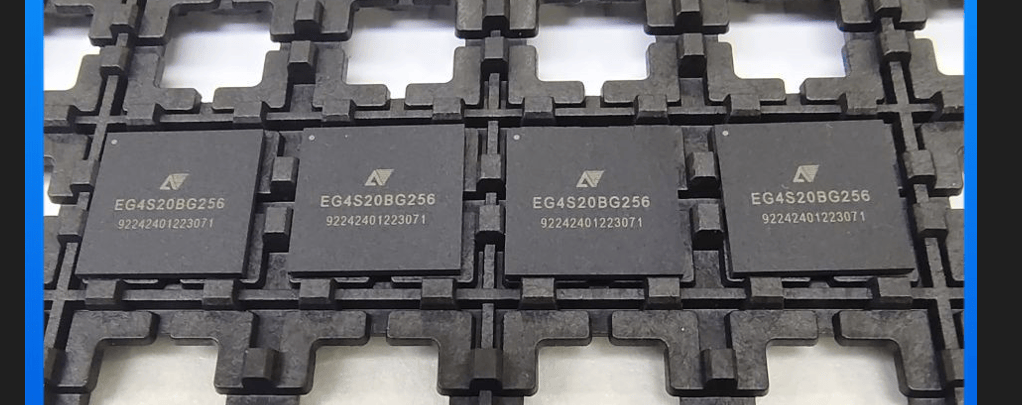

安路FPGA極簡開發板是專門針對數字電路課程開發的,核心板不追求大而全,但已經覆蓋數電課程的基礎需求、簡單易用并擁有較強的擴展性,結合學校一線教學經驗和國產化趨勢,我們將開發板的核心芯片型號選定為安路科技的EG4S20BG256,它資源豐富且管腳多;在外圍功能模塊的設計上,則以簡潔直觀、小巧易攜帶為目標,主要包括以下幾類模塊:板載USB-JTAG電路,實現一根線供電和調試;輸出顯示類,如LED燈、數碼管;輸入操作類的,如矩陣按鍵、撥動開關;發聲及音頻類的,如蜂鳴器;對外通信接口類的,如UART轉USB接口;存儲器類的,如FLASH存儲器、SDRAM存儲器;模數混合類的,如ADC和DAC

安路科技的 EG4S20 FPGA,是基于安路成熟可靠的低成本、低功耗可編程FPGA—EG4X20,采用最新的 3D 合封技術,與一塊 2M X 32bits 的 SDRAM 合封而成。EG4S20 既有尺寸更小,更簡單可靠的QFN封裝,又有用戶可用 IO 更多的 BGA 封裝。更大的內嵌存儲容量,特別適用于大容量,高速數據的采集、傳輸和變換等應用。特色優勢? 多品種,大容量的內置存儲空間? 內置 64Mb SDRAM 存儲空間,32 位數據總線寬度,最高 200Mhz 工作頻率,最大讀寫帶寬高達 800MB/s? 內置 64 塊 ERAM9K 隨機讀寫 RAM,可配置為真雙口,簡單雙口,單口RAM 和FIFO 工作模式,位寬可配置為 512x18, 1Kx9, 2Kx4, 4Kx2, 8Kx1, 最高頻率220Mhz? 內置 16 塊 32Kb RAM,可配置為單口 RAM,雙口 RAM,可獨立配置為2Kx16 或者4Kx8? 更小封裝,更多 IO, 更利于 PCB 布線的引腳排布? 支持 True LVDS,最高頻率 800Mbps? BGA256 封裝為 1.0mm 引腳間距,封裝尺寸 17mm X 17mm? QFN88 封裝為 0.4mm 引腳間距,10mm X 10mm? CSG324 封裝為 0.8mm 引腳間距,封裝尺寸 15mm X 15mm? 優化的引腳排布,只需要兩層 PCB 即可輕松使用器件所有 IO? 支持簡單低成本的 SPI FLASH 配置;上電配置后,FLASH 可開放給用戶使用。? 集成多種專用 IP? 集成電源監控模塊,可對指定 BANK 電壓監控? 集成內部環型振蕩器SALEAGLE?4S20 FPGA 數據手冊DS301_2.7.2 www.anlogic.com 32022.3 Confidential2 EG4S20 架構介紹同 EG4X20,詳情請參考 EG4 系列 FPGA 數據手冊3 EG4S20 交直流特性同 EG4X20,詳情請參考 EG4 系列 FPGA 數據手冊4 EG4S20 內部 SDRAMEG4S20 內嵌一片 2M x 32bit 的 SDRAM(EM638325),最高 200Mhz 工作頻率,最大讀寫帶寬高達800MB/s。SDRAM 與 FPGA 通過軟件深度整合,所以如果要使用 SDRAM,只需要在IP generate 中例化,或者在頂層實例化如下 IP 模塊即可。該 IP 的原型如下:EG_PHY_SDRAM_2M_32 U_EG_PHY_SDRAM_2M_32(.clk(SD_CLK), // SDRAM 時鐘 1bit 位寬.ras_n(SD_RAS_N), // SDRAM 行選通 1bit 位寬.cas_n(SD_CAN_N), //SDRAM 列選通 1bit 位寬.we_n(SD_WE_N), //SDRAM 寫使能 1bit 位寬.addr(SD_SA), //SDRAM 地址 11bits 位寬.ba(SD_BA), // SDRAM BANK 地址 2bits 位寬.dq(SD_DQ), //SDRAM 數據 32bits 位寬.cke(SD_CKE), // SDRAM 時鐘使能1bit 位寬.dm(4'b0) //SDRAM 數據屏蔽 4bit 位寬

靈活的邏輯結構

?19600 個 LUTs,用戶 IO 數量 193 個

低功耗器件

?先進的 55nm 低功耗工藝

?靜態功耗低至 5mA

支持分布式和嵌入式存儲器

?156 Kbits 分布存儲器(Distribute RAM)

?1 Mbits 嵌入塊存儲器(Block RAM 簡稱 BRAM)包括:

- 64 個 9 Kbits BRAM,可配置為真雙口,8Kx1 到 512x18 模式

- 16 個 32 Kbits BRAM,可配置為真雙口,可設置為 2K*16 或 4K*8

- 專用 FIFO 控制邏輯

內置大容量存儲器

?內置 2M*32bits SDR SDRAM,最高工作時鐘 200MHz

可配置邏輯模塊 (PLBs)

?優化的的 LUT4/LUT5 組合設計

?雙端口分布式存儲器

?支持算數邏輯運算

?快速進位鏈邏輯

源同步輸入 / 輸出接口

?輸入 // 輸出單元包含 DDR 寄存器

· Generic DDRx1

· Generic DDRx2

高性能,靈活的輸入 / 輸出緩沖器

?支持 LVTTL、LVCMOS (3.3/2.5/1.8V/1.5/1.2V)、PCI

?支持 LVDS,Bus-LVDS, MLVDS, RSDS, LVPECL

?支持熱插拔

?可配置上拉 / 下拉模式

?片內 100 歐姆差分電阻

時鐘資源

?針對高速 I/O 接口設計的 2 路 IOCLK

?16 路全局時鐘

?支持 4 個 PLLs 用于頻率綜合

?5 路時鐘輸出

?分頻系數 1 到 128

?支持 5 路時鐘輸出級聯

?動態相位選擇

配置模式

?主模式串行 SPI (MSPI)

?從模式串行 (SS)

?主模式并行 x8 (MP)

?從模式并行 x8 (SP)

?JTAG 模式 (IEEE-1532)

每個芯片擁有的 64 位 DNA

嵌入式硬核 IP

?8 通道 12 位 1MSPS SAR ADC

?集成電壓監控模塊

?內置環形振蕩器