當(dāng)然,(近乎)完美的電氣開(kāi)關(guān)已經(jīng)存在很長(zhǎng)時(shí)間了,但我們?cè)谶@里不是在談?wù)摍C(jī)械。現(xiàn)代電源轉(zhuǎn)換依賴(lài)于理想情況下沒(méi)有電阻的半導(dǎo)體開(kāi)關(guān),當(dāng)打開(kāi)時(shí)沒(méi)有電阻,關(guān)閉時(shí)具有無(wú)限電阻和耐壓,并且能夠通過(guò)簡(jiǎn)單的驅(qū)動(dòng)在兩種狀態(tài)之間切換,任意快速,并且沒(méi)有瞬時(shí)功耗。

在我們注重能源和成本的世界中,這些功能有助于在電源、逆變器、電池充電器、電機(jī)驅(qū)動(dòng)器等領(lǐng)域?qū)崿F(xiàn)高功率轉(zhuǎn)換效率。隨之而來(lái)的好處是減少了設(shè)備尺寸、重量和故障率,同時(shí)降低了采購(gòu)成本和生命周期成本。有時(shí),會(huì)超出一個(gè)簡(jiǎn)單的效率閾值,從而打開(kāi)整個(gè)應(yīng)用領(lǐng)域。例如,如果電機(jī)驅(qū)動(dòng)器損耗過(guò)大并因此又大又重,則電動(dòng)汽車(chē)幾乎不可行,而這又需要更多的電池功率,同時(shí)又會(huì)導(dǎo)致重量和續(xù)航里程的進(jìn)一步損失。從近 75 年前的 Shockley、Bardeen 和 Brattain 時(shí)代開(kāi)始,工程師們因此一直致力于改進(jìn)半導(dǎo)體開(kāi)關(guān),以更接近理想狀態(tài)。

邁向理想開(kāi)關(guān)

機(jī)械開(kāi)關(guān)確實(shí)用于第一個(gè)電源轉(zhuǎn)換應(yīng)用——機(jī)械“振動(dòng)器”最初是用于隔離 DC/DC 轉(zhuǎn)換或 DC 電壓升壓的電動(dòng)發(fā)電機(jī)組的唯一替代品。然而,在晶體管發(fā)明大約 10 年后,出現(xiàn)了第一個(gè)開(kāi)關(guān)模式電源 (SMPS) 設(shè)計(jì),從那時(shí)起,設(shè)計(jì)人員不得不使用可用的半導(dǎo)體技術(shù)。盡管場(chǎng)效應(yīng)晶體管 (FET) 的原理已于 1930 年由 Julius Edgar Lilienfeld 提出并獲得專(zhuān)利1,但它們實(shí)際上無(wú)法制造,而且最初使用鍺的雙極晶體管主導(dǎo)了早期的 SMPS 電路。?

雙極晶體管起初具有有限的額定電壓、高關(guān)斷狀態(tài)泄漏以及緩慢且有損的開(kāi)關(guān),并且它們需要復(fù)雜的基極驅(qū)動(dòng)。時(shí)至今日,雙極晶體管的增益很低,可能需要數(shù)安培的基極電流。基極中存儲(chǔ)的電荷是一個(gè)大問(wèn)題,限制了關(guān)斷時(shí)間和效率,因此使用技術(shù)來(lái)精確定制基極驅(qū)動(dòng)并使用 Baker 鉗位等技術(shù)來(lái)限制電荷,該技術(shù)以一些傳導(dǎo)損耗換取較低的動(dòng)態(tài)損耗。

硅金屬氧化物柵極 FET (MOSFET) 在 70 年代和 80 年代具有垂直傳導(dǎo)路徑和平面柵極結(jié)構(gòu),隨后在 90 年代采用“溝槽”布置,因此在高功率方面變得可行。然而,在更高功率下的使用受到電壓額定值和可實(shí)現(xiàn)的導(dǎo)通電阻的限制。一個(gè)主要的發(fā)展是 70 年代后期的絕緣柵雙極晶體管 (IGBT),它結(jié)合了類(lèi)似 MOSFET 的柵極驅(qū)動(dòng)和類(lèi)似雙極的傳導(dǎo)路徑,具有易于驅(qū)動(dòng)和固定飽和電壓的優(yōu)點(diǎn),因此功耗名義上與電流成正比,而不是與 MOSFET 中的電流平方成正比。然而,IGBT 并非沒(méi)有自己的問(wèn)題,有閉鎖的趨勢(shì),會(huì)帶來(lái)災(zāi)難性的后果。關(guān)斷時(shí)的“尾電流”也使動(dòng)態(tài)損耗相對(duì)較高,從而限制了工作頻率。現(xiàn)代 IGBT 中的閂鎖問(wèn)題現(xiàn)已解決,尾電流最小化,而電流和電壓額定值已顯著增加,這使得這些部件在非常高的功率轉(zhuǎn)換中很常見(jiàn)。但是,由于動(dòng)態(tài)損耗,開(kāi)關(guān)頻率仍被限制在最大幾十千赫茲。

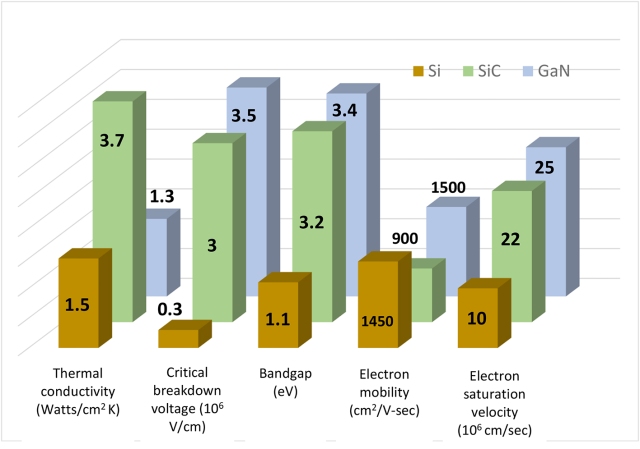

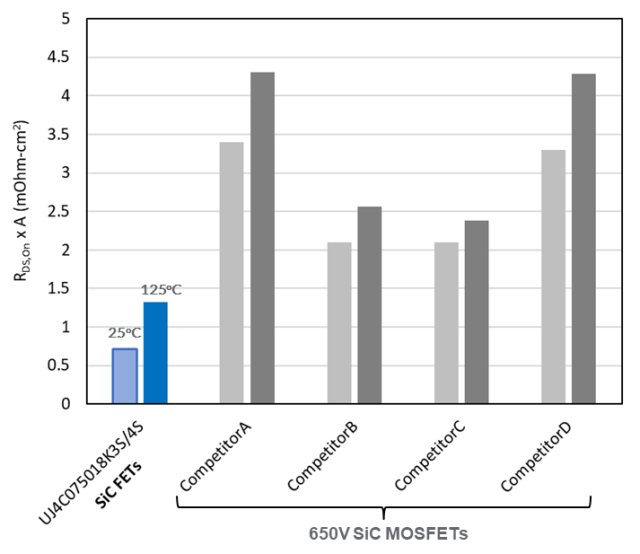

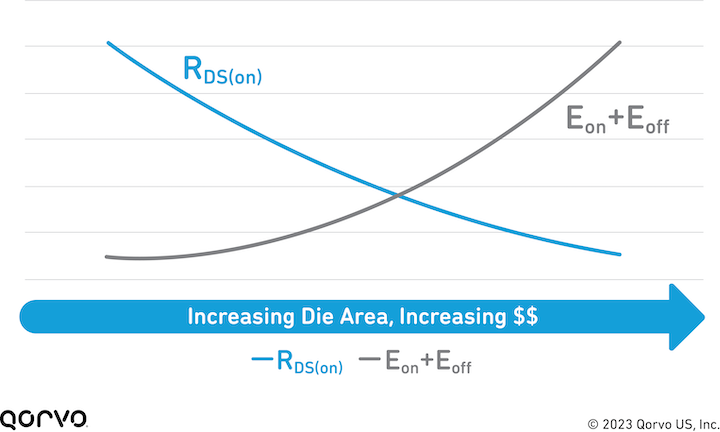

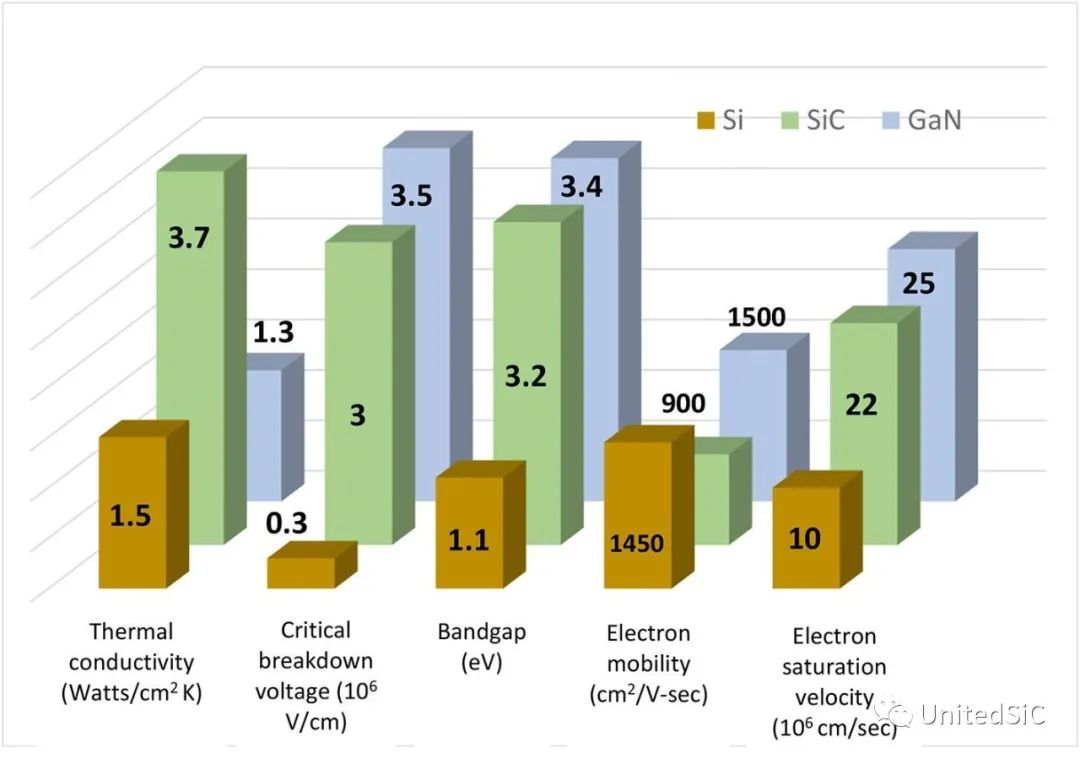

高開(kāi)關(guān)頻率是更小的磁性元件和具有更高性能控制回路的整體更小、更輕的功率轉(zhuǎn)換產(chǎn)品的關(guān)鍵,因此隨著 MOSFET 導(dǎo)通電阻和額定電壓的提高,它們被越來(lái)越多地使用,頻率被推高到數(shù)百千赫茲,“超級(jí)結(jié)”類(lèi)型是最先進(jìn)的。然而,一個(gè)限制因素是硅的擊穿電壓,對(duì)于給定的工作電壓和因此高的導(dǎo)通電阻 (R DS )值迫使體材料的最小厚度。許多單元可以并聯(lián)以減少這種情況,但總芯片面積 (A) 會(huì)增加。該效應(yīng)通過(guò)每單位面積的導(dǎo)通電阻 (R DSA) 品質(zhì)因數(shù),并促使人們對(duì)碳化硅和氮化鎵等寬帶隙材料的興趣激增。與硅相比,WBG 材料具有更高的本征擊穿電壓和其他有利特性,例如更高的電子遷移率和飽和速度、耐高溫能力以及對(duì)于 SiC 而言更好的導(dǎo)熱性。圖 1顯示了硅、SiC 和 GaN 材料主要特性的比較。

圖 1:Si、SiC 和 GaN 材料特性

圖 1:Si、SiC 和 GaN 材料特性早期 SiC 器件開(kāi)發(fā)

SiC器件的開(kāi)發(fā)比GaN 早 10 年,預(yù)期最初更廣泛地適用于更高的電壓和額定功率。SiC 開(kāi)關(guān)的一個(gè)自然起點(diǎn)是考慮開(kāi)發(fā)增強(qiáng)型、常關(guān)型 MOSFET,以便與現(xiàn)有的 Si MOSFET 設(shè)計(jì)和制造技術(shù)兼容。與任何新技術(shù)一樣,也存在初期問(wèn)題——有些是可以預(yù)測(cè)的,有些則不是,這導(dǎo)致了零件商業(yè)化的延遲。?

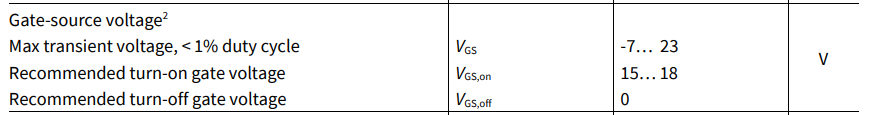

與硅相比,碳化硅的一個(gè)固有特性過(guò)去是,現(xiàn)在仍然是,晶格缺陷的數(shù)量更多。這些缺陷導(dǎo)致柵極氧化層與 SiC 溝道的界面處電子遷移率低,導(dǎo)致導(dǎo)通電阻相對(duì)較高。為了成本效益,碳化硅晶圓尺寸必須最大化,并且很難在 6 英寸行業(yè)標(biāo)準(zhǔn)下保持低缺陷率和晶圓平整度。SiC MOSFET 還表現(xiàn)出具有顯著滯后的柵極閾值不穩(wěn)定性,使得柵極驅(qū)動(dòng)難以設(shè)計(jì)以實(shí)現(xiàn)最佳效率和可靠性。盡管最新的 SiC MOSFET 更好,理論上可以使用單極 0 至 15V 驅(qū)動(dòng),但實(shí)際上,–5V 的負(fù)柵極電壓通常用于可靠運(yùn)行。此外,15 V 不會(huì)提供最低的導(dǎo)通電阻,

2010 年左右,碳化硅 MOSFET 遇到了一個(gè)無(wú)法預(yù)料的困難,即“基面位錯(cuò)”——晶格中的體缺陷——實(shí)際上在工作應(yīng)力期間生長(zhǎng)和遷移。隨著體二極管從源極到漏極的導(dǎo)電,產(chǎn)生電子空穴載流子,當(dāng)它們復(fù)合時(shí),有足夠的能量移動(dòng)并擴(kuò)大缺陷。這是 SiC 更高帶隙能量值的結(jié)果,其結(jié)果可能是性能下降——更高的漏電流和導(dǎo)通電阻——進(jìn)而導(dǎo)致更高的損耗和故障。隨著制造方法的進(jìn)步和缺陷篩選,如今的 SiC MOSFET 有了很大的改進(jìn),但仍在努力提高芯片的產(chǎn)量和成本效益以及封裝的性能,以實(shí)現(xiàn)低電感和熱阻。

SiC FET:另一種方法

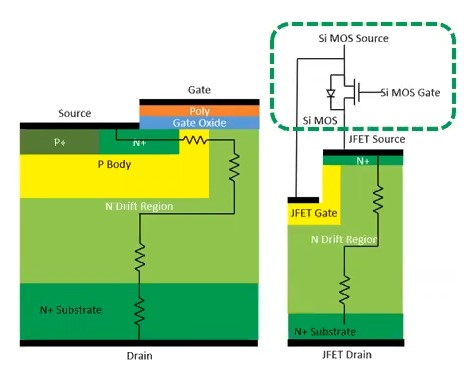

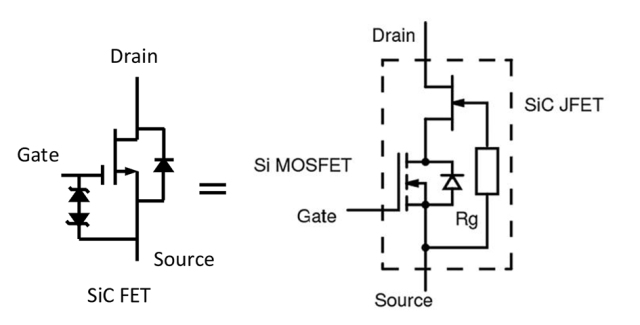

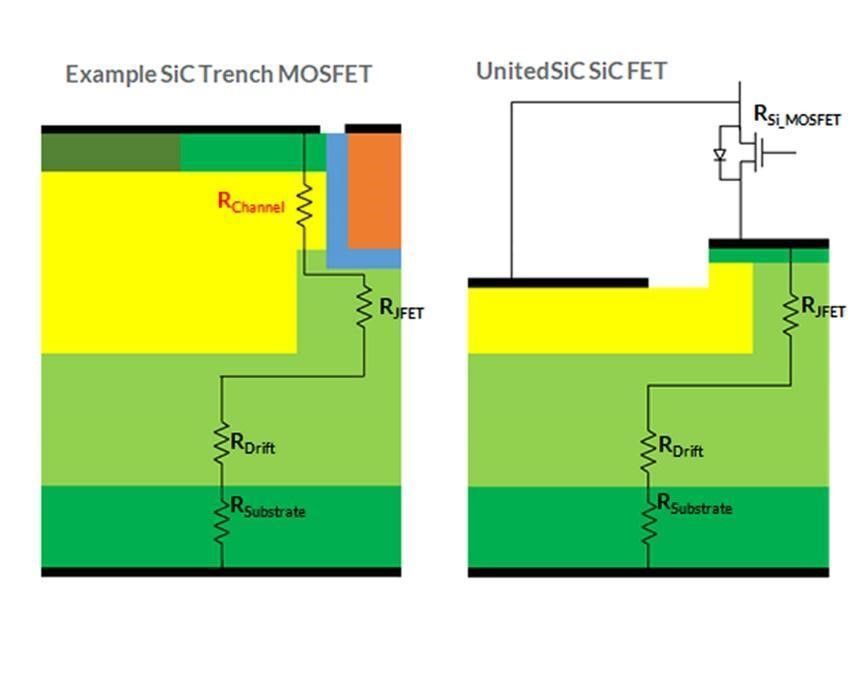

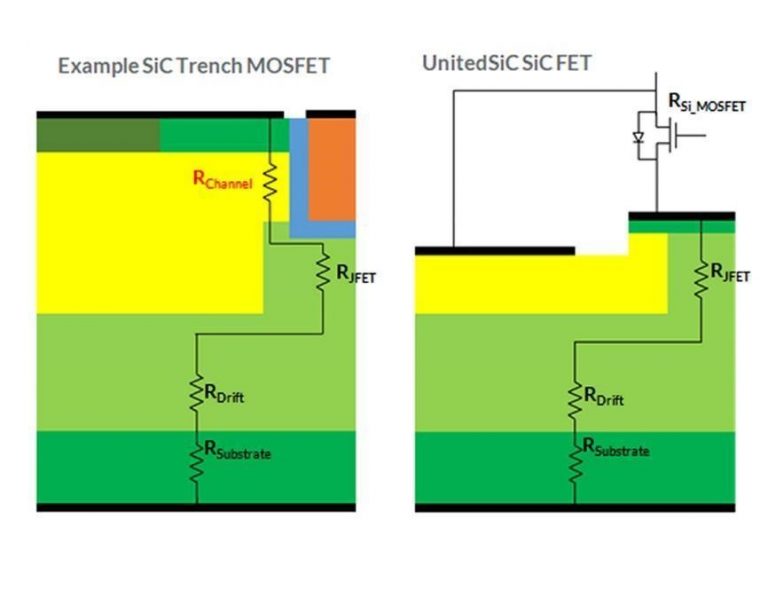

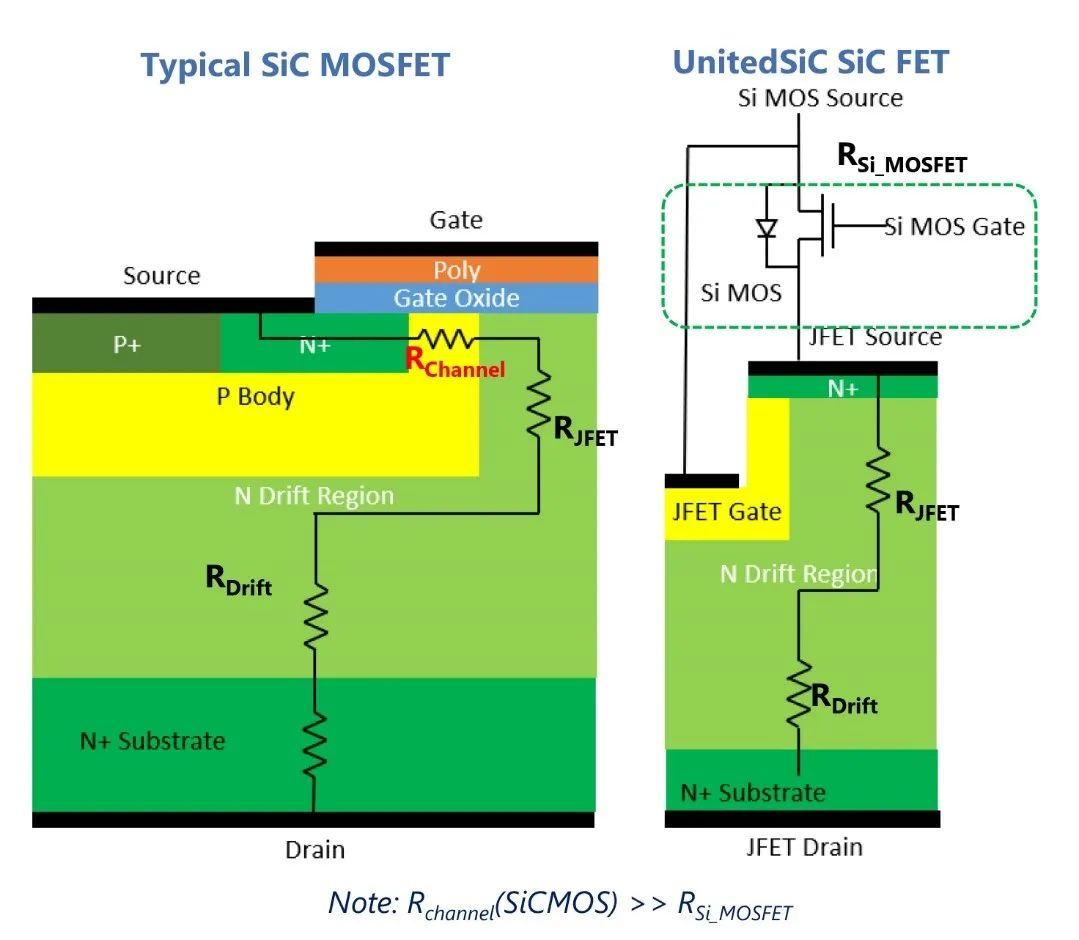

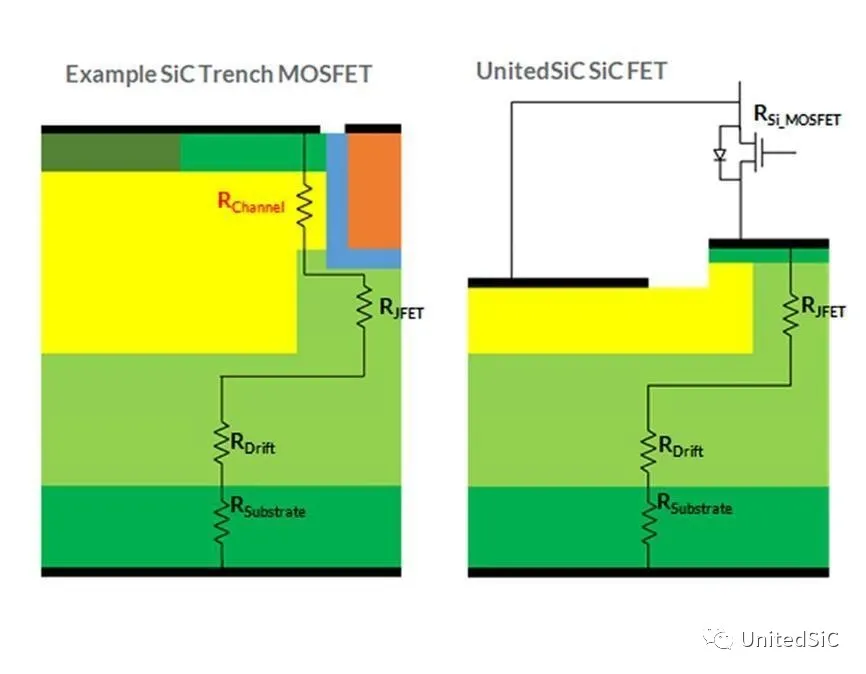

With the arrival of wide-bandgap technology, while many semiconductor manufacturers took the route of development of SiC MOSFETs using existing fabrication lines, others started with a blank sheet and considered other options. The simplest switch implemented with SiC is the JFET structure, which has no gate oxide and is a unipolar conduction device, so it does not show some of the limitations of MOSFETs. The device has a major drawback, though: It is normally on with gate drive at 0 V and requires a negative drive to turn off. At best, this is inconvenient; at worst, it risks application failure, especially under transient conditions such as system turn-on/turn-off. A device was proposed in the ’90s and developed around 2010 that solved the problem: the SiC FET, a combination of a SiC JFET and a silicon MOSFET that is normally off but maintains the advantages of a JFET over a MOSFET. 圖 2顯示了 SiC FET 布置(右)與通用 SiC MOSFET 原理圖(左)的比較。

圖 2:SiC MOSFET(左)和 SiC FET 結(jié)構(gòu)(右)

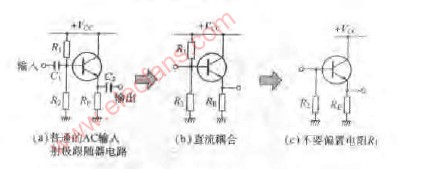

圖 2:SiC MOSFET(左)和 SiC FET 結(jié)構(gòu)(右)SiC FET 的排列是共源共柵,可能對(duì)更成熟的工程師來(lái)說(shuō)熟悉,他們甚至可能看到它以原始形式實(shí)現(xiàn)為真空管的組合,旨在降低音頻放大器中的噪聲。多年來(lái),共源共柵或“發(fā)射極開(kāi)關(guān)”以不同的形式出現(xiàn),包括雙極晶體管或 BJT 和 MOSFET 的組合;一般屬性是低壓開(kāi)關(guān)控制高壓開(kāi)關(guān),在高額定電壓和易于驅(qū)動(dòng)之間取得了很好的折衷。然而,由于需要大量的基極驅(qū)動(dòng)電流和緩慢的開(kāi)關(guān)速度,帶有 BJT 的電路在高功率下并不流行。SiC 共源共柵或 SiC FET 解決了這些問(wèn)題。?

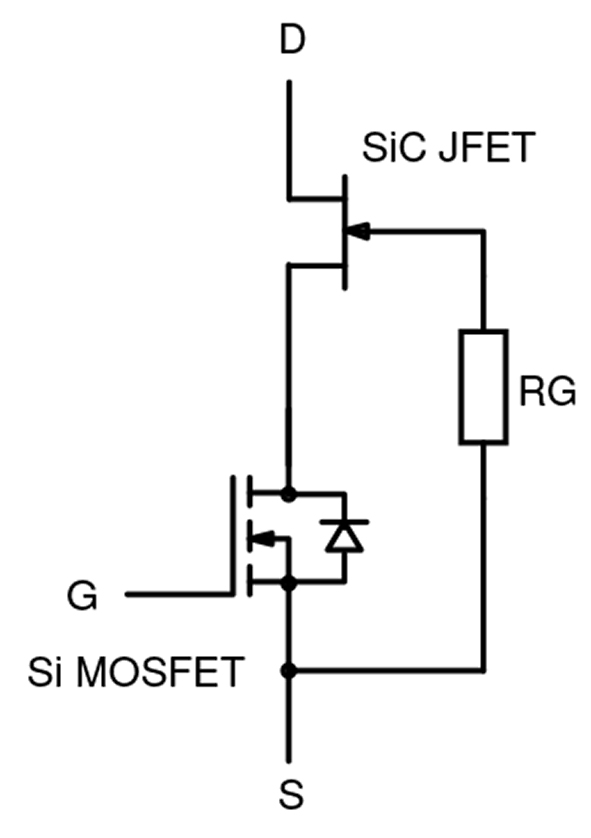

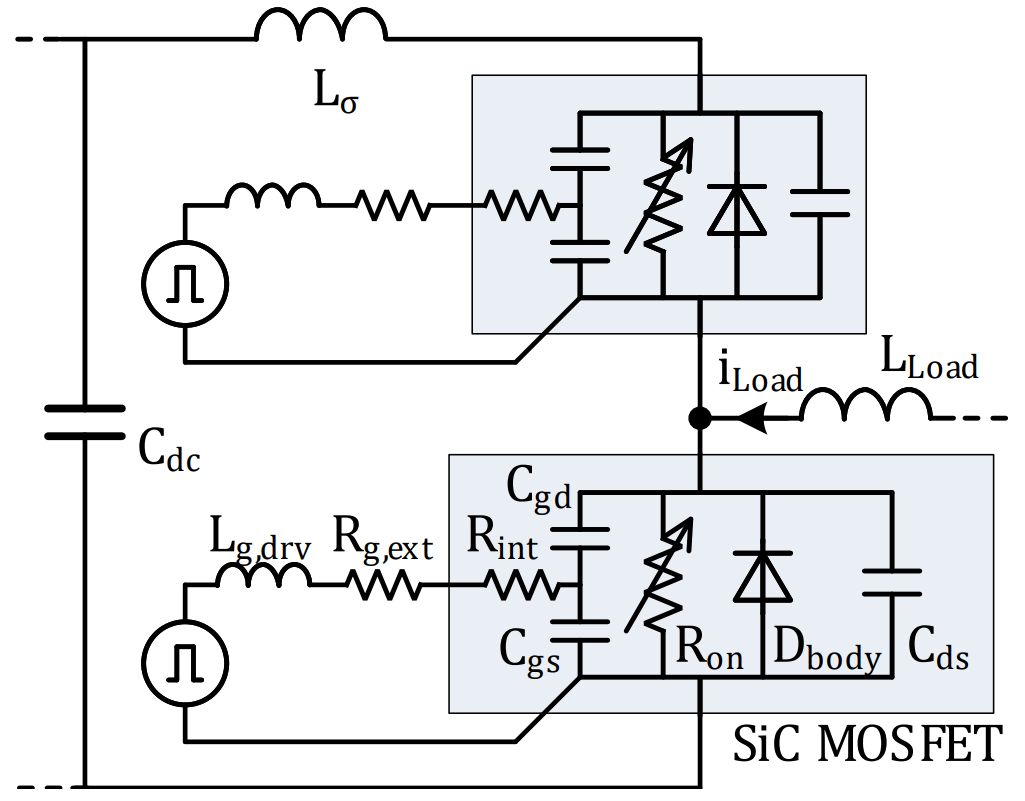

參考圖 3所示的 SiC FET 原理圖,當(dāng) Si MOSFET 通過(guò)其柵極導(dǎo)通時(shí),JFET 源極和柵極有效短路且 JFET 導(dǎo)通。電流現(xiàn)在可以通過(guò) JFET 和 MOSFET 漏源通道,傳導(dǎo)損耗由 JFET 固定,因?yàn)榕c高壓 SiC JFET 相比,低壓 Si MOSFET 導(dǎo)通電阻可以非常低。當(dāng) Si MOSFET 關(guān)閉時(shí),JFET 源極電壓上升到超過(guò)其負(fù)幾伏的柵源閾值并且 JFET 關(guān)閉的點(diǎn)。由于器件電容的比率,Si MOSFET 兩端的電壓動(dòng)態(tài)保持較低。

圖 3:SiC FET 原理圖

圖 3:SiC FET 原理圖SiC FET 與 SiC MOSFET 相比,無(wú)論是在電氣性能還是在實(shí)際使用中,都具有許多優(yōu)勢(shì)。作為開(kāi)關(guān),導(dǎo)通電阻是一個(gè)主要因素,與 SiC MOSFET 相比,SiC JFET 固有地在通道中具有更好的電子遷移率。通道密度也更高,這種組合意味著對(duì)于給定的裸片面積,SiC FET 導(dǎo)通電阻低 2 到 4 倍,或者相反,每個(gè)晶圓可以獲得高達(dá) 4 倍的裸片數(shù)量。 SiC MOSFET 具有相同的導(dǎo)通電阻。與硅超級(jí)結(jié) MOSFET 相比,增加的裸片數(shù)量可高達(dá) 13 倍。考慮到 SiC 作為一種材料可能總是比硅更昂貴,因此每片晶圓上總管芯的增加對(duì)于 SiC FET 技術(shù)的成功至關(guān)重要。如前所述,衡量芯片生存能力的指標(biāo)是品質(zhì)因數(shù) R動(dòng)態(tài)搜索廣告。?

另一個(gè)品質(zhì)因數(shù)是R DS × E oss,即導(dǎo)通電阻和器件輸出開(kāi)關(guān)能量之間的權(quán)衡,源自輸出電容。這是一種有用的措施,因?yàn)榭梢酝ㄟ^(guò)簡(jiǎn)單地在芯片中并聯(lián)更多單元來(lái)減少導(dǎo)通電阻和傳導(dǎo)損耗;但是,除了增加面積外,這還會(huì)直接增加電容,從而增加 E oss,從而導(dǎo)致與頻率相關(guān)的開(kāi)關(guān)損耗增加。因此,R DS × E oss 的低值是有利的。?

SiC FET 的柵極只是級(jí)聯(lián) Si MOSFET 的柵極。它具有大約 5 V 的穩(wěn)定的、基本上無(wú)滯后的閾值,因此很容易用 12 V 或 15 V 驅(qū)動(dòng)以實(shí)現(xiàn)完全增強(qiáng)和低 R DS(on),與典型的 25 V 的絕對(duì)最大值相比有很大的余量。簡(jiǎn)單的 SiC FET 柵極驅(qū)動(dòng)在名義上與硅 MOSFET 甚至 IGBT 級(jí)兼容,為現(xiàn)有產(chǎn)品設(shè)計(jì)升級(jí)提供潛在的向后兼容性。SiC MOSFET 和 GaN HEMT 單元在實(shí)踐中需要定制驅(qū)動(dòng)裝置,以實(shí)現(xiàn)最佳效率和足夠的柵極過(guò)壓保護(hù)。

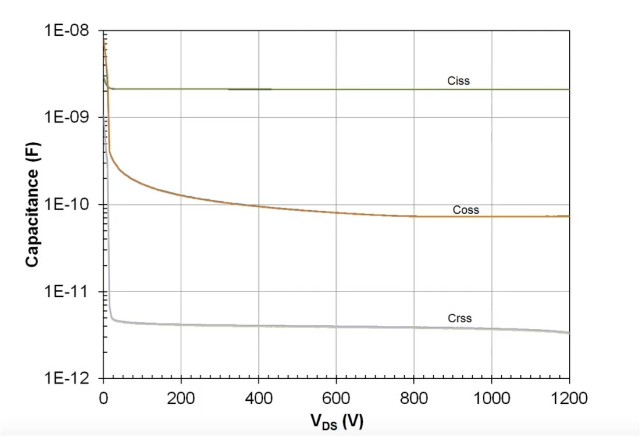

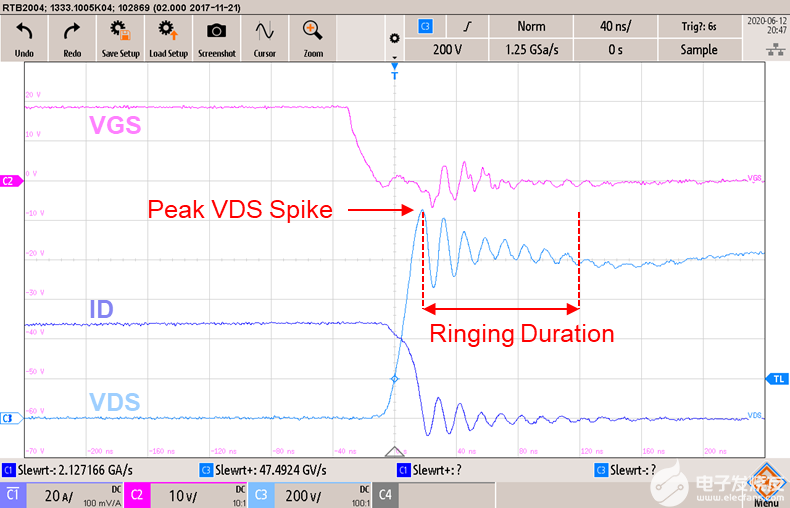

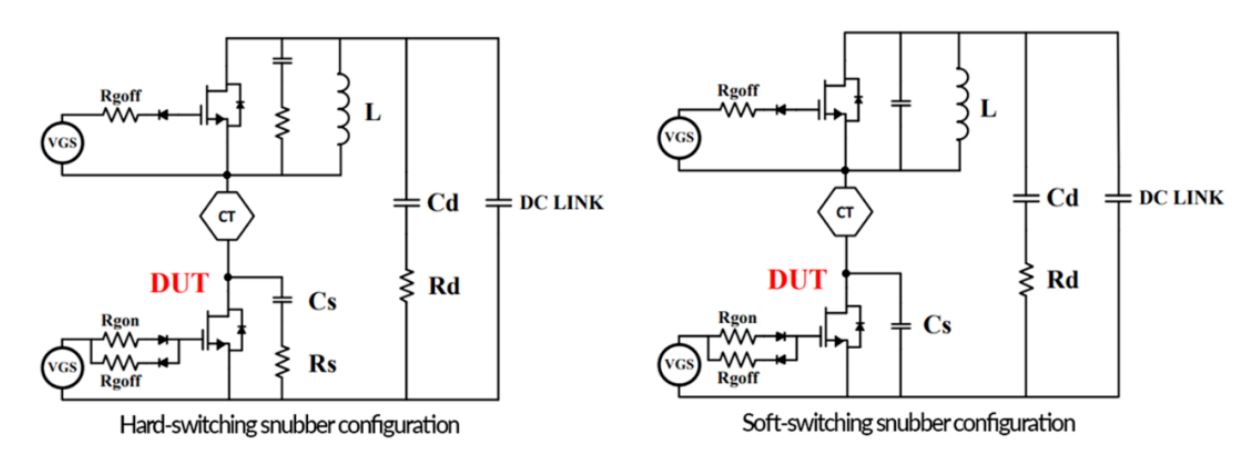

SiC FET 幾乎沒(méi)有柵漏電容或米勒電容 (C rss ),因?yàn)槠骷叽缧。夜苍垂矕排帕兄械?Si MOSFET 具有隔離效應(yīng),可實(shí)現(xiàn)超快速開(kāi)關(guān)。輸出電容 (C oss ) 以及相關(guān)的開(kāi)關(guān)能量 (E oss ) 很低,這也導(dǎo)致以最小的損耗實(shí)現(xiàn)快速開(kāi)關(guān)。邊緣速率如此之快,以至于在實(shí)際電路中,必須減慢 SiC FET 以限制電壓過(guò)沖和 EMI。這可以通過(guò)添加?xùn)艠O電阻器來(lái)實(shí)現(xiàn),但這種方法會(huì)導(dǎo)致高開(kāi)關(guān)頻率下無(wú)法接受的控制延遲,因此簡(jiǎn)單的 RC 緩沖器通常是更好的解決方案。電容器通常設(shè)置為大約 3 × C oss,串聯(lián)電阻的耗散最小。圖 4顯示了典型的 SiC FET 器件電容及其在阻塞狀態(tài)下隨漏電壓的變化。

C iss = C GS + C GD , (C DS短路), C rss = C GD , C oss = C DS + C GD

圖 4:SiC FET 器件電容

圖 4:SiC FET 器件電容SiC FET“體二極管”

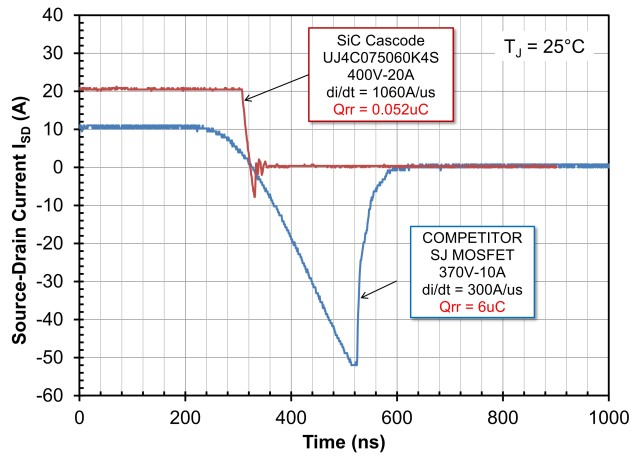

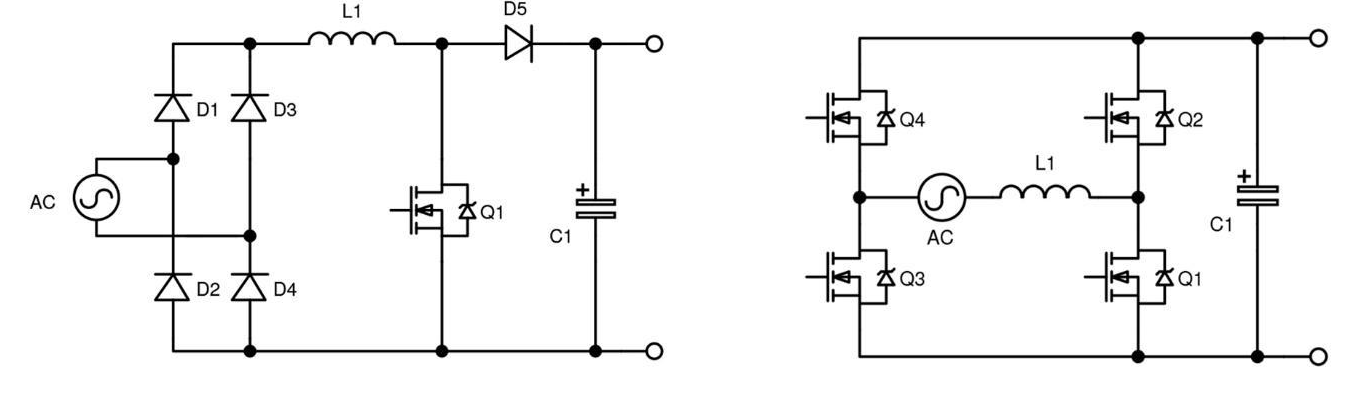

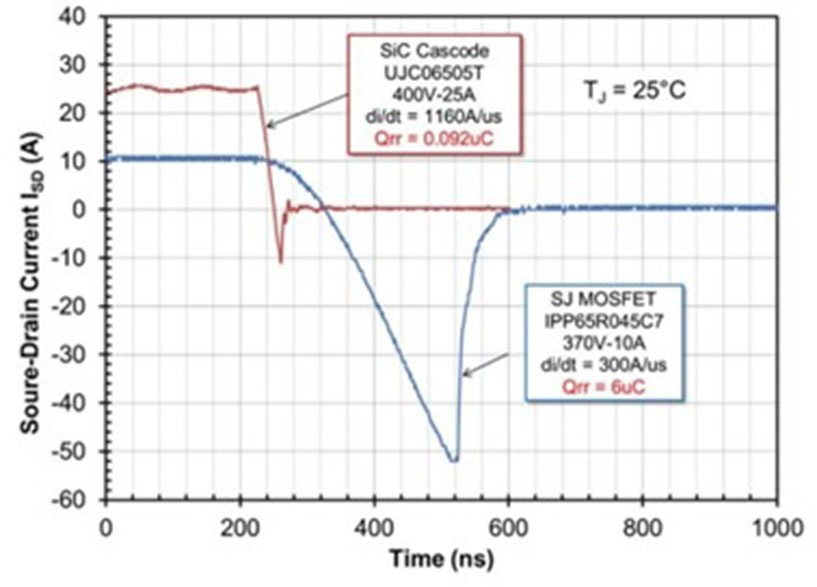

在電源轉(zhuǎn)換器中,完美的開(kāi)關(guān)應(yīng)該以低損耗雙向傳導(dǎo)。這實(shí)際上在交流電機(jī)驅(qū)動(dòng)器和帶有感性負(fù)載的轉(zhuǎn)換器等電路中是必需的——即所謂的三象限操作。IGBT 無(wú)法做到這一點(diǎn),需要一個(gè)并聯(lián)二極管,但硅和 SiC 中的 MOSFET 和 JFET 可以在柵極的控制下通過(guò)其溝道在任一方向?qū)щ姟?/font>MOSFET 還具有 JFET 中不存在的固有體二極管,并且該體二極管通過(guò)在具有感性負(fù)載的硬開(kāi)關(guān)轉(zhuǎn)換器中在器件通道通過(guò)柵極導(dǎo)通之前的“死區(qū)時(shí)間”中通過(guò)“換向”自動(dòng)導(dǎo)通,以允許反向電流。這種傳導(dǎo)存儲(chǔ)電荷 (Q rr),當(dāng)體二極管隨后反向偏置時(shí)恢復(fù),此操作會(huì)耗散大量峰值功率,隨著頻率的增加,峰值功率平均會(huì)逐漸升高,從而降低效率。對(duì)于硅 MOSFET,其影響可能非常嚴(yán)重,以至于實(shí)際上它們不能用于某些電路,例如流行的圖騰柱 PFC 級(jí),在連續(xù)導(dǎo)通模式下工作。SiC MOSFET 的 Q rr值可能比硅好 10 倍,但 SiC FET 仍然更好,因?yàn)槠骷妮敵鲭娙葺^低,并且低壓 MOSFET 中存儲(chǔ)的電荷最少。比較確實(shí)取決于器件的電壓等級(jí),但圖 5顯示了 SiC FET 和其他類(lèi)似硅超級(jí)結(jié) MOSFET 的典型反向恢復(fù)圖。

圖 5:碳化硅 FET 共源共柵的反向恢復(fù)電荷比硅超級(jí)結(jié) MOSFET 小 100 倍。

圖 5:碳化硅 FET 共源共柵的反向恢復(fù)電荷比硅超級(jí)結(jié) MOSFET 小 100 倍。雖然 SiC MOSFET 和 GaN 器件可能具有足夠低的反向恢復(fù)損耗或沒(méi)有反向恢復(fù)損耗,但反向傳導(dǎo)時(shí)的壓降卻是另一回事。這會(huì)在電源轉(zhuǎn)換器的死區(qū)時(shí)間內(nèi)產(chǎn)生顯著的損耗。Si 超結(jié) MOSFET 的二極管壓降通常約為 1 V,而 SiC MOSFET 的情況要差得多,其體二極管可以輕松壓降 4 V。三象限操作中的 GaN HEMT 單元降低的電壓 (V sd ) 是所述的總和我× [R通道的電壓和柵閾值電壓小于柵極-源極電壓,或:

V sd = ( V th – V gs ) + ( I sd × R on )?

GaN 的柵極閾值通常為 1.5 V,因此在高電流下,總壓降可能很高。如果柵極被驅(qū)動(dòng)為負(fù)以關(guān)閉(這很常見(jiàn)),則此電壓 (V gs ) 會(huì)增加源極-漏極壓降,導(dǎo)致 V sd為幾伏,這可能比其他技術(shù)要差得多。SiC FET 導(dǎo)通源極至漏極時(shí),與 GaN 器件類(lèi)似,溝道電阻有I × R壓降,但這僅因低壓級(jí)聯(lián) Si MOSFET 的體二極管兩端的電壓而增加,相對(duì)而言低的。產(chǎn)生的正向壓降通常約為 1.5 V,優(yōu)于 SiC MOSFET 或 GaN 性能。

證明 SiC FET 的可靠性

寬帶隙開(kāi)關(guān)是穩(wěn)健的,尤其是因?yàn)樗鼈児逃械母邷睾透邠舸╇妷耗芰Γ?SiC FET 的一個(gè)特殊優(yōu)勢(shì)是沒(méi)有 SiC 柵極氧化物,如 SiC MOSFET 中存在的,以及它們的退化問(wèn)題來(lái)自高電場(chǎng)。共源共柵中的 Si MOSFET 是一種穩(wěn)健的低電壓類(lèi)型,具有高閾值電壓和厚柵極氧化層,此外還受到內(nèi)置齊納鉗位的保護(hù)。在實(shí)踐中,碳化硅 FET 已證明其非常可靠,其部件現(xiàn)在通常能達(dá)到汽車(chē) AEC-Q 等級(jí)。

另一個(gè)重要的考慮因素是過(guò)壓和短路等意外應(yīng)力事件期間的可靠性。SiC FET 具有強(qiáng)大的雪崩能力,可通過(guò) JFET 漏柵擊穿激活。通過(guò)圖 3 中的RG 產(chǎn)生的電流會(huì)降低電壓,從而開(kāi)啟 JFET 并鉗位過(guò)壓。Si MOSFET 現(xiàn)在以高度可控的方式發(fā)生雪崩,因?yàn)檠┍辣Wo(hù)二極管包含在每個(gè)單元的制造中,并且耗散的功率很小。SiC MOSFET 也具有雪崩額定值,但 GaN HEMT 單元沒(méi)有,這迫使制造商在較低的電壓下對(duì)部件進(jìn)行額定值,以在工作和破壞性擊穿電壓之間獲得足夠的裕度。

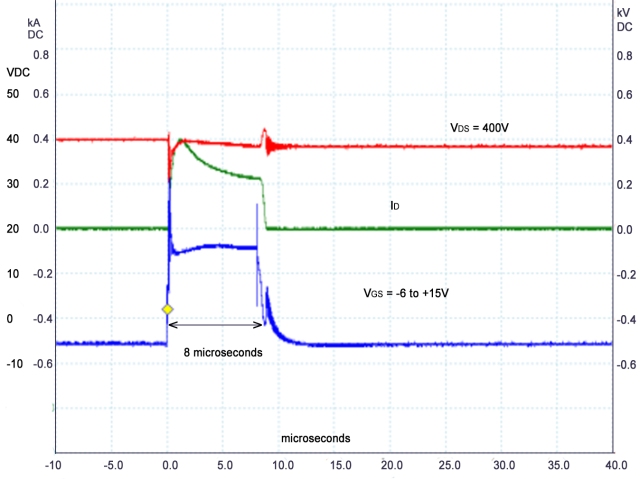

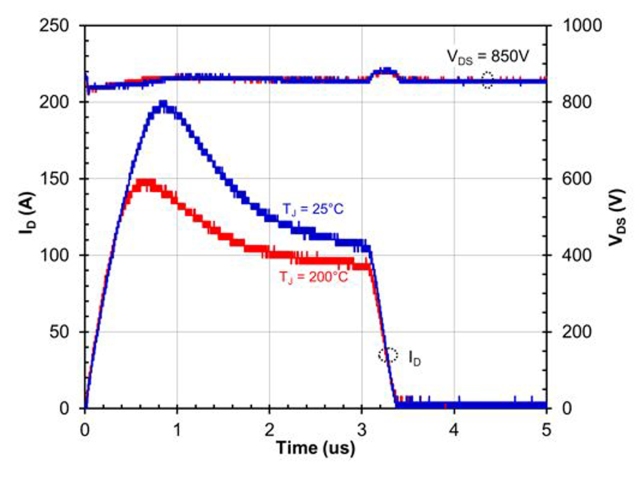

SiC FET 還具有良好的短路電流特性:在高電流下,溝道兩端的電壓降梯度會(huì)導(dǎo)致自然的“夾斷”效應(yīng)來(lái)限制電流。與 MOSFET 和 IGBT 不同,短路電流與柵極電壓無(wú)關(guān),而且 SiC FET 通道的導(dǎo)通電阻正溫度系數(shù)也有助于降低限制電流并將應(yīng)力分散到芯片中的各個(gè)單元上。效果如此一致,以至于 SiC FET 可用作線(xiàn)性電路中的精確限流器件。汽車(chē)應(yīng)用中的一項(xiàng)典型測(cè)試是使器件能夠承受至少 5 μs 的短路,圖 6顯示了一個(gè) 750-V SiC FET 能夠承受 8 μs 的應(yīng)力而沒(méi)有退化。圖 7 顯示導(dǎo)通電阻隨溫度增加的影響,使用額定值為 1,200V 的 SiC FET 將短路電流降低到很大程度上獨(dú)立于初始結(jié)溫的最終值。

圖 6:SiC FET 可承受來(lái)自 400V 總線(xiàn)的 8μs 短路應(yīng)力。

圖 6:SiC FET 可承受來(lái)自 400V 總線(xiàn)的 8μs 短路應(yīng)力。 圖 7:SiC FET 短路電流與初始結(jié)溫?zé)o關(guān)。

圖 7:SiC FET 短路電流與初始結(jié)溫?zé)o關(guān)。為了保持可靠性,封裝的 SiC FET 中的溫升和梯度應(yīng)該最小化,并且 SiC 的熱導(dǎo)率是硅或 GaN 的 3 倍以上,在這里是一個(gè)優(yōu)勢(shì)。最新的器件還使用銀燒結(jié)而不是焊接進(jìn)行芯片連接,這使界面的熱導(dǎo)率提高了 6 倍,從而保持較低的結(jié)溫上升和較高的可靠性。

其他 SiC FET 應(yīng)用

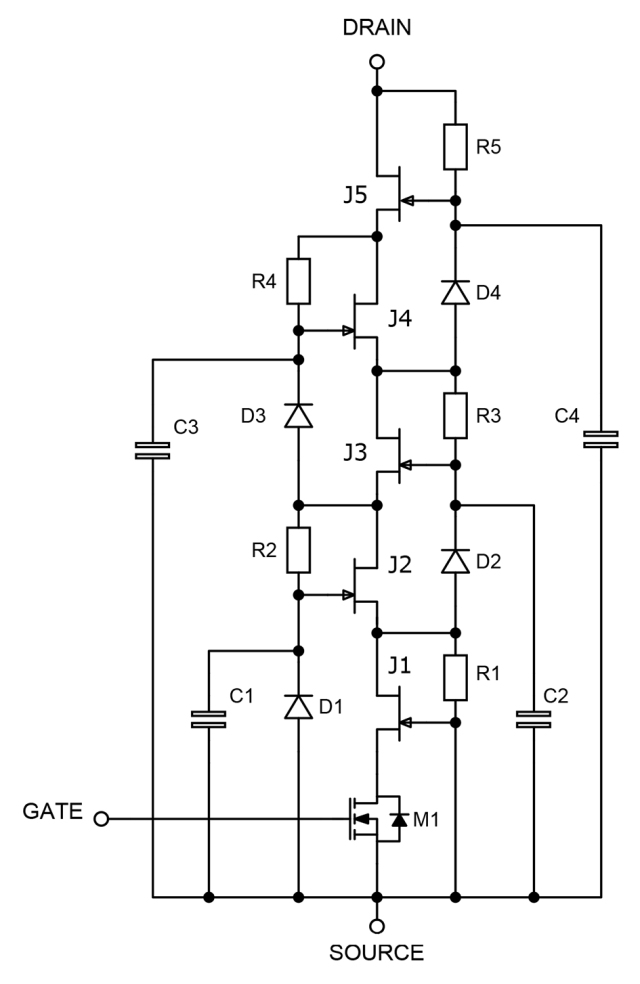

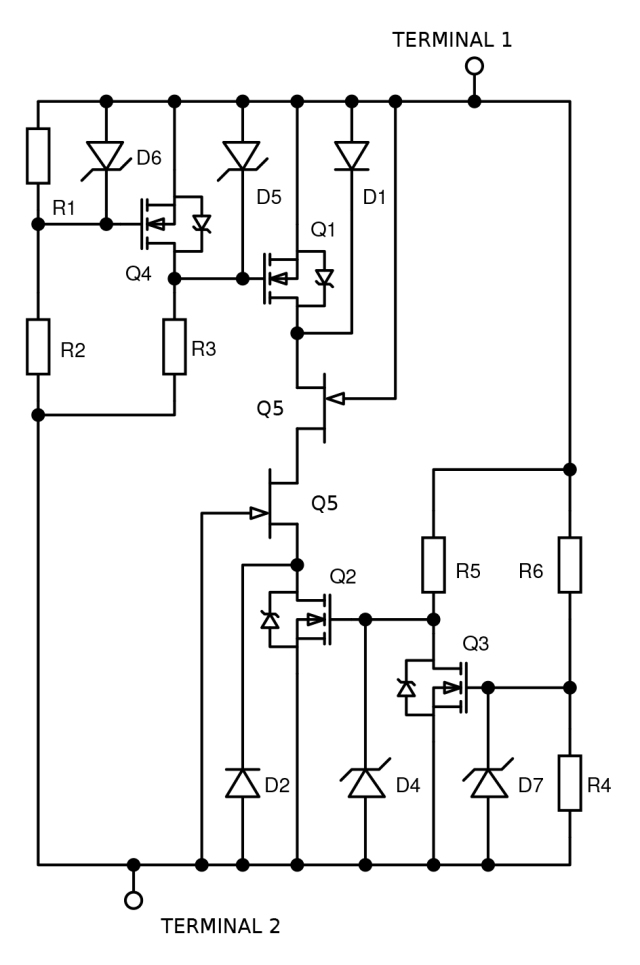

碳化硅場(chǎng)效應(yīng)晶體管在高效功率轉(zhuǎn)換器中找到了自然的歸宿,可提供高達(dá) 1,700V 的額定電壓,適用于典型的工業(yè)三相應(yīng)用。然而,通過(guò)在控制硅 MOSFET 上“堆疊”碳化硅 JFET,可以輕松擴(kuò)展共源共柵原理(圖 8)。已開(kāi)發(fā)出具有 40 kV 額定值的演示該原理的模塊。3

圖 8:堆疊共源共柵原理可用于額定電壓為數(shù)十千伏的高電壓。

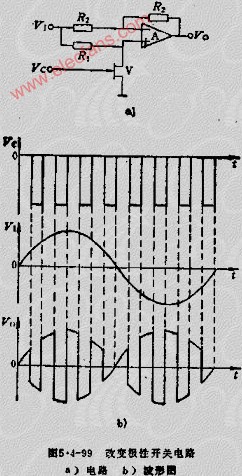

圖 8:堆疊共源共柵原理可用于額定電壓為數(shù)十千伏的高電壓。如前所述,碳化硅 JFET 具有接近恒定的飽和電流特性,具有柵極-源極和漏極電壓,這可用于電流限制器或斷路器等電路保護(hù)應(yīng)用。圖 9顯示了使用 SiC FET 共源共柵的自偏置斷路器概念,它是真正的“兩端”,沒(méi)有外部輔助電源軌或內(nèi)部 DC/DC 轉(zhuǎn)換器。

圖 9:兩端自偏置斷路器概念

圖 9:兩端自偏置斷路器概念在提高性能和價(jià)值方面取得進(jìn)展

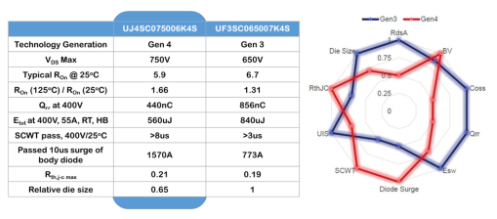

SiC FET 經(jīng)歷了幾代技術(shù)的進(jìn)步。最新的 GEN4 帶來(lái)了一系列改進(jìn),包括可用的電壓范圍、更好的導(dǎo)通電阻的單元密度,以及提高熱性能的燒結(jié)芯片連接。現(xiàn)在使用基板減薄技術(shù),因?yàn)橥ǖ离娮璺浅5停ㄟ^(guò)基??板本身的傳導(dǎo)損耗成為一個(gè)限制因素。在動(dòng)態(tài)方面,部件也得到了改進(jìn),特別是輸出電容 (C oss)。這降低了硬開(kāi)關(guān)拓?fù)洌ɡ邕B續(xù)傳導(dǎo)模式下的圖騰柱 PFC)的損耗,并在軟開(kāi)關(guān)諧振電路(例如 LLC 或 PSFB)中實(shí)現(xiàn)更高頻率的操作。開(kāi)關(guān)邊緣速率現(xiàn)在如此之快,以致于為設(shè)備提供了超快和有意減慢的“快速”額定值,以適應(yīng)邊緣速率對(duì)性能并不重要并且可能導(dǎo)致 EMI 和故障問(wèn)題的應(yīng)用,例如在電機(jī)驅(qū)動(dòng)中。

封裝也從第一個(gè) SiC FET 發(fā)展而來(lái),由 Si MOSFET 和 SiC FET 裸片并排排列形成,并帶有互連線(xiàn)鍵合。例如,這可實(shí)現(xiàn) TO-247 封裝的靈活性,但為了降低成本和提高性能,“堆疊”芯片布置現(xiàn)在普遍用于大電流的大芯片,尤其是在緊湊模塊中并聯(lián)部件時(shí)。為了獲得更好的熱性能,焊片貼裝已讓位于銀燒結(jié),而 DFN 8 × 8 封裝可實(shí)現(xiàn)用于兆赫茲開(kāi)關(guān)的低電感、高頻布局。TO-220、TO-247 和 D2PAK 封裝仍然很受歡迎,因?yàn)樗鼈兛梢詫?SiC FET 改造為舊設(shè)計(jì),甚至是使用 IGBT 的設(shè)計(jì)。

除此之外,使用碳化硅場(chǎng)效應(yīng)晶體管從其電氣性能中增加的價(jià)值得到了成本降低計(jì)劃的補(bǔ)充,該計(jì)劃通過(guò)持續(xù)改進(jìn)生產(chǎn)良率和向 8 英寸晶圓發(fā)展。

SiC FET 是一種引人注目的解決方案

現(xiàn)在,最新一代 SiC FET 更接近理想的開(kāi)關(guān)。傳導(dǎo)和動(dòng)態(tài)損耗是有史以來(lái)最低的,使高頻功率轉(zhuǎn)換級(jí)具有 99% 以上的效率,并相應(yīng)地節(jié)省了能源、尺寸和重量。設(shè)計(jì)師對(duì)“理想”有更廣泛的定義;他們還希望該部件在一個(gè)方便的封裝中易于驅(qū)動(dòng),具有穩(wěn)定的特性,在廣泛的操作和故障條件下。與此同時(shí),設(shè)備最終用戶(hù)需要可靠的最終產(chǎn)品,其總生命周期成本優(yōu)于舊技術(shù)實(shí)施。UnitedSiC 的 SiC FET 可通過(guò)一系列額定電壓為 650 V 至 1,700 V 且導(dǎo)通電阻低至 7 mΩ 的部件實(shí)現(xiàn)這一點(diǎn)。

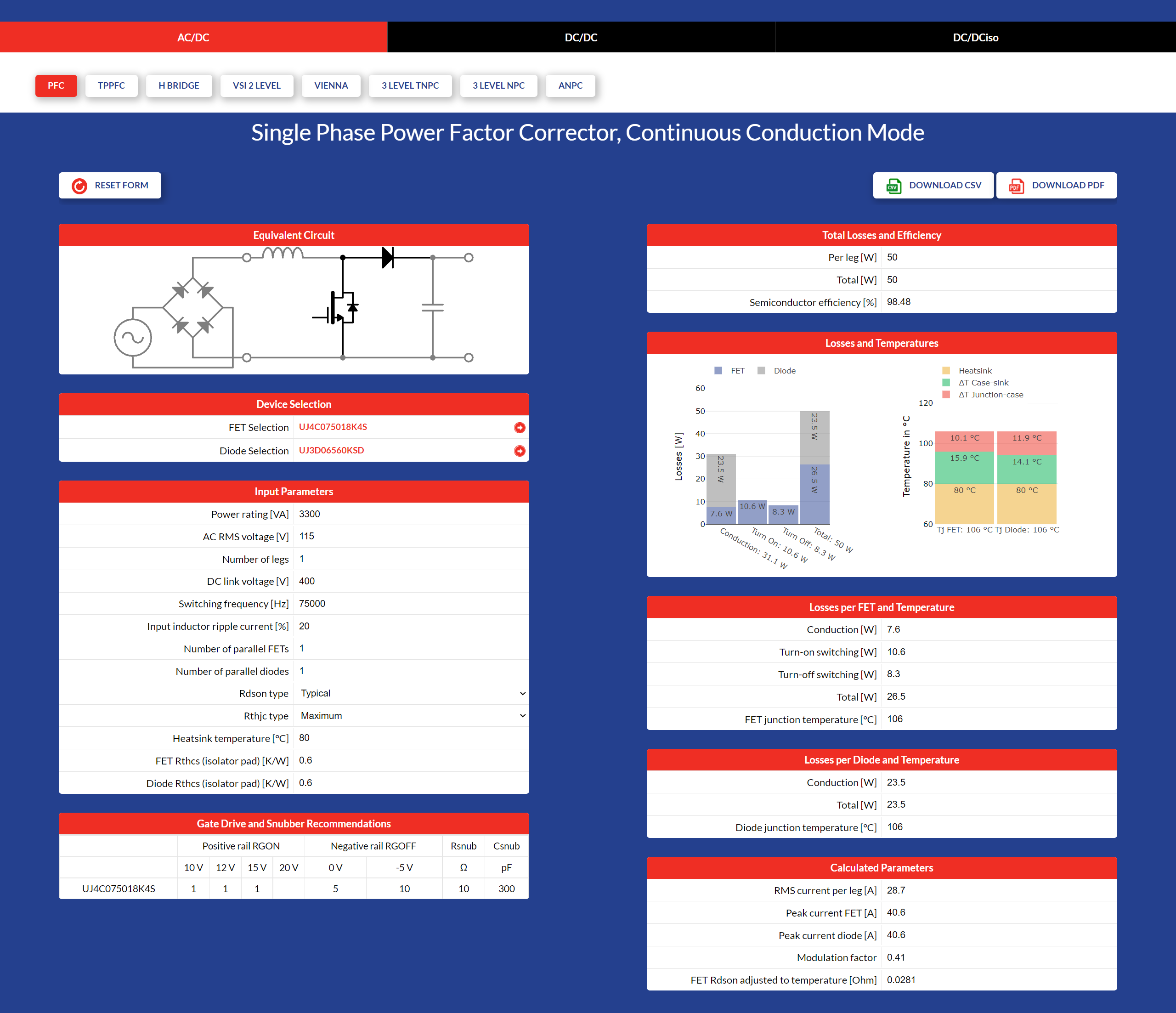

作為設(shè)計(jì)輔助工具,UnitedSiC 的“FET JET”計(jì)算器4允許在選擇的功率轉(zhuǎn)換拓?fù)浣Y(jié)構(gòu)中對(duì)其任何器件進(jìn)行快速選擇和性能預(yù)測(cè),包括 PFC 級(jí)和隔離/非隔離 DC/DC 轉(zhuǎn)換器。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論