可編程邏輯器件(PLD)是嵌入式工業(yè)設(shè)計的關(guān)鍵元器件。在工業(yè)設(shè)計中,PLD已經(jīng)從提供簡單的膠合邏輯發(fā)展到使用FPGA作為協(xié)處理器。該技術(shù)在通信、電機控制、I/O模塊以及圖像處理等應(yīng)用中支持I/O擴展,替代基本的微控制器(MCU)或者數(shù)字信號處理器(DSP)。

隨著系統(tǒng)復(fù)雜度的提高,F(xiàn)PGA還能夠集成整個SoC,與分立的MCU、DSP、ASSP,以及ASIC解決方案相比,大幅度降低了成本。

不論是用作協(xié)處理器還是SoC,Altera FPGA在您的工業(yè)應(yīng)用中都具有以下優(yōu)勢:

1. 設(shè)計集成——使用FPGA作為協(xié)處理器或者SoC,在一個器件平臺上集成IP和軟件堆棧,從而降低成本。

2. 可重新編程能力——在一個公共開發(fā)平臺的一片F(xiàn)PGA中,使工業(yè)設(shè)計能夠適應(yīng)協(xié)議、IP以及新硬件功能的發(fā)展變化。

3. 性能調(diào)整——通過FPGA中的嵌入式處理器、定制指令和IP模塊,增強性能,滿足系統(tǒng)要求。

4. 過時保護——較長的FPGA產(chǎn)品生命周期,通過FPGA新系列的器件移植,延長工業(yè)產(chǎn)品的生命周期,保護硬件不會過時。

5. 熟悉的工具——使用熟悉的、功能強大的集成工具,簡化設(shè)計和軟件開發(fā)、IP集成以及調(diào)試。

設(shè)計集成

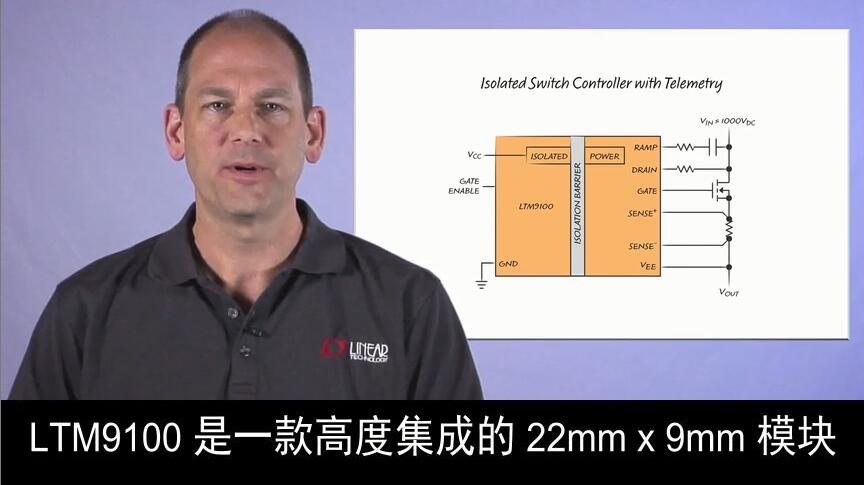

現(xiàn)代工業(yè)系統(tǒng)設(shè)計人員面臨很多挑戰(zhàn),包括,系統(tǒng)復(fù)雜度、標準的變化、性能需求,以及系統(tǒng)總成本等,如圖1所示。

圖1.關(guān)鍵工業(yè)設(shè)計挑戰(zhàn)

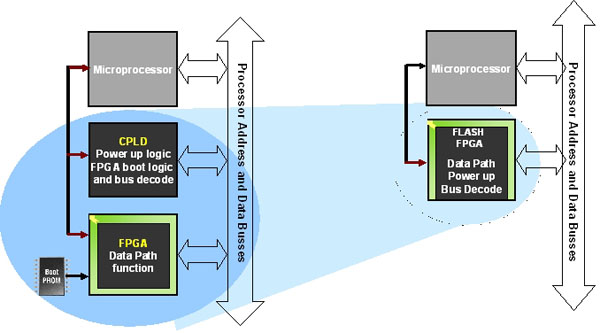

作為一名工業(yè)系統(tǒng)設(shè)計人員,您可以確定是否使用FPGA作為協(xié)處理器(也稱為I/O輔助或者I/O hub器件),還是完整的SoC解決方案。您可以在相同的電路板上組合使用標準主處理器和FPGA,由外部主處理器完成系統(tǒng)處理功能。

然而,功能固定的處理器在工業(yè)應(yīng)用中通常缺少關(guān)鍵的接口、功能或者性能。您可以將部分處理任務(wù)移到FPGA中,從而減輕處理器的工作。或者,您在一個基于FPGA的SoC平臺上集成所有處理器功能,降低設(shè)計復(fù)雜度,減少系統(tǒng)總成本。

很多MCU或者DSP解決方案如果要同時運行電機控制任務(wù)和通信功能,其帶寬將無法滿足需求。結(jié)果,您可能需要增加其他的ASSP、MCU或者FPGA器件,如果目前的電路板無法承載這些器件,那么只能將其作為昂貴的置入卡來使用。相似的,不同的現(xiàn)場總線以及發(fā)展的工業(yè)以太網(wǎng)協(xié)議標準也需要針對每一協(xié)議采用專用ASSP、MCU或者FPGA器件。由于某些標準需要協(xié)議專用硬件(MAC)和協(xié)議專用軟件堆棧,因此,這些工作是必須的。FPGA支持您在協(xié)處理器中集成系統(tǒng)功能,根據(jù)需要隨時修改設(shè)計。

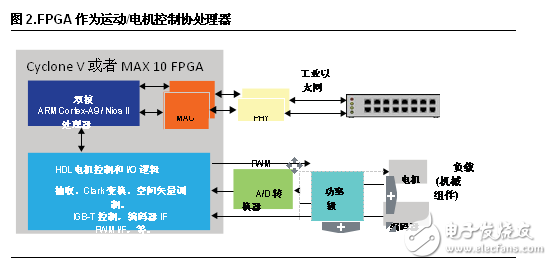

圖2顯示了一個運動和電機控制平臺,它發(fā)揮了Altera FPGA的優(yōu)勢,作為DSP卸載引擎和工業(yè)網(wǎng)絡(luò)的協(xié)處理器。電機控制器通過控制速度和電流(轉(zhuǎn)換為扭矩設(shè)置),設(shè)置電機的能效和精度。相似的,運動控制則主要完成位置和時序精度控制功能。在很多情況下,電子硬件都是相似的,主要的差別在于控制軟件或者算法,以及I/O接口。

圖2中的例子顯示了一個典型的控制器,它依靠一個主MCU或者DSP器件(主處理器)來運行算法,驅(qū)動電機或者運動控制器的電源級。當主處理器達到其性能極限時,設(shè)計人員可以提高器件時鐘速率,以提升處理器性能。但是,對性能增益是有限制的,這種方法可能會帶來其他問題,例如,需要更新到速度更快的存儲器,其他硬件的性能,以及優(yōu)化軟件需要更多的時間等。

在這種情況下,將某些主處理器功能卸載到FPGA協(xié)處理器中有助于簡化系統(tǒng),使用FPGA進行通信,幫助您隨著工業(yè)以太網(wǎng)協(xié)議等標準的發(fā)展而靈活的進行修改。然后,您對FPGA重新編程,使用相同的硬件平臺來滿足需求。

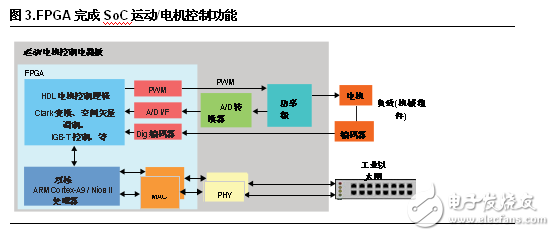

在一個SoC FPGA器件平臺上集成設(shè)計元器件,進一步簡化了設(shè)計復(fù)雜度,降低了系統(tǒng)總成本。圖3顯示了一個簡單的工業(yè)電機控制系統(tǒng),F(xiàn)PGA現(xiàn)在起到了SoC的功能,集成DSP模塊、存儲器、視頻圖形控制器、電機編碼器以及其他元器件。您可以簡單的加入PHY和其他模擬以及電源器件,從而完成設(shè)計。

此外,電機控制應(yīng)用通常還需要采用反饋機制來計算當前速率和位置。對于FPGA,很多經(jīng)過優(yōu)化的數(shù)字編碼器接口IP內(nèi)核只能用作IP,支持在接口上使用FPGA。在FPGA上集成IP減小了電路板尺寸,減少了元器件數(shù)量,簡化了裝配,降低了存儲要求。這種集成方法減少了電路板上的元器件數(shù)量,從而提高了系統(tǒng)可靠性。Altera FPGA支持很多其他系統(tǒng)功能,例如,嵌入式處理器、DSP模塊、LCD顯示屏和視頻處理器等。

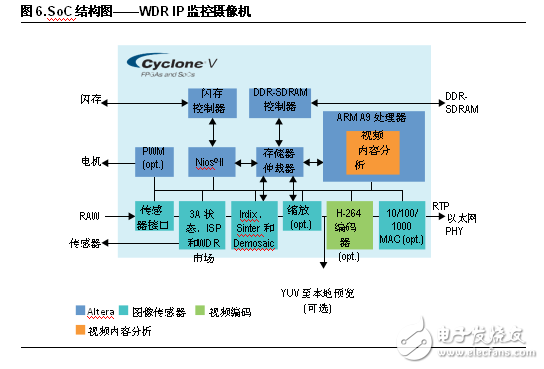

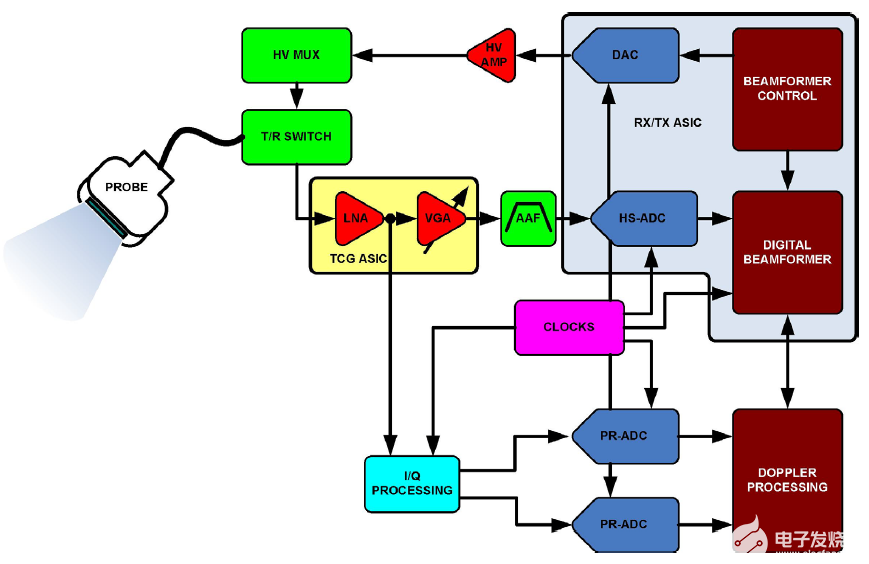

圖4顯示了另一應(yīng)用實例,其FPGA用作視頻監(jiān)控應(yīng)用中的協(xié)處理器。視頻監(jiān)控市場越來越多的采用了寬動態(tài)范圍(WDR)攝像機傳感器,能夠分辨從背景到逆光條件下的目標物體。只有FPGA具有WDR圖像傳感器流水線(ISP)協(xié)處理所需的帶寬,將視頻流送入DSP器件進行視頻編碼,例如,H.264等。DSP器件缺少處理WDR ISP所需的帶寬和接口,不具備運行其他監(jiān)控功能的性能,例如,視頻分析等。

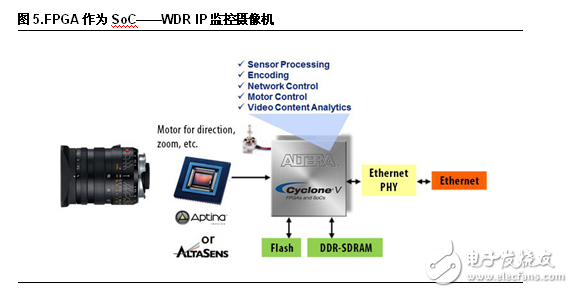

另一個例子,圖5顯示了FPGA作為視頻監(jiān)控應(yīng)用中的SoC。用作SoC時,F(xiàn)PGA支持您在一片F(xiàn)PGA中集成所有的組件——ISP、視頻分析、編碼和聯(lián)網(wǎng)功能。這一方法不需要采用后端DSP器件,支持實現(xiàn)更緊湊的集成設(shè)計。

圖6顯示了在Cyclone? V SoC上實現(xiàn)的SoC系統(tǒng)實例的結(jié)構(gòu)圖。

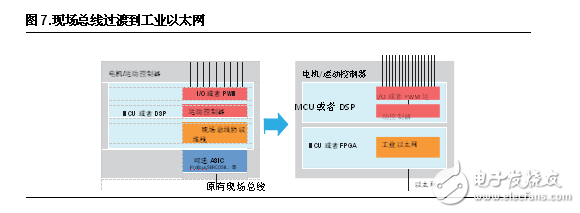

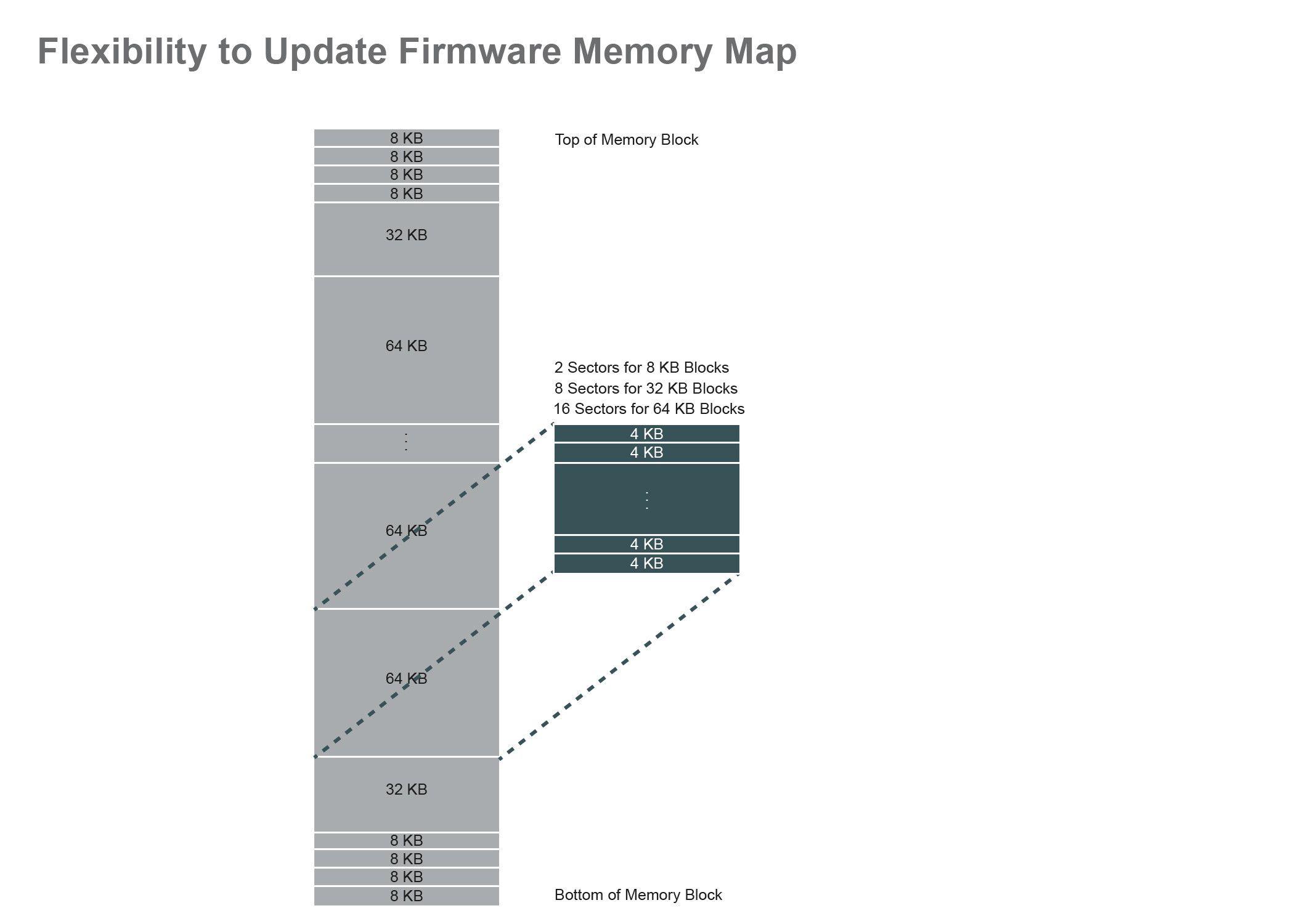

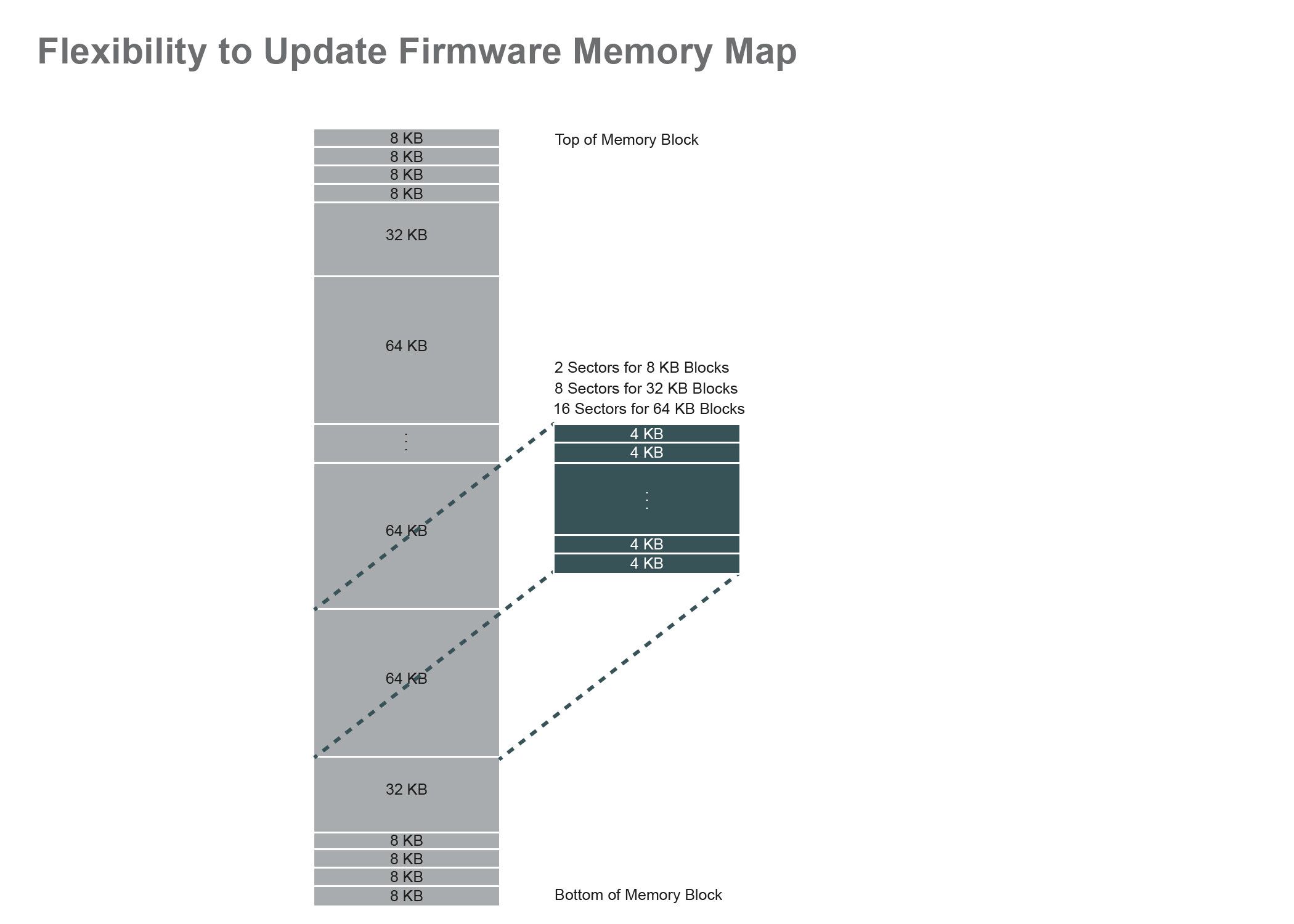

可重新編程能力

利用FPGA的可重新編程能力,您很容易適應(yīng)標準的發(fā)展,支持設(shè)計重用。即使您在工業(yè)應(yīng)用中只采用一個MCU、DSP、ASSP或者ASIC解決方案,很多應(yīng)用還是需要分立器件來處理工業(yè)通信等功能,例如,可選的現(xiàn)場總線專用ASIC或者FPGA,,如圖7所示。當網(wǎng)絡(luò)規(guī)范或者功能需求出現(xiàn)變化時,您通常會集中精力來開發(fā)多塊PCB,以支持不同的協(xié)議和功能,每一平臺都需要額外的軟件導(dǎo)入導(dǎo)出時間。這大大提高了解決方案的總成本。

或者,您可以使用FPGA作為通信協(xié)處理器。您可以在一個硬件平臺上設(shè)計一個通信子系統(tǒng),隨時修改網(wǎng)絡(luò)協(xié)議,支持多種產(chǎn)品。您通過在一片F(xiàn)PGA中更靈活的集成主MCU或者DSP控制功能、多個處理器和其他IP以及接口,開發(fā)小外形器件,節(jié)省空間,降低成本。由于能夠針對多種產(chǎn)品采用一個平臺,減少了要開發(fā)的硬件數(shù)量,簡化了軟件的導(dǎo)入導(dǎo)出,因此,您將獲得幾個月甚至更長的產(chǎn)品及時面市優(yōu)勢。

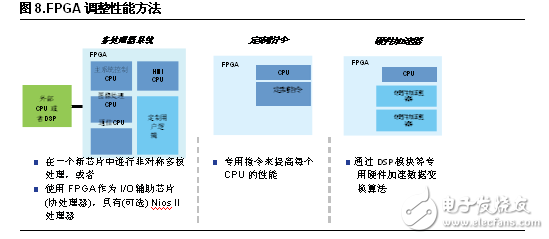

調(diào)整性能

任何工業(yè)控制系統(tǒng)的關(guān)鍵所在是主機/主MCU、DSP、ASIC或者ASSP器件的處理功能。當性能成為設(shè)計難題時,F(xiàn)PGA提供以下方法來調(diào)整處理性能,如圖8所示。

■ 使用高性能外部處理器以及FPGA內(nèi)置的多個嵌入式處理器之一。您還可以將所有處理功能集成到FPGA中,作為SoC。

■ 加入定制指令以及您的處理器代碼,從而加速專用處理器指令;浮點就是一個很好的例子。

■ 通過DSP模塊等專用硬件加速數(shù)據(jù)轉(zhuǎn)換算法。

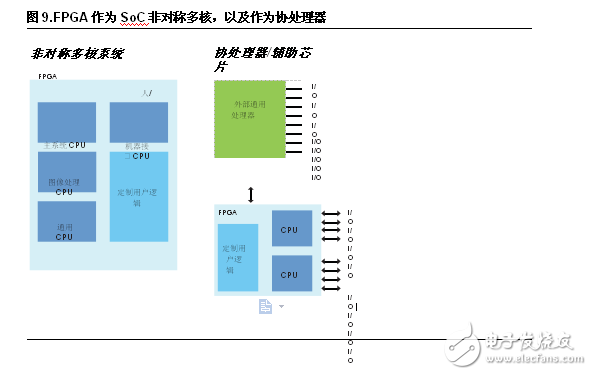

多核處理

對于靈活的多處理器設(shè)計,您可以從多種實現(xiàn)方式中進行選擇。嵌入式工業(yè)設(shè)計人員通常對非對稱協(xié)處理感興趣,把FPGA作為I/O輔助芯片或者SoC。非對稱多處理器意味著多功能產(chǎn)品可以采用專用處理器來實現(xiàn)每一主要功能。這尤其適合滿足當今迫切的應(yīng)用需求,例如,智能電話等。開發(fā)人員以前在PCB上采用多個處理器來開發(fā)這類系統(tǒng)。現(xiàn)在,您可以在一片F(xiàn)PGA中每個分區(qū)的專用處理模塊上來完成這一工作,如圖9所示。

這類應(yīng)用的一個例子就是高性能伺服驅(qū)動應(yīng)用,它需要高性能主處理器(或者多處理器)來完成每一主要功能。專用處理器執(zhí)行應(yīng)用代碼,通信處理器提供現(xiàn)場總線或者以太網(wǎng)鏈路,圖形或者圖像處理器提供顯示功能,包括數(shù)字電機編碼器、PWM功能和電源控制等其他定制邏輯和接口。您還可以將所有這些功能集成到FPGA中,作為協(xié)處理器或者完整的SoC。

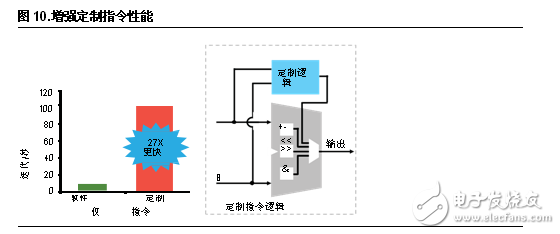

定制指令

您可以通過增加定制指令以及相應(yīng)的處理器代碼來調(diào)整處理器性能。這一方法加速了專用處理器指令,如圖10所示。

您可以在嵌入式處理器指令集中加入定制指令,以加速對時間要求較高的軟件算法。圖10中的例子顯示了您怎樣在Altera Nios? II處理器的算術(shù)邏輯單元(ALU)中加入定制指令邏輯。使用定制指令將復(fù)雜的標準指令序列簡化為在硬件中實現(xiàn)的嵌入指令。您可以在各種應(yīng)用中使用這一功能。例如,您可以優(yōu)化DSP的軟件內(nèi)循環(huán)、數(shù)據(jù)包頭處理以及需要大量計算的應(yīng)用。Quartus? II軟件提供配置GUI,支持Nios II處理器的256條定制指令。圖10中的例子使用了64 Kilobyte (KB) CRC緩沖。在Nios II處理器中,與只采用軟件操作相比,定制指令能夠?qū)?a target="_blank">CPU的性能提高27倍。

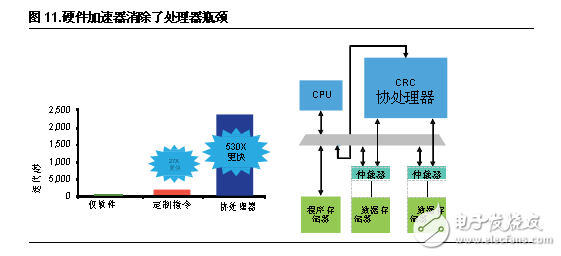

硬件加速

除了定制指令,您還可以使用硬件加速器,例如DSP模塊、視頻模塊以及其他IP,從而消除數(shù)據(jù)瓶頸。圖11顯示了與僅采用定制指令的同一Nios II處理器系統(tǒng)相比,采用同時或者并行數(shù)據(jù)協(xié)處理器功能將系統(tǒng)性能提高了530倍。在并行數(shù)據(jù)協(xié)處理器期間,處理器的中央處理單元(CPU)啟動并停止協(xié)處理器,協(xié)處理器獲取數(shù)據(jù),存儲結(jié)果,CPU同時運行應(yīng)用代碼。這適用于模塊數(shù)據(jù)操作,例如,電機控制或者運動控制應(yīng)用中常見的DSP功能。

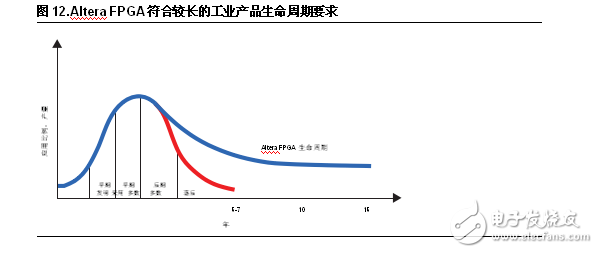

過時保護

生命周期較長的FPGA降低了產(chǎn)品過時的風險。Altera FPGA的產(chǎn)品生命周期非常符合工業(yè)設(shè)備的長生命周期要求,能夠穩(wěn)定的供應(yīng)器件,如圖12所示。

大部分MCU、DSP或者ASSP器件的產(chǎn)品生命周期比FPGA短得多,這是因為和Altera相比,其供應(yīng)商通常會更快的停止供應(yīng)成熟器件。這類器件設(shè)計用于針對大批量用戶在短期內(nèi)實現(xiàn)特定應(yīng)用。而且,雖然目前產(chǎn)品中的ASIC器件可以工作15年以上,但是很多已經(jīng)接近壽命終了,迫使設(shè)計人員考慮FPGA等其他長壽命器件。雖然新ASIC設(shè)計正在開發(fā)中,但是設(shè)計人員還不能迅速更新這些產(chǎn)品以跟上標準的發(fā)展,或者滿足新功能的要求。

相反,F(xiàn)PGA涵蓋了多種應(yīng)用和市場,與大批量產(chǎn)品的特殊應(yīng)用無關(guān)。因此,Altera在很長時間內(nèi)生產(chǎn)的FPGA是您的高性價比選擇。您可以更好的管理穩(wěn)定的供應(yīng)鏈,它會含有很多其他半導(dǎo)體元器件。在您的設(shè)計中使用FPGA平臺時,您能夠隨時更新并修改您的設(shè)計。您可以重復(fù)使用IP,在很短的時間內(nèi)將設(shè)計導(dǎo)入到新系列FPGA中,這要比設(shè)計新MCU、DSP、ASSP或者ASIC快得多。

隨著時間的推移,Altera FPGA幫助您提高了多條產(chǎn)品線的商業(yè)價值,降低產(chǎn)品過時的成本。

本文選自電子發(fā)燒友《智能工業(yè)特刊》,更多優(yōu)質(zhì)內(nèi)容,馬上下載閱覽

電子發(fā)燒友App

電子發(fā)燒友App

評論