摘要 隨著器件尺寸的持續減小,以及在器件的制造中不斷使用新材料,對晶圓級可靠性測試的要求越來越高。在器件研發過程中這些發展也對可靠性測試和建模也提出了新的要求。為了滿足這些挑戰需要開發更快、更敏感、更具靈活性的可靠性測試工具。

隨著集成電路技術的持續發展,芯片上將集成更多器件,芯片也將采用更快的時鐘速度。在這些要求的推進下,器件的幾何尺寸將不斷縮減,并要求在芯片的制造工藝中并不斷采用新材料和新技術。這些改進對于單個器件的壽命來說影響非常大,可能造成局部區域的脆性增加、功率密度提高、器件的復雜性增加以及引入新的失效機制。從前制造器件壽命達100年的工藝在縮減尺寸之后制造的器件可能壽命不到10年——這些對于那些設計壽命為10年左右的產品來說無疑是個不利的消息。同時較小的容錯空間意味著壽命問題必須在設計的一開始就給予考慮,并且在器件的開發和制造過程中一直進行監控,這個過程需要持續到最終產品完成。時至今日,器件壽命上一個很小的變化可能帶來整個產品的徹底失敗。

盡管大部分可靠性測試都是在器件封裝級別上完成的,但許多IC制造商現在正在向晶圓級測試(WLT)轉移。這種轉移一般出于多方面考慮,包括將來把可靠性測試融入到晶圓的制造流程中。同已封裝好的失效器件相比,晶圓級可靠性(WLR)測試也節省了大量的時間、產能、金錢以及材料的損耗。其返工時間較短,可以直接從生產線中將失效的晶圓抽出并測試,而不需要先將這部分器件封裝之后再測試,封裝并測試的流程需要花上兩周的時間。由于大部分測試流程相似,保證了可靠性測試向WLT轉移的簡易性。

在半導體器件中,應力檢測是衡量器件運行壽命和損耗失效的常用方法。該測試關注的失效機制位于圖1所示典型失效率浴缸曲線的右側;這就是說,并不關注與器件初用期或制造期相關的失效。

通過應力檢測可以方便地做出曲線,并外推來預測器件的運行壽命。由于器件的壽命通常都是用年來度量的,因為需要采用一些手段來加速測試。最有效的方法是讓器件處于應力過載狀態,然后測量可以衡量性能降低的關鍵參數,將測得的參數外推得到器件的壽命。在圖2中,曲線的右下部分(實測數據)就是在高應力狀態下測得的。通過實測數據可以進行線性外推用于預測正常工作條件下器件的壽命(曲線的左上部)。

一般的WLR測試均使用應力測試技術,其中包括熱載流子注入(HCI)或溝道熱載流子、負偏壓溫度不穩定性(NBTI)、電遷移、時間相關介電層擊穿(TDDB)或電荷擊穿(QBD)。這些測試技術在主流CMOS器件的開發和工藝控制中運用得非常普遍(傳統HCI和NBTI測試的介紹請參見附文)。

新的尺寸縮減和新材料的使用要求對這些完備的測試方法進行修改,并且升級測試工具以適應新技術。下面給出兩個例子,一個是如何克服PMOS器件中與NBTI測試相關的挑戰,另一個是在使用高k柵極材料的晶體管中,如何克服與電荷俘獲現象相關的挑戰。

NBTI測試中的退化緩和

NBTI測試的特別之處在于其性能退化在去掉應力加載之后還可以恢復(圖3)。當柵極電壓(Vg)引入的應力卸載之后,漏極電流(Id)和閾值電壓(Vt)的退化會逐漸恢復并最終返回到起始的情況。恢復的速度對溫度的依賴程度很高。在室溫下完全恢復的情況也見諸報道。當恢復之后如果再次在柵極引入應力,性能退化將按照上次退化的曲線發展。但在較高溫度時,將有一部分退化的性能是無法抵消的,這種情況稱為退化鎖定。

在并行NBTI測試中,當應力卸載后Id 退化恢復過程的測量是一個極大的挑戰。傳統的測試方法需要花很長的時間來測試HCI退化,通常并行對器件加載應力,之后將應力源斷開,對器件進行順序測量(圖4)。這種方法有兩個問題:首先,從斷開應力源到開始測量需要一段時間,而在這段時間內一旦應力源消失退化的恢復實際已經開始了;其次,由于順序測量器件,其測量時間也不同,那么退化恢復的程度也有差異。對于最后一個測量的器件來說,測量時其退化程度可能是第一個被測器件的一小部分。這些缺點要求采用無應力轉換的開關、可以完成多器件并行測量的測試方法。另外還要求可以通過幾點測試數據估測Vt 的退化情況,而不是像傳統方法那樣必須使用整條Id-Vg 曲線來測量Vt 退化。

NBTI測試中,退化恢復的另一個常見問題同晶體管工作時是否能達到頻繁的開關狀態有關。因為只有在晶體管關斷的條件下,NBTI退化才能開始恢復。因此,如果使用傳統的DC應力和退化手段,如果晶體管一直處于開態,將不會有恢復現象出現,這樣將會導致低估晶體管的壽命。

一種解決這些動態恢復問題的方法是采用脈沖應力取代傳統的DC應力。使用這一技術,晶體管受到脈沖應力,其工作狀態在開態和關態之間交替轉換。這樣Vt的退化就成為脈沖頻率的函數。這種測試可以提供不同應用下器件恢復性能的重要信息。例如,開關頻率與晶體管在不同功能電路的使用頻率不同。NBTI退化與頻率的對應關系可以揭示出部分電路在測試前失效的情況。

高k柵極介電材料的電荷俘獲

盡管在最先進的工藝中采用高k材料有助于解決超薄柵介質層的漏電問題,但天下沒有免費的午餐。隨之而來的是很多個必須解決的技術難題。其中之一就是暫態電荷俘獲問題。當柵極處于偏壓狀態下,會發生暫態電荷俘獲并導致Vt漂移。在測量溝道載流子遷移率時,電荷俘獲問題還會引起漏極電流降低導致測得的載流子遷移率有偏差。另外,電荷俘獲還會影響到HCI、NBTI和TDDB測試中器件參數退化的測量。這是由于大部分觀察到的退化現象是由薄膜中電荷俘獲引起的,7但想要觀察的卻是器件參數真正的退化情況。

電荷俘獲問題是暫態的;也就是說其影響與時間的相關性很強。傳統的DC方法將不會,或很大程度上不會涉及到這個問題。現在普遍采用脈沖激勵來研究暫態電荷俘獲現象。

圖5所示的是兩套不同的單脈沖電荷俘獲(SPCT)測量系統的原理圖。在每套系統中,晶體管的漏極接一定的偏壓,在將脈沖激勵加到柵極上。由柵極脈沖引起Id的變化被記錄在示波器上。圖中兩套系統的不同之處在于帶寬,圖5b中所示的系統帶寬很高,可以捕獲很快的脈沖反應(一直到數十納秒)。電荷陷阱一般對如此高速的脈沖都沒有反應。因此可以測量到將電荷俘獲現象降至最低的“凈”晶體管性能。圖6所示為分別使用長脈沖寬度(方波)和短脈沖寬度(三角波)測量SPCT的結果;在長脈沖寬度激勵的Id-Vg曲線中,磁滯現象即是由電荷俘獲造成的。在短脈沖激勵的SPCT測試中,也可以觀察到一些磁滯現象,這是由于薄膜在較短的時間里也俘獲了一部分電荷造成的。

在較短脈沖寬度情況下,電荷俘獲現象將會大大減弱,因此測得的Id比DC條件下測量值要高(圖7)。

如果將使用脈沖I-V曲線得到的數據帶入到模型中,計算所預測的溝道載流子遷移率會高一些,這更能反映這類高速開關晶體管的實際性能(即在實際使用時,晶體管受到電荷俘獲現象的影響并不是很大)。

針對不同應用范圍的晶體管,分別表征其電荷俘獲現象將會過于復雜。因此建模工程師們如果可以在設計時不考慮這一現象那將再好不過。如果可以在儀器的選擇和測試系統的搭建時,避免與DC或慢脈沖激勵相聯系的假象,那么測得的結果就已經足夠接近真實值了。這樣建立的模型可以用于操作條件的設計優化。另外,隨著沉積薄膜質量和消除電荷俘獲退化效應兩個方面不斷取得進展,工藝工程師們也需要可以表征和追蹤性能提高的測試手段。

除了在常規工作的晶體管中關注電荷俘獲現象外,還可以有意在柵極中引入應力造成電荷注入。這種現象被稱為電荷抽取。這樣做的目的是雙重的:首先,這樣可以控制注入電荷的數量;其次,可以確定界面的損壞是否是應力造成的,以及這些界面處的損壞如何影響介電層的電荷俘獲行為。當施加應力之后,可以用電荷抽取電流發現界面處是否有損壞。

可靠性測試儀器的發展趨勢

就像前文所指出的那樣,可靠性測試需要與新器件的設計和新材料的使用密切關聯。盡管HCI測試仍然是可靠性測試中非常重要的一環,但工程師們越來越關注于PMOS的NBTI測試;高k柵極晶體管的電荷俘獲現象;以及NBTI、TDDB和HCI的疊加效應,例如NBTI增強的熱載流子和TDDB增強的NBTI等。為了面對這些新挑戰,測試方法已經從DC應力激勵和DC、脈沖應力同時作用轉向性能退化中的松弛現象研究。更進一步,當前的測試儀器包含有更全面的參數用以表征器件性能,其中包括DC I-V、C-V、電荷抽取和電荷俘獲(圖8)。

這些不斷改進的測試要求推動工程師們不斷尋找合適的測試工具,這樣才能滿足高效開發器件和工藝的要求。理想的測試工具需要足夠敏感,可以捕獲所有由應力引起的性能退化的細節,也要具有足夠的靈活性,可以適用于例如應力C-V測試、電荷抽取等非傳統的WLR測試。還要求測試工具具有良好的可擴展性,這樣在每次采用新的測試方案時不需要再購進一套新測試系統。最后,測試工具還要易于使用,這樣工程師們可以將寶貴的精力放在數據分析而不是儀器的操作上。

為了滿足上述要求,一**代可靠性測試系統應該具有以下特征:

◆ 可以滿足加速測試,并不用在精度和外推器件壽命應用上過于折中的硬件和軟件系統

◆ 帶有熱卡盤的半自動或全自動探針

◆ 低漏電的操縱裝置或平行探針卡

◆ 控制儀器、探針、卡盤的驅動設備,可以進行測試初始化、展開測試和管理數據

◆ 可以在不同使用者的測試條件、新材料和不同失效機制間轉換的靈活性

◆ 可以方便提取最終器件壽命并在短期加速測試中預測器件壽命的軟件系統

不斷提高的測試規模和新材料的應用使得WLR測試比以往更為困難。這些也促進了可靠性測試和建模向上游工藝的發展——這一點在工藝的研發領域體現得更為顯著。儀器制造商正致力于使測試工具更快、更敏感、具有更高的靈活性來滿足降低測試成本縮短上市時間的要求。

傳統熱載流子注入測試和負偏壓溫度不穩定性測試

熱載流子注入(HCI)

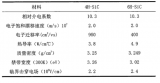

熱載流子注入(HCI)在過去幾代CMOS中一直是最重要的可靠性測試方法之一。這一過程機制如下:在MOSFET中,很高的側向電場產生熱載流子(高能電子或空穴),這些熱載流子會損壞MOS柵氧化層界面并導致器件I-V性能退化。由于溝道內的側向電場是柵極電壓(Vg)除以溝道長度,因此當溝道長度縮短時這種情況更加退化。由于溝道長度的縮減比例比Vg的縮減比例要高,增加的側向電場會產生更高能量的熱載流子,導致對柵氧化層的損壞更強烈。這種損壞是由載流子加速后的高動能造成的,并在粒子沖擊過程中產生電子/空穴對。可以看到器件的IDS(圖)、跨導和閾值電壓(Vt)都發生了退化 。退化首先降低器件的運行速度,最終器件會完全無法正常工作而失效。HCI測試是在加載電流應力條件下,檢查MOSFET晶體管性能退化的速度。通常在應力條件下測試,這樣做是為了加速器件的性能退化再外推出器件在正常使用情況下的實際壽命(正文中的圖2)。

負偏壓溫度不穩定性(NBTI)

負偏壓溫度不穩定性(NBTI)是在PMOS晶體管的一種失效模式,并且隨著晶體管柵極工作電壓的不斷降低,這一問題更為嚴重。NBTI退化的測量依據是閾值電壓隨著時間的偏移,與這種偏移相聯系的后果是運行速度變慢、漏電更多以及高溫負偏壓下驅動電流降低。NBTI測試通常是順序加載應力的過程。在某應力條件下,加載負的柵極偏壓,晶體管的其他極接地。在兩個連續應力之間,使用正常的工作條件測漏極電流(Id)。將Id或者Vt的退化作為應力加載時間的函數作圖。所有的應力偏壓和測量都是在高溫(例如,135℃)下完成。

電子發燒友App

電子發燒友App

評論