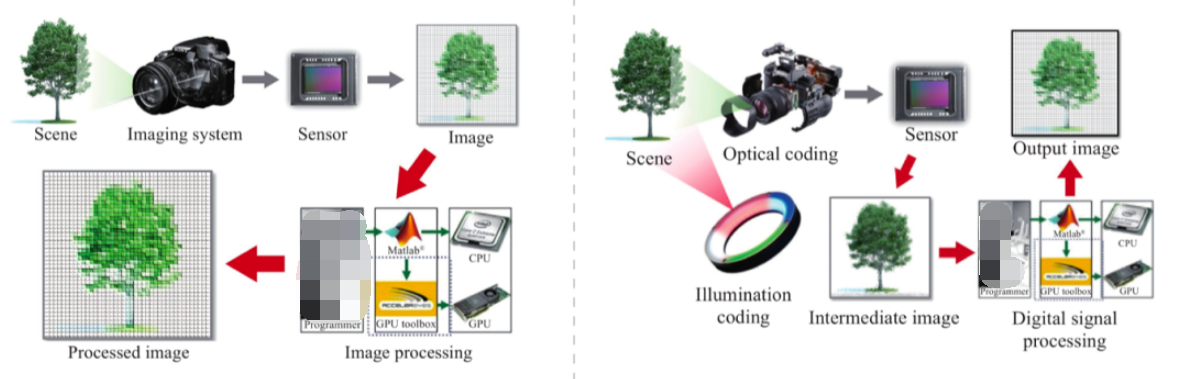

成功的路上充滿挑戰,特別是在測試測量與醫學成像應用領域尤其如此。上述領域涉及高精尖技術,因此要求采用速度最快、分辨率最高的電子技術,才能設計出獨樹一幟的未來產品。數字電子技術的發展正在推動相關領域的進步,而模擬電子技術也同樣重要。

在測試測量與醫學成像應用領域,數字電子技術通常在軟件和/或固件控制下執行多種復雜功能。

現實世界的信號(如聲和光等)是持續的,我們需采用模擬信號處理技術來應對" 真實"的環境。用模擬電子技術通過感應器進行信號采樣并帶動傳感器。

我們可將數模轉換器 (DAC) 與模數轉換器 (ADC) 等混合信號產品用于實現模擬和數字之間的連接。盡管這些器件搭建了數字與模擬間的橋梁,但我們仍將其視為模擬元件。

本文將給出測試測量與醫學成像應用領域的實例,并討論未來的發展趨勢。

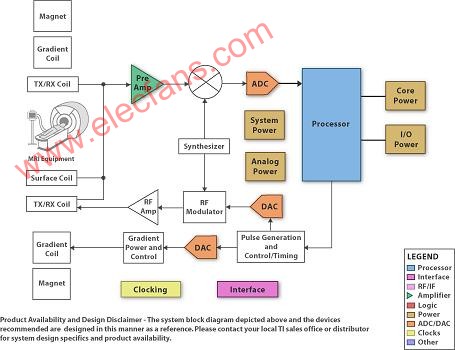

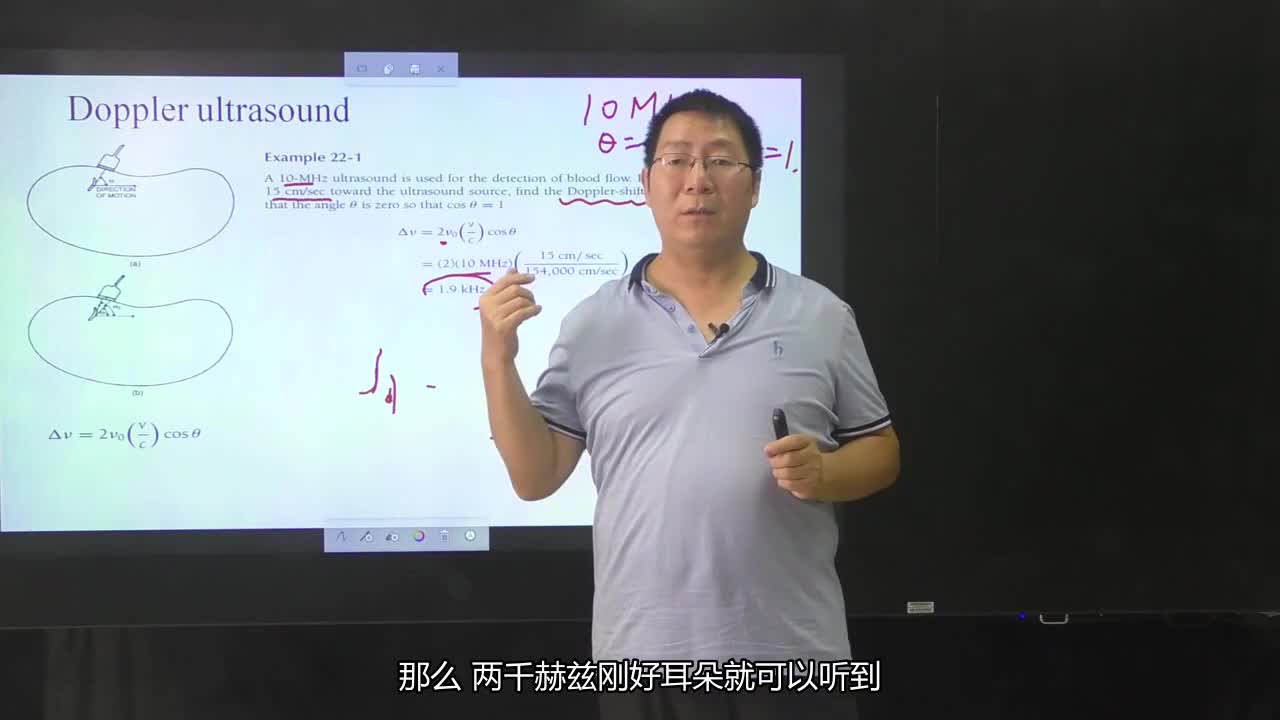

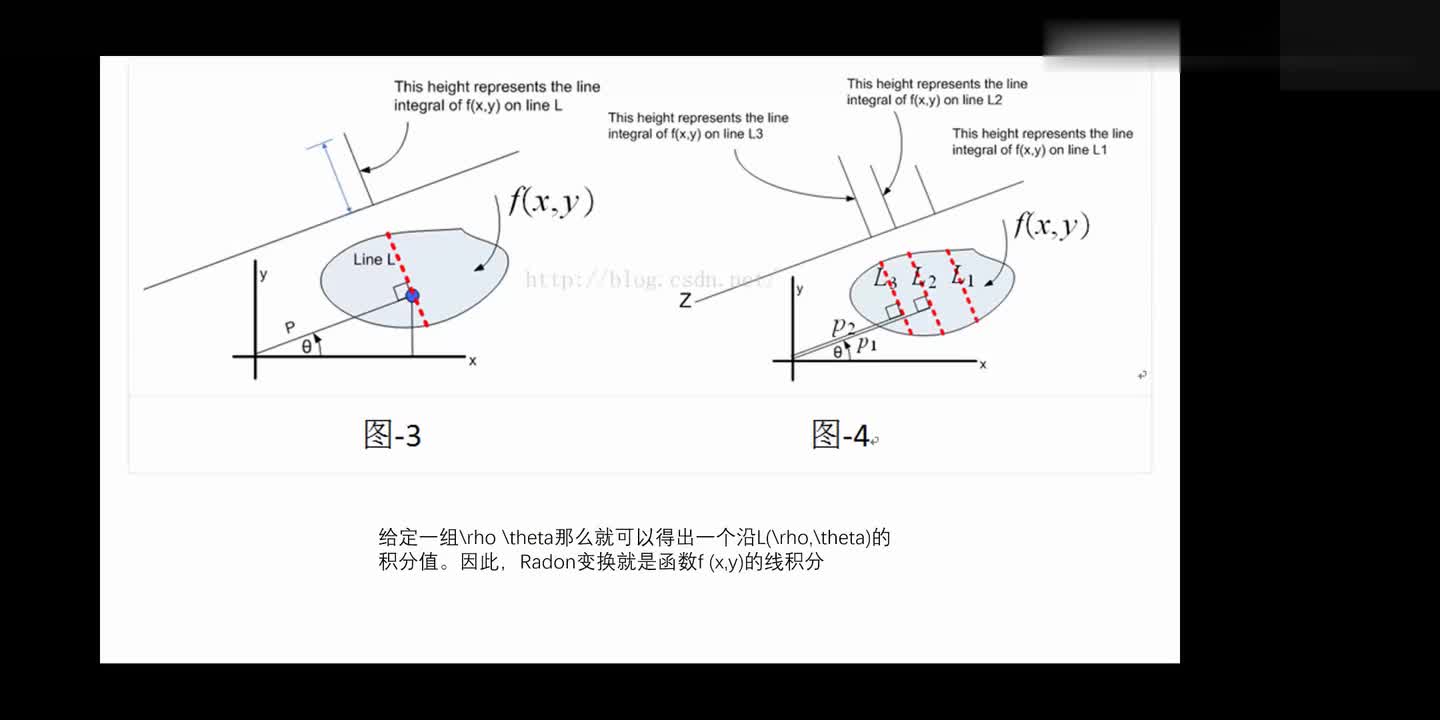

醫學成像:超聲

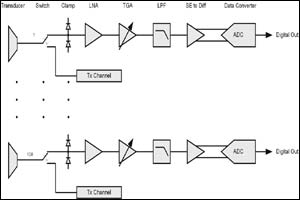

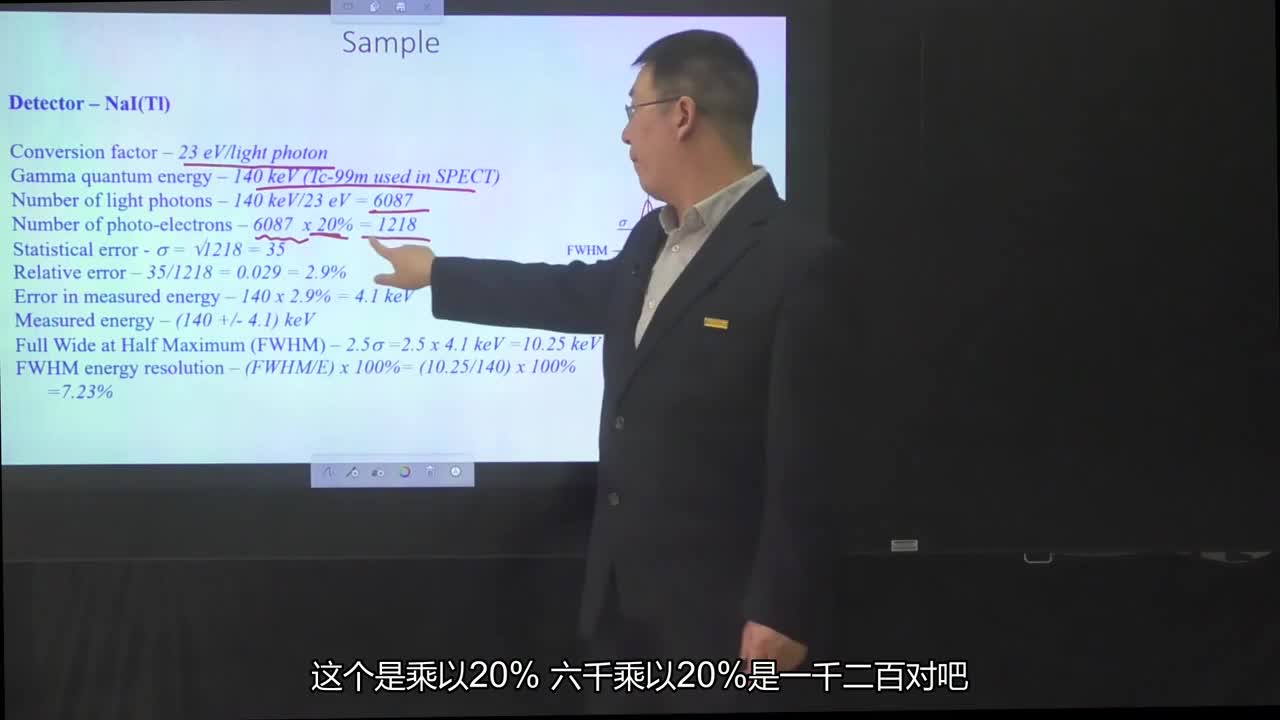

圖 1 給出了超聲通道的結構圖。通常來說,接收機與發送器共用同一變送器。發送器將向變送器發送高振幅脈沖。這時將開關設置為接收機輸入,以便檢測回聲或從病人處反 回信號。

我們提供鉗位,以確保接收通道不因發送器的高幅度信號而飽和。低噪聲放大器(LNA) 用于放大返回信號,并設置接收機的噪聲系數。

隨著信號深入人體組織,它會逐漸減弱,而返回信號則隨著時間的流逝而要求更高的增益,以保持可接受的 ADC 水平。因此,LNA 隨后還要加上時間增益放大器,該放大器編程后可補償信號的衰減。

信號的帶寬受低通濾波器 (LPF) 限制,能夠降低通道內噪聲,并達到防止信號混淆的目的。由于大多數高速的高精度 ADC 都使用差分輸入,因此需將信號從單端 (SE) 轉換為差分(Diff)。信號隨后轉換為數字形式,在數字域進行進一步處理。

在超聲中形成的波束使用多個通道來構成圖像。高性能系統中使用的通道超過 128個。新一代系統的通道數量還將繼續增加,達到 1024 個。

圖1 超聲接收機結構圖

超聲的未來趨勢

為了降低超聲設備的成本并提高性能,我們應當對其功能進行集成。通常集成的第一步就是將多種部件集成在一個封裝中,并借助先進的架構進行性能提升。因此,多通道系統不是用單個部件就可以實現的,而是通過多種部件的集成來實現,它們可使尺寸更小、功耗及成本更低、可靠性更高。

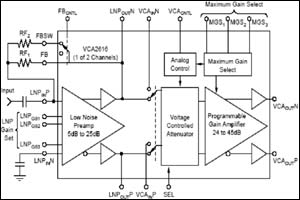

以TI的VCA2611/6(圖2)與ADS5271(圖3)為例,將多個放大器與 ADC 封裝在一起。這些元件可用于實施以上所示大多數模擬信號的調節工作。

VCA2611/6 包含兩個低噪聲前置放大器 (LNP) 以及低噪聲可變增益放大器 (VGA)。VCA2611 是 VCA2616 的升級版本,其輸入處可處理 -2.0V 負向輸入峰值,在低噪聲前置放大器之前實現較慢的廉價輸入鉗位二極管 (VCA2616 只能處理 -0.3V 的峰值)。在某些設計中,我們甚至不需要輸入鉗位。

VCA2611/6 集成了有源終端 (AT) 作為其架構的一部分。通過有源終端可實現低輸入阻抗,與傳統的分路終端 (shunt termination) 相比,改善了 4.6dB 的噪聲指數。我們也可改變終結值以適應不同的信號源。有源終端結合最大增益選擇 (MGS) 可為我們實現最佳的噪聲性能。

低噪聲前置放大器具備差分輸入與輸出功能,可設置實現 5dB、17dB、22dB 或25dB 的增益。低噪聲前置放大器的輸出可用于外部信號處理,如低通濾波。

可變增益通過模擬電壓進行控制,其增益可在 0dB 到最大增益選擇寄存器設置的增益值之間變動。用戶能夠對可變增益進行編程,使動態范圍最優化。VCA 輸入可從低噪聲前置放大器轉換到外接電路,以適應不同的應用。將低噪聲、增益以及增益范圍的可編程性相結合,能夠使 VCA2611/6 在許多應用中都成為一種功能豐富的構建塊,因為對于這些應用來說噪聲特性至關重要。

未來的 VCA2611/6 系列產品將實現更高的性能與功能,從而推動所用元件數量的減少。

圖2 VCA2611/6 功能結構圖(二選一通道)

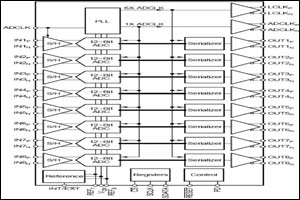

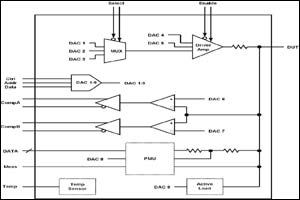

ADS5271 是一款高性能、12 位、50MSPS 的 8 通道并行模數轉換器 (ADC)。ADS5271 在 20MHz 上具備 70.5dBFS(典型)的 SNR 以及 82dBc(典型)的SFDR。

3.3V CMOS 技術實現了非常低的功耗,僅為 957mW,這為實現最高的系統集成密度留有余地。串行 LVDS(低電壓差動信令)輸出減少了接口線路數量,減小了封裝尺寸,從而進一步提高了密度。

ADS5271 可由內部或外部參照驅動,不過通過內部參照模式才能實現最佳性能與最簡系統設計。該器件采用節約面積的散熱增強型 PowerPAD、TQFP-80 封裝。

由于 ADS5271 中的通道數量已經很高,因此該系列的未來產品將致力于提高采樣率。這將通過過采樣減少模擬濾波要求。

圖3 ADS5271 功能結構圖

測試測量:引腳電子技術

我們將自動測試測量 (ATM) 設備用于測試通信系統、計算機、工業系統以及許多其他最終應用中使用的半導體器件。接受測試的器件包括模擬、數字、混合信號、邏輯以及存儲器等。為了對這些器件進行測試,我們應生成信號,激活被測試器件(DUT) 并測量響應。用于此目的的電子技術一般稱作“引腳電子技術”,而且通常包括以下功能:

以任意電平將格式化數字模型驅動到 DUT;

從 DUT 讀取數字模型,并以任意閾值水平獲取定時測量結果;

動態設置 DUT 輸出端口的負載條件;

強制電壓并測量電流,以及強制電流,測量電壓。

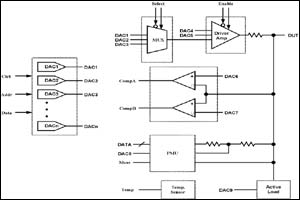

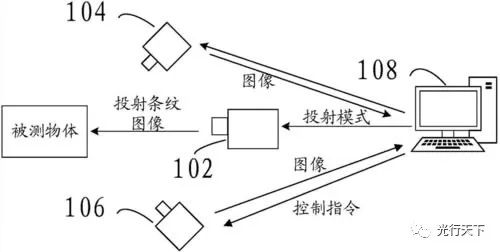

我們通過以下組件來實現上述功能,圖 4 所示為功能結構圖。

DAC

數模轉換器 (DAC) 生成模擬信號,其用于驅動被測試器件,并用于實現各種功能,如設置窗口比較器、PMU 以及有源負載水平等。12 位或 13 位的分辯率較常見,而未來產品則要求 16 位乃至更高的分辯率。由于可編程信號和電平數量較多,因此我們需要大量 DAC 來實現完整的測試解決方案。

驅動器

為了實現正確測試某些器件所需的電平,需要一個驅動器放大器。驅動器放大器必須能夠提供相關電壓并具備 DUT 所要求的輸出驅動功能。驅動器輸出必須為三態輸出,這樣它才不會干擾從 DUT 返回的信號的測量。

窗口比較器

窗口比較器用于測試是否成功通過。測試存儲器就是一個很好的使用實例,這時將數據模式寫入 DUT 并被讀出。

參數測量單元

參數測量單元可提供強制電壓、強制電流以及測量電壓與電流測量等功能。它可用于持續性測試,進行電壓、輸入電流以及漏電流測量。功能組合如下:

強制電壓/測量電流 (FVMI);

強制電流/測量電壓 (FIMV);

強制電壓/測量電壓 (FVMV);

強制電流/測量電流 (FIMI);

無強制/測量電壓 (FNMV)。

有源負載

有源負載可用于提供 DUT 負載。通過 DAC 輸入可對源極與汲極電流進行編程。

溫度傳感器

我們還包括了可提供溫度信息的溫度傳感器。

圖4 引腳電子技術功能結構圖

引腳電子技術的未來趨勢

到目前為止,引腳電子技術執行功能時需要彼此差異很大的技術--一種技術用于高速電路,而另一種技術則用于高精度直流 (DC) 電路,而且我們還要求采用不同的技術處理混合信號(如 DAC)功能。

盡管某些功能已經集成到了一起,而且目前也已經提供,但大多數解決方案都要求兩到三顆芯片才能完全實現測試頭。為了降低成本、提高功能引腳功能,并增加相同測試頭數量下的引腳數量,我們應當進行功能集成,外部組件必須最小化,而且還應充分挖掘有關架構方面的改進。圖 5 顯示了我們所建議的一種引腳電子技術器件,其在同一芯片上集成了上述所有功能。

未來,這種芯片將用于減小測試解決方案的尺寸和成本,而這也將相應降低被測試器件的制造成本,此外,由于復雜性降低,這順便也實現了提高可靠性的優勢。

圖5 集成的引腳電子技術

工藝技術實現了更高的集成度

有四種制造工藝可實現測試測量與醫學成像領域更高的集成度,它們是:CBC-10、C05、BiCom II 以及 BiCom III。

CBC-10

TI 采用 CBC-10 工藝制造 VCA2611/6,這是一種 10V 互補雙極晶體管模擬工藝,具備用于數字功能的 CMOS。

CBC 二極晶體管的特征尺寸僅為 1 _m (drawn),CMOS 電路的密度為 0.8 _m,是一種領先的工藝,為 NPN 以及 PNP 晶體管分別提供了 10GHz 和 7GHz 的截止頻率。它還具備 80V 的典型爾利電壓。此外,除了核心互補高速雙極器件之外,其還采用了模塊化方法來添加肖特基二極管、JFET 晶體管、高熱能無源器件以及亞微米 CMOS 作為可選模塊。

該工藝實現了高質量、低噪聲的 JFET 晶體管,其可實現出色的高阻抗輸入級。該工藝還具備可微調的薄膜電阻器以及高精度電容器,實現最小的寄生效應以及最佳的線性和跟蹤性能。高精度電阻器與電容器實現的線性為每伏特數 ppm。舉例來說,高精度電容器的線性比可為 5 ppm/V,電壓系數為 10 至 50ppm/V。這就能夠實現噪聲與失真性能方面的顯著提升。該工藝還為高密度 CMOS 電路提供了額外的隔離,提供了隔離構建電路的分開場所 (separate tub)。這對混合信號設計而言是至關重要的,因為這能夠最小化串擾并改善精度,以及提高模擬電路的速度。這樣,我們就實現了更高的精確度、更高的增益以及更快速的模擬電路。總而言之,CBC-10 工藝實現了數字控制、粘接邏輯以及與微控制器與 DSP 相連的接口。除了能在 ±5V 上運行高性能模擬與混合信號電路之外,CBC 還采用 0_5 V 的 CMOS 接口。

CBC-10 是一種非常快捷的模擬工藝,能夠制造類似 OPA847 的放大器,其增益帶寬乘積 (GBW) 達 3.9GHz,輸入噪聲低至 0.85nV/√Hz,轉換速率高達 950V/_s,而且失真很低,只有-105dBc(5MHz)。模擬功能很強,CMOS 數字功能也很強,二者相結合就實現了更高程度的集成功能,正如我們在 VCA2611/6 中所述。

C05

ADS5271 采用 C05 數字工藝制造——該項工藝開發于 90 年代晚期,用于制造先進的 DSP(數字信號處理器)。目前其已是一種成熟的數字工藝,其模擬功能也在ADS5271 與 ADS5500 等產品中得到了進一步充分利用。

C05 是 0.18 微米的 CMOS 工藝,它實現了高傳輸時間的晶體管。其采用先進的金屬系統來實現低結電容與晶體管周圍的寄生元素。這使其理想地適應于高速混合信號設計。

C05 工藝還具備隔離式 NMOS,有助于降低數字開關帶給敏感模擬節點的串擾,也可降低類似 ADS5271 的多通道部件中通道間的串擾。

我們采用智能架構與電路技術來充分發揮高 ft 晶體管的優勢,從而設計出市場上最快速、性能最高的 ADC。

BiCom-II

BiCom-II 工藝是 15V 互補雙極晶體管技術,其采用電介質隔離來降低晶體管中的寄生結電容。NPN 晶體管擁有 5GHz 的傳輸速率與 4GHz PNP,這就實現了快速而高性能的模擬晶體管。它能夠處理更高的電壓,這使其非常適用于要求更高電壓的引腳電子技術。

此外,BiCom-II 還包括一個高性能 5 伏亞微米數字 CMOS 工藝,能夠在芯片上實施包括數千個門極之多的邏輯功能。這種片上 CMOS 邏輯功能實施所要求的硅芯片面積更小,成本更低,比雙極邏輯的功耗更低。因此,采用 BiCom-II 工藝制造的器件將支持片上 CMOS 邏輯功能,而其門密度則比前代互補雙極工藝要高 20 倍。該工藝實現了集成在模擬塊中的完整的標準數字函數庫,并可使用標準的數字設計工具。

BiCom-II 工藝實現了多種底層工藝技術的最佳結合,非常適用于先進的引腳電子技術應用。BiCom-II 是互補雙極與 CMOS 工藝的結合,其可提供出色的 beta 版,推出了優秀的雙極晶體管爾利電壓產品,并實現了更簡單、更高性能的電路。15 伏互補雙極工藝實現了用于運算放大器中的快速晶體管,成為多種模擬功能的構建塊。CMOS 工藝提供了 5 伏模擬晶體管,實現了設計靈活性。上述因素可簡化開發,并幫助 TI 以更快的速度響應市場需求,并推出全面集成的引腳電子技術產品。

THS4271 是模擬功能的一個實例。它具備 1.4GHz 的帶寬,是第一款在保持極低噪聲 (3 nV/√Hz) 條件下實現極快轉換速率 (1000 V/_s) 的單位穩定增益運算放大器。

BiCom-III

BiCom-III 是一種 5V 硅鍺 (SiGe) 工藝,其開發用于超高速模擬集成電路,是基于硅技術 (Si) 的電介質絕緣工藝,在基礎區域添加了鍺 (Ge)。在基礎區添加鍺大大提高了載體的移動性,并實現了極快的瞬態時間。該工藝實現了真正的互補雙極 NPN 與 PNP 晶體管,傳輸頻率 (fT) 達 18GHz,最高頻率 (fmax) 達 40-60GHz。該工藝的速度比早期工藝提高了三倍。

與 BiCom-II 類似,BiCom-III 工藝流程也包括高密度亞微米 CMOS 邏輯,并具備廣泛的數字庫,可實現高性能模擬與復雜數字功能的無縫集成。

5V 超高速模擬晶體管使該工藝理想適用于測試低電壓設備(如閃存)所需的引腳電子技術。

我們在說明有關 BiCom-III 工藝的先進性能時所舉的實例就是 THS4304,其也是第一款 3GHz 單位增益穩定電壓反饋運算放大器。根據設計,其可用于采用 +5V 單電源工作的高速、高性能模擬信號處理鏈中。

THS4304 可提供 3GHz -3dB 的單位增益帶寬,830V/μs 的轉換速率,在 20MHz 上 +45dBm 的輸出三級攔截 (OIP3),2.8nV/√Hz 的輸入噪聲,以及 7.5ns 到 0.01% 的建立時間,同時靜態耗電僅為 90mW。

全面集成:片上系統

制造商能夠將高度復雜的高密度數字功能集成至模擬工藝上,或更準確地說,他們在成熟的數字工藝中開發了模擬功能,并推出了許多高性能片上系統 (SOC)。最新型的先進最高性能數字與模擬部件仍采用不同工藝進行開發,至少在不久的將來仍將保持這種狀態。

在片上集成數字與模擬功能面臨著諸多挑戰。高性能數字邏輯會產生噪聲,并降低模擬的信噪比 (SNR)。在同一 PCB(印刷電路板)上集成快速數字邏輯與模擬要求高超的工程設計技能,這甚至比芯片級集成還要困難。

先進的模擬電壓最近已成功地從 12V 降至 5V 和 3.3V,但還不能很輕松地降至當前數字核心電壓的水平。這是由于噪聲與工作電壓不成正比,而是基本保持常量。模擬工作電壓必須保持足夠高以實現良好的 SNR。較低的電壓不能提供高動態范圍模擬信號所要求的性能空間。

先進的數字工藝不包括高性能模擬組件。此外,先進模數之間在工藝特征尺寸方面也有很大差別。模擬工藝的起點是穩定的數字工藝。不管數字工藝晶體管的線性功能如何,我們都要用其實現片上模擬功能。即便如此,在工藝早期階段,我們仍要強調數字部分;模擬功能只限于不需要額外工藝步驟或修改的部分。一旦工藝成熟并成功制造了最新系列的高速邏輯產品,數字工藝設計人員就可向下一工藝節點推進,而模擬組件設計人員則致力于在該工藝上推出更高的模擬功能。開發與完善模擬組件尚需時日。高性能模擬工藝通常比基本數字工藝的投產晚好幾年。

結語

未來的競爭市場要求新工藝技術推動用于測試測量以及醫學成像設備中高性能模擬組件的集成。這將拓撲技術發展與創新設計解決方案進行了完美結合,從而可進一步降低成本與功耗要求、縮小尺寸、提高可靠性,并使未來設備更輕盈小巧。

當前的技術實現了比以前任何時候都更高的集成度,但在同一器件上實施先進數字與高級模擬功能的真正集成還有待未來的發展才能實現。一旦能夠實現真正集成,那么下一個目標就是降低成本。

- 測試測量(90355)

相關推薦

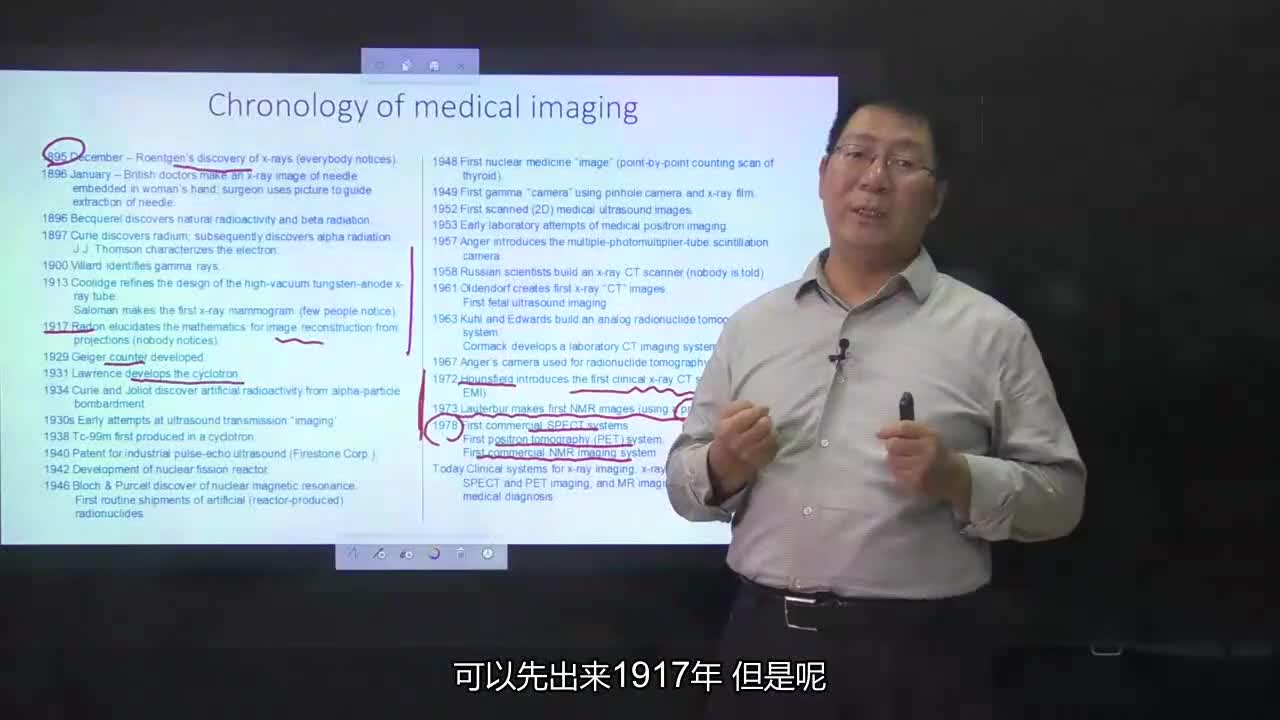

醫學成像領域的人工智能

3252

3252醫學影像分類

醫學數字成像

醫學成像中的時鐘分發系統設計簡介

模擬電路技術在數字時代面臨的挑戰有哪些?

測試測量與醫學成像領域的模擬技術趨勢

【AD新聞】中國深圳先進院在高分辨率超聲成像領域取得重要進展

不同醫學數字成像設的挑戰

不同醫學成像方法電子設計的挑戰

東莞CCD視覺測量技術有哪些有點?

恒茂創遠虛擬仿真實訓系統在醫學教育領域的發展趨勢

深圳CCD視覺檢測技術在測量時有哪些優點?

解析不同醫學數字成像方法電子設計

超聲系統的架構原理及醫學超聲芯片的模擬參數

首個開源醫療影像系統案例分享

測試測量與醫學成像領域的模擬技術趨勢

14

14飛利浦開展新型醫學成像技術PET/MR研究

1051

1051切倫科夫冷光成像的新型光學成像技術分析

710

710不同醫學成像方法電子設計存在的挑戰

443

443

醫學成像:兩高一低新風尚

1496

1496

核醫學成像設備基礎知識詳解

9320

9320光學成像與激光散斑成像技術的介紹

12

12生物醫學工程的電阻抗成像技術研究

4610

4610

醫學數字成像的挑戰及最新動態概述

879

879

什么是讓醫學成像領域被深度學習的魔力折服呢?

4600

4600醫學成像配準的詳細資料說明

15

15AI徹底改變醫學成像 2023年全球醫學影像人工智能市場將達20億美元

1875

1875人工智能和增強智能正在推動醫學成像科學的發展

607

60720秒完成全身3D掃描的醫學成像設備

2811

2811自供電的X射線檢測器有望改變醫學成像技術現狀

576

576醫學成像光譜技術突破,能夠快速診斷出肺癌

989

989高級醫學成像技術確診心臟病 只需7秒

544

544醫學超聲影像技術獲得新發展

1121

1121基于深度學習的光學成像算法綜述

10

10光學成像技術的了解與研究

3482

3482為實時醫學成像應用部署OCT

419

419計算光學成像:突破傳統光學成像極限

886

886先進等離激元技術及其在多尺度生物醫學成像中的應用

1100

1100【虹科】機器視覺為醫學成像帶來成本和臨床效益(一)

377

377

虹科案例 | 太赫茲技術用于醫學成像研究

2390

2390

紅外熱成像技術在醫學領域的應用

719

719

基于光學成像的物體三維重建技術研究

493

493

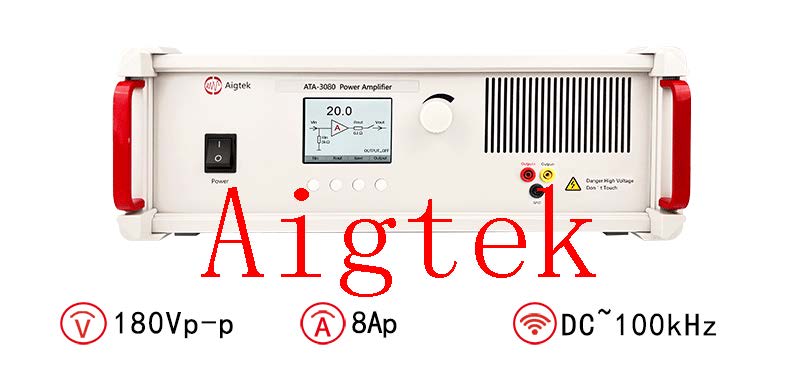

ATA-4052高壓功率放大器如何幫助醫生完成醫學成像診斷?

193

193

計算光學成像如何突破傳統光學成像極限

215

215

2023十大科技趨勢之一:計算光學成像

783

783

新技術:使用超光學器件進行熱成像

105

105安泰功率放大器在醫學領域的應用有哪些

69

69

電子發燒友App

電子發燒友App

評論