uart串口

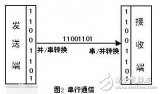

通用異步收發(fā)傳輸器(Universal Asynchronous Receiver/Transmitter),通常稱作UART,是一種異步收發(fā)傳輸器,是電腦硬件的一部分。它將要傳輸?shù)?a href="http://www.asorrir.com/soft/special/" target="_blank">資料在串行通信與并行通信之間加以轉(zhuǎn)換。作為把并行輸入信號轉(zhuǎn)成串行輸出信號的芯片,UART通常被集成于其他通訊接口的連結(jié)上。

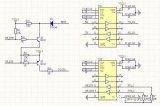

具體實物表現(xiàn)為獨立的模塊化芯片,或作為集成于微處理器中的周邊設(shè)備。一般是RS-232C規(guī)格的,與類似Maxim的MAX232之類的標準信號幅度變換芯片進行搭配,作為連接外部設(shè)備的接口。在UART上追加同步方式的序列信號變換電路的產(chǎn)品,被稱為USART(Universal Synchronous Asynchronous Receiver Transmitter)。

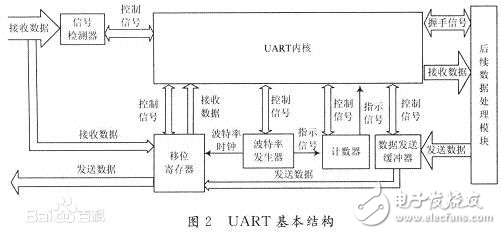

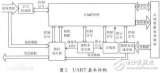

uart基本結(jié)構(gòu)

1輸出緩沖寄存器,它接收CPU從數(shù)據(jù)總線上送來的并行數(shù)據(jù),并加以保存。

uart基本結(jié)構(gòu)

2輸出移位寄存器,它接收從輸出緩沖器送來的并行數(shù)據(jù),以發(fā)送時鐘的速率把數(shù)據(jù)逐位移出,即將并行數(shù)據(jù)轉(zhuǎn)換為串行數(shù)據(jù)輸出。

3輸入移位寄存器,它以接收時鐘的速率把出現(xiàn)在串行數(shù)據(jù)輸入線上的數(shù)據(jù)逐位移入,當(dāng)數(shù)據(jù)裝滿后,并行送往輸入緩沖寄存器,即將串行數(shù)據(jù)轉(zhuǎn)換成并行數(shù)據(jù)。

4輸入緩沖寄存器,它從輸入移位寄存器中接收并行數(shù)據(jù),然后由CPU取走。

5控制寄存器,它接收CPU送來的控制字,由控制字的內(nèi)容,決定通信時的傳輸方式以及數(shù)據(jù)格式等。例如采用異步方式還是同步方式,數(shù)據(jù)字符的位數(shù),有無奇偶校驗,是奇校驗還是偶校驗,停止位的位數(shù)等參數(shù)。

6狀態(tài)寄存器。狀態(tài)寄存器中存放著接口的各種狀態(tài)信息,例如輸出緩沖區(qū)是否空,輸入字符是否準備好等。在通信過程中,當(dāng)符合某種狀態(tài)時,接口中的狀態(tài)檢測邏輯將狀態(tài)寄存器的相應(yīng)位置“1”,以便讓CPU查詢。

uart串口的調(diào)試

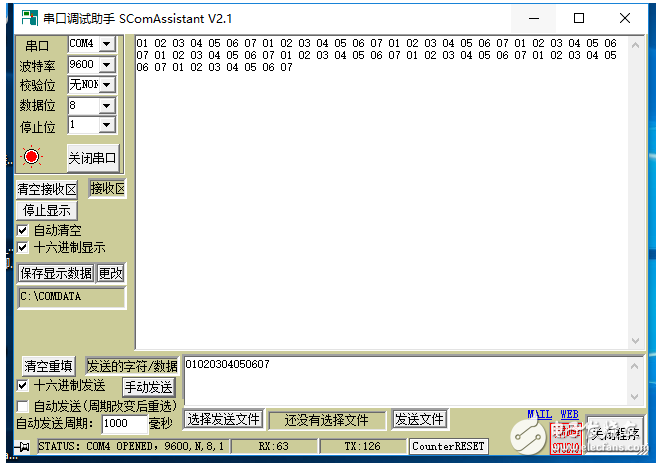

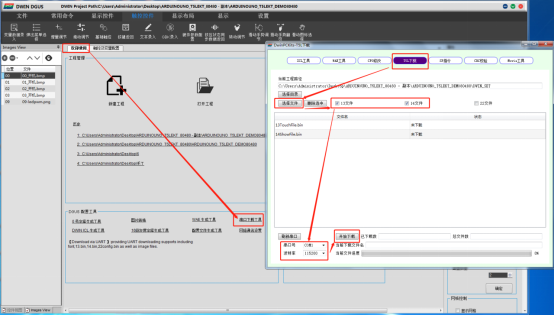

用FPGA設(shè)計了數(shù)據(jù)接收和發(fā)送模塊,F(xiàn)IFO模塊,此處FIFO調(diào)用的是Show-ahead模式,在下一篇博客中將會分析這個問題。

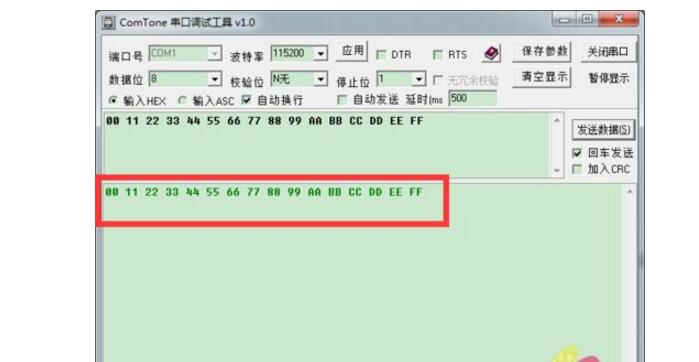

用串口調(diào)試工具發(fā)送數(shù)據(jù),數(shù)據(jù)接收模塊將接收到的串行數(shù)據(jù)轉(zhuǎn)換為并行數(shù)據(jù)(串轉(zhuǎn)并),并存入FIFO中,當(dāng)FIFO中的數(shù)據(jù)個數(shù)大于某個值的時候,讀出數(shù)據(jù),通過發(fā)送模塊將并行數(shù)據(jù)轉(zhuǎn)換為串行數(shù)據(jù)(并轉(zhuǎn)串),然后就可以在串口調(diào)試工具上看到接收到的數(shù)據(jù)。

注意的點:

1、接收數(shù)據(jù)時,接收的數(shù)據(jù)因為不確定什么時候會來,所以有可能出現(xiàn)亞穩(wěn)態(tài),因此要進行同步處理,打兩拍。

2、不論是接收還是發(fā)送數(shù)據(jù)都是從低位開始的。

3、采數(shù)據(jù)的時侯要在數(shù)據(jù)中間取值,原因下文有講。

基本概念:

波特率與比特率?

波特率:單位時間內(nèi)傳輸碼元的個數(shù)(碼元是攜帶數(shù)據(jù)信息的信號單元,有可能是1位的,也有可能是多位)

比特率:單位時間內(nèi)傳輸了多少位數(shù)據(jù)

比特率=波特率*碼元的位數(shù)

因為UART數(shù)據(jù)是一位一位傳輸?shù)模圆ㄌ芈逝c比特率在這里可以認為是等效的,不用過于糾結(jié),我們就直接理解成1s傳送了多少位數(shù)據(jù)就可以了。

這是一個很不專業(yè)的總結(jié),但是能很快理解二者關(guān)系。

常用的波特率有 9600,19200,38400等,這里用9600進行詳細講解

波特率位9600,則每一位數(shù)據(jù)的時間為 1s/9600=1000_000_000 ns/9600 =104166.67ns

因為時鐘頻率是50Mhz,因此需要104166.67ns/20ns=5208個時鐘周期。

這里需要注意的問題是我們的時間并不能整除,有誤差,因此設(shè)計的時候要在數(shù)據(jù)的中間取值,這樣就可以避免數(shù)據(jù)出錯。

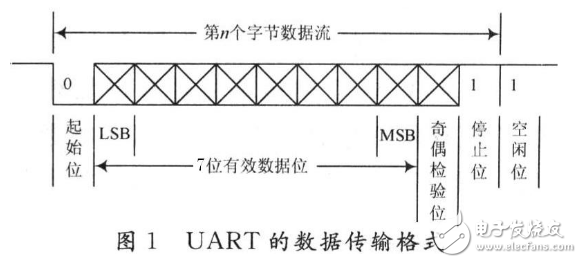

UART數(shù)據(jù)傳輸格式

數(shù)據(jù)格式由起始位、數(shù)據(jù)位(位數(shù)可以位7、8等)、奇偶校驗位(可有可無)、停止位(接收數(shù)據(jù)時可以忽略,發(fā)送數(shù)據(jù)時必須要有停止位)

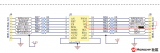

上面已經(jīng)說過每個數(shù)據(jù)的時間為5208個時鐘周期,因此需要設(shè)計一個計數(shù)器cnt_5208

接收數(shù)據(jù)時為 起始位+8位數(shù)據(jù)位,即9位數(shù),因此需要一個計數(shù)器來指示是哪一位數(shù),cnt_bit。

接收數(shù)據(jù)時怎么檢測有數(shù)據(jù)要來呢?

空閑時刻,數(shù)據(jù)線處于高電瓶,有數(shù)據(jù)來時要發(fā)送低電平,因此我們可以利用這個特性進行一個邊沿檢測,檢測到下降沿的時候就知道有數(shù)據(jù)要來了。

接收數(shù)據(jù)注意的要點有哪些?

1、亞穩(wěn)態(tài)問題:并不能確定數(shù)據(jù)什么時候來,所以為了避免出現(xiàn)亞穩(wěn)態(tài),我們需要對到來的數(shù)據(jù)進行同步化處理,就是簡單的打兩拍。

2、最好是在數(shù)據(jù)穩(wěn)定的時候采集數(shù)據(jù),所以有 clk_en =(cnt_5208 ==TIME_5208/2 -1)? 1‘b1:1’b0,這個使能信號,可以保證在數(shù)據(jù)中間時刻采值,正確率高。

發(fā)送數(shù)據(jù)時 起始位0 +8位數(shù)據(jù)位 +停止位1,同樣也需要一個計數(shù)器來指示是哪一位數(shù)。

發(fā)送數(shù)據(jù)模塊注意的要點有哪些?

發(fā)送數(shù)據(jù)模塊就是把接收到的數(shù)據(jù)一位一位發(fā)出去,這時候就要設(shè)計一個rdy信號告訴外面的模塊系統(tǒng)是否處于工作模式,這樣可以防止數(shù)據(jù)的丟失,

我們一板將要發(fā)送的數(shù)據(jù)先緩存起來,然后再一位一位發(fā)出去,這樣也避免了再發(fā)送數(shù)據(jù)的時候受其他因素影響造成信息錯誤。

還要注意數(shù)據(jù)傳送的時候都是從低位開始。這一點很重要很重要,否則發(fā)送的數(shù)據(jù)和接收到的數(shù)據(jù)就不一樣,我是深深被傷到了,浪費了好多時間,以后要細心,不能再想當(dāng)然,要遵守協(xié)議。。。。。

調(diào)試結(jié)果:當(dāng)發(fā)送超過60字節(jié)的數(shù)據(jù)時,就會接收到數(shù)據(jù),結(jié)果如下。

發(fā)送了01020304050607,即4位*14=56位數(shù),即一次發(fā)送7字節(jié)的數(shù)據(jù)。

電子發(fā)燒友App

電子發(fā)燒友App

評論