DDR4主要是針對(duì)需要高帶寬低功耗的場(chǎng)合。這些需求導(dǎo)致了DDR4芯片引入了一些新的特點(diǎn):它摒棄了上幾代內(nèi)存產(chǎn)品的SSTL電平接口,引用了新的I/O架構(gòu)POD(Pseudo Open Drain)。

2018-07-27 10:56:20 15823

15823

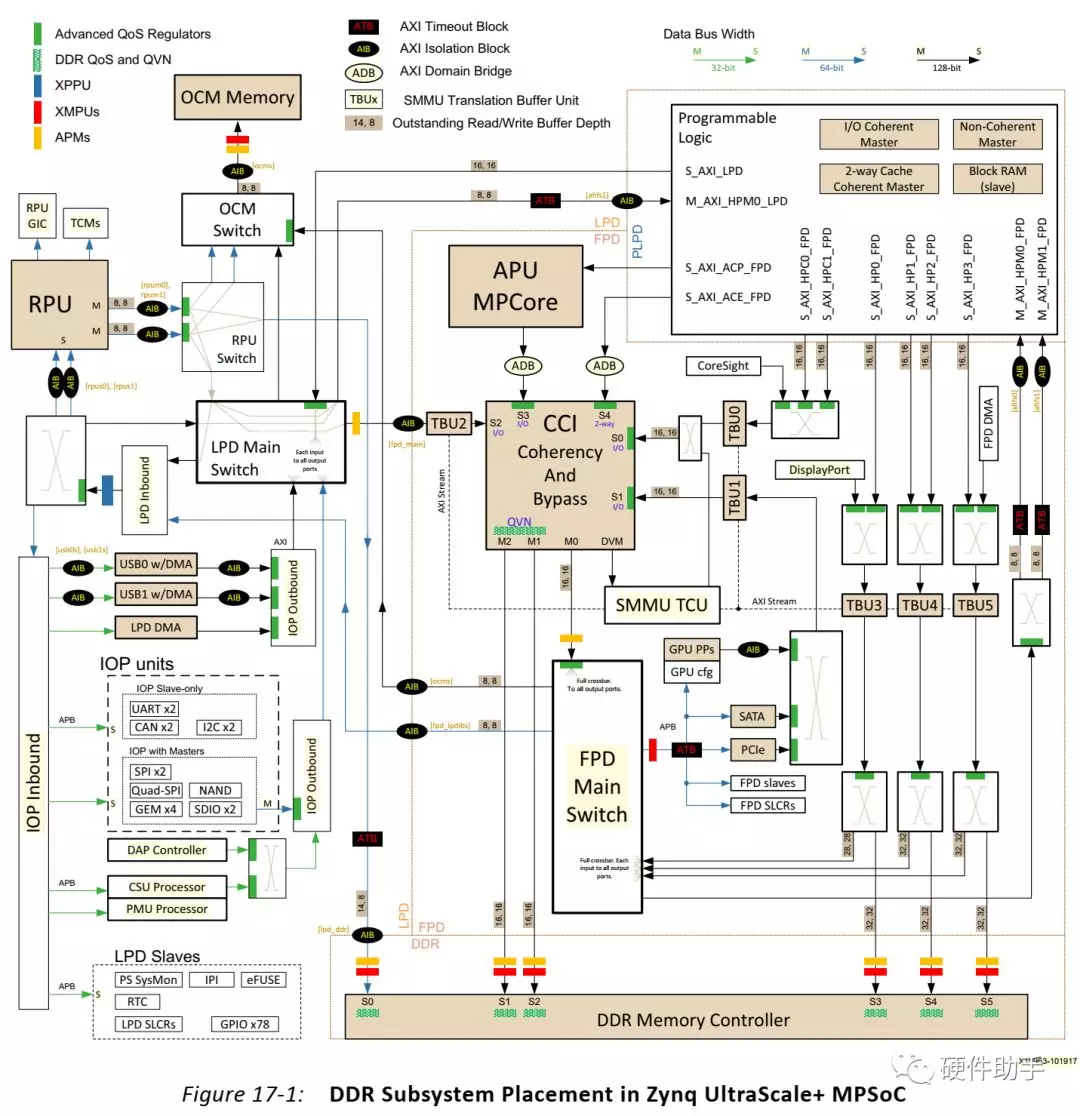

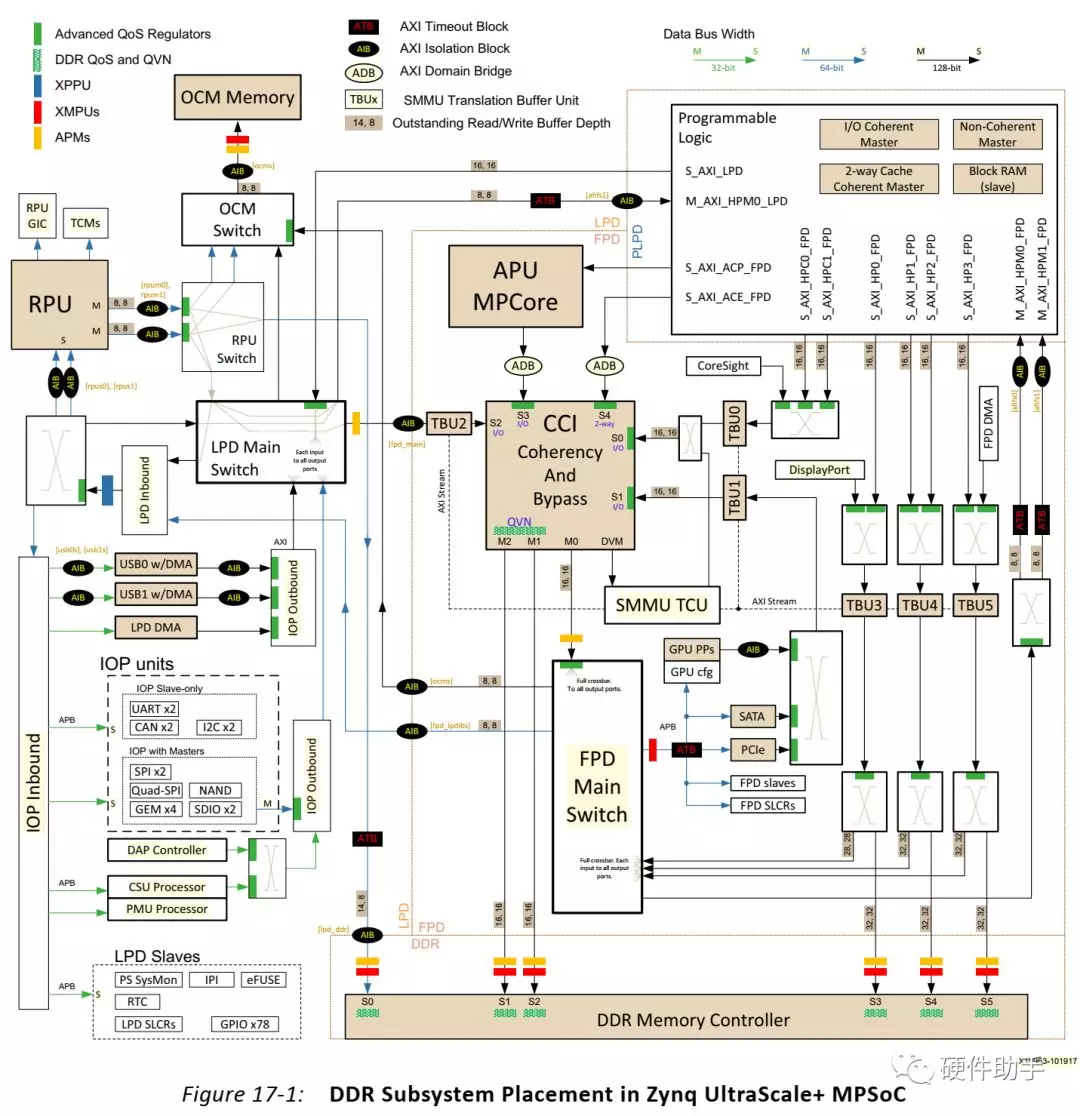

本篇主要針對(duì)Zynq UltraScale + MPSoC的DDR接口,從硬件設(shè)計(jì)的角度進(jìn)行詳細(xì)介紹,最后展示一下小編之前自己設(shè)計(jì)的基于ZU+的外掛8顆DDR4的設(shè)計(jì)。 目前比較常用的DDR

2020-12-21 14:04:36 7224

7224

DDR內(nèi)存1代已經(jīng)淡出市場(chǎng),直接學(xué)習(xí)DDR3 SDRAM感覺(jué)有點(diǎn)跳躍;如下是DDR1、DDR2以及DDR3之間的對(duì)比。

2023-04-04 17:08:47 2871

2871

相對(duì)于DDR3, DDR4首先在外表上就有一些變化,比如DDR4將內(nèi)存下部設(shè)計(jì)為中間稍微突出,邊緣變矮的形狀,在中央的高點(diǎn)和兩端的低點(diǎn)以平滑曲線過(guò)渡,這樣的設(shè)計(jì)可以保證金手指和內(nèi)存插槽有足夠的接觸面

2023-09-19 14:49:44 1485

1485

DDR5已經(jīng)開(kāi)始商用,但是有的產(chǎn)品還才開(kāi)始使用DDR4。本文分享一些DDR4的測(cè)試內(nèi)容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以達(dá)到 3200Mb/s,這樣高速的信號(hào),對(duì)信號(hào)完整性的要求就更加嚴(yán)格,JESD79‐4 規(guī)范也對(duì) DDR4 信號(hào)的測(cè)量提出了一些要求。

2024-01-08 09:18:24 464

464

DDR4 SDRAM的尋址方式有哪些?

2021-10-27 06:50:24

DDR4 DESIGNDDR4 DESIGNDDR4 DESIGN拿走拿走!

2015-04-24 18:06:37

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之處?

2021-03-12 06:22:08

DDR4 SDRAM結(jié)構(gòu)和尋址DDR4 SDRAM的封裝和尋址新的改變功能快捷鍵合理的創(chuàng)建標(biāo)題,有助于目錄的生成如何改變文本的樣式插入鏈接與圖片如何插入一段漂亮的代碼片生成一個(gè)適合你的列表創(chuàng)建一個(gè)

2021-07-29 06:58:22

(UG583)“UltraScale架構(gòu)PCB設(shè)計(jì)用戶指南”的V1.10表示(通常)DDR4接口信號(hào)reset_n不需要滿足適用于地址/命令/控制組中其他信號(hào)的偏移約束。但是,在專門引用DDR4

2020-08-27 17:10:06

DDR4就一定比DDR3好嗎?

2021-06-18 06:22:29

DDR4的工作原理以及尋址方式DDR4是什么?DDR4全稱,DDR4-DRAM,與其他DDRDRAM一樣,是當(dāng)前電子系統(tǒng)架構(gòu)中使用最為廣泛的的RAM存儲(chǔ)器。這句話可以分解出3個(gè)關(guān)鍵字:存儲(chǔ)器

2021-11-11 07:13:53

DDR4相比DDR3的相關(guān)變更點(diǎn)相比DDR3,DDR4存在諸多變更點(diǎn),其中與硬件設(shè)計(jì)直接相關(guān)的變更點(diǎn)主要有:?增加Vpp電源;?VREFDQ刪除;?CMD、ADD、CTRL命令的端接變更為POD模式

2021-11-12 08:07:07

://blog.csdn.net/qq_42682826/article/details/102970701DDR4相比DDR3的相關(guān)變更點(diǎn)相比DDR3,DDR4存在諸多變更點(diǎn),其中與硬件設(shè)計(jì)直接相關(guān)

2019-11-12 12:40:17

還未接觸過(guò)DDR4,在LAYOUT顆粒設(shè)計(jì)中,布局布線上DDR3與DDR4有沒(méi)有區(qū)別?有哪些區(qū)別?

2019-03-07 10:11:39

DDR5和DDR4相比有什么優(yōu)勢(shì)?

2021-06-18 08:19:59

DDR內(nèi)存格式發(fā)展歷程(DDR~DDR4) 一、DDR DDR=Double Data Rate雙倍速內(nèi)存。嚴(yán)格的說(shuō)DDR應(yīng)該叫DDR SDRAM,人們習(xí)慣稱為DDR,部分初學(xué)者也常看到DDR

2011-02-27 16:47:17

UltraScale DSP48 Slice架構(gòu)的優(yōu)勢(shì)是什么?UltraScale內(nèi)存架構(gòu)的優(yōu)勢(shì)是什么?

2021-05-24 06:34:00

MT40A512M16LY-075E:B MT40A1G8SA-075:EMT29F64G08CBABAWP:BMT40A256M16GE-083E IT:BMT40A512M8RH-083E:B 鎂光DDR4 時(shí)時(shí)發(fā)集團(tuán)亞洲有限公司 QQ:535553245

2019-02-18 10:51:21

支持Xilinx FPGA中的32位 DDR4 SDRAM

2020-12-29 06:30:15

嗨,我正在嘗試在Kintex UltraScale(KCU105)中實(shí)現(xiàn)DDR4內(nèi)存,但是(DDR4 SDRAM(MIG))中的特定部分不可用。部分是:MT401G16HBA-083E:我應(yīng)該為實(shí)現(xiàn)這個(gè)內(nèi)存做什么。?注意:我正在使用VIVADO 2016.1謝謝Luis。

2020-04-26 13:58:08

8.2 TeraMAC的DSP計(jì)算性能。 o 16.3 Gb/s的背板收發(fā)器,最低速度級(jí)為12.5Gb/s。 o 和支持DDR4的Kintex-7相比,存儲(chǔ)器帶寬增加2倍。 5. Virtex

2013-12-17 11:18:00

東莞專業(yè)收購(gòu)DDR4東莞長(zhǎng)期高價(jià)回收DDR4,專業(yè)收購(gòu)DDR4,深圳帝歐電子長(zhǎng)期現(xiàn)金高價(jià)回收DDR4。帝歐電子趙生 ***,QQ:764029970//1816233102,mail

2021-05-08 17:42:19

和100系列主板,DDR4開(kāi)始真正走向大眾,也標(biāo)志著DDR4時(shí)代的到來(lái)。DDR4 SDRAM與DDR3相比,DDR4的工作電壓從1.5V降到1.2V和1.05V(DDR4L),這意味著功耗更低,發(fā)熱量更小

2022-10-26 16:37:40

密不可分,它們也是DDR4區(qū)別于DDR3的主要技術(shù)突破。POD電平的全稱是Pseudo Open-Drain 偽漏極開(kāi)路,其與DDR3對(duì)比簡(jiǎn)單的示例電路如下圖二所示。圖二 POD示意電路從中可以看到

2022-12-16 17:01:46

仍不知道DDR3和DDR4這兩種規(guī)格的區(qū)別,以至于買回來(lái)的硬件并不兼容。下面和宏旺半導(dǎo)體一起來(lái)看一下DDR3和DDR4到底有哪些差別。DDR3是一種計(jì)算機(jī)內(nèi)存規(guī)格,它屬于SDRAM家族的內(nèi)存產(chǎn)品,提供

2019-07-25 14:08:13

(Self-Refresh Temperature)等兩種功能,讓存儲(chǔ)器在休眠時(shí)也能夠隨著溫度變化去控制對(duì)存儲(chǔ)器顆粒的充電頻率,以確保系統(tǒng)資料的完整性。DDR4 SDRAM (Double Data Rate Fourth

2019-08-01 10:17:46

佛山回收DDR4高價(jià)回收DDR4,佛山專業(yè)收購(gòu)DDR4,深圳帝歐電子長(zhǎng)期現(xiàn)金高價(jià)回收DDR4。帝歐電子趙生 ***,QQ:764029970//1816233102,mail

2021-07-15 19:36:21

佛山回收DDR4高價(jià)回收DDR4,佛山專業(yè)收購(gòu)DDR4,深圳帝歐電子長(zhǎng)期現(xiàn)金高價(jià)回收DDR4。帝歐電子趙生 ***,QQ:764029970//1816233102,mail

2021-12-27 19:25:08

FPGAXCKU060-FFVA1156-2-I架構(gòu),支持PCIE Gen3 x8模式的高速信號(hào)處理板卡,搭配兩路40G QSFP+接口,兩組64-bit DDR4,每組容量8Gbyte,可穩(wěn)定運(yùn)行在2400MT

2022-07-11 11:35:54

NXP IMX8M Mini DDR4 校準(zhǔn)

2023-04-20 07:36:55

嗨,我是jongbum。目前,MIG UltraScale DDR4支持最高2級(jí)。https://forums.xilinx.com/t5/Memory-Interfaces

2020-04-22 08:36:21

的電路板布局是否正確,并驗(yàn)證 DDR 接口是否工作正常。 建議您參考 (PG150) 基于UltraScale 架構(gòu)的 FPGA 內(nèi)存 IP 產(chǎn)品指南,以獲得關(guān)于 DDR4 示例設(shè)計(jì)的更多信息,以及

2021-01-07 16:02:09

嗨,我正在尋找一款價(jià)格合理的Zynq Ultrascale +主板,其中DDR4接口連接到PL。我想使用一個(gè)軟核內(nèi)存控制器。問(wèn)候,Mosfa

2019-10-17 08:45:37

型號(hào) UD408G5S1AF的一款8Gb 32位 DDR4 SDRAM,是一款支持使用在英特爾Arria 10 SoC FPGA以及Kintex Ultrascale FPGA中的存儲(chǔ)器。32位 DDR4

2020-09-23 10:59:56

本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2021-04-20 06:30:52

DDR,DDR2,DDR3,DDR4,LPDDR區(qū)別文所有權(quán)歸作者Aircity所有1什么是DDRDDR是Double Data Rate的縮寫(xiě),即“雙比特翻轉(zhuǎn)”。DDR是一種技術(shù),中國(guó)大陸工程師

2021-09-14 09:04:30

深圳專業(yè)收購(gòu)DDR4深圳長(zhǎng)期高價(jià)回收DDR4,專業(yè)收購(gòu)DDR4,深圳帝歐電子長(zhǎng)期現(xiàn)金高價(jià)回收DDR4。帝歐電子趙生 ***,QQ:764029970//1816233102,mail

2021-01-30 17:36:35

回收DDR4,收購(gòu)DDR4,24h開(kāi)心財(cái)富熱線:趙生--135-3012-2202QQ-8798-21252 帝歐電子長(zhǎng)期專業(yè)高價(jià)回收f(shuō)lash, 回收DDR,回收手機(jī)字庫(kù)。回收全新flash,回收

2021-09-08 14:59:58

本帖最后由 dealicdz 于 2021-3-30 15:41 編輯

蘇州專業(yè)收購(gòu)DDR4曉色又侵窗紙。窗外雞聲初起。蘇州長(zhǎng)期高價(jià)回收DDR4,專業(yè)收購(gòu)DDR4,深圳帝歐電子長(zhǎng)期現(xiàn)金高價(jià)回收

2021-03-17 17:59:10

使用DDR4作為外接存儲(chǔ)單元時(shí),蜂鳥(niǎo)e203的訪問(wèn)地址為0x40000000,但是經(jīng)過(guò)vivado的Block design后使用DDR4,在板子上跑測(cè)試DDR4讀寫(xiě)程序,報(bào)store訪問(wèn)異常

2023-08-11 06:17:58

DDR4和DDR3的區(qū)別在哪里?DDR4內(nèi)存與DDR3內(nèi)存相比,有哪些優(yōu)勢(shì)呢?

2021-06-18 08:58:23

PH1A100是否支持DDR3,DDR4

2023-08-11 06:47:32

適用于Xilinx Virtex-7 FPGA開(kāi)發(fā)板的32位DDR4 SDRAM

2020-12-30 07:39:14

本文將介紹DDR SDRAM的一些概念和難點(diǎn),主要結(jié)合上一篇SDRAM的介紹加以對(duì)比。同時(shí)著重講解主流DDRII的技術(shù)。最后結(jié)合硬件設(shè)計(jì)提出一些參考。

DDR SDRAM全稱為Double Dat

2010-08-30 16:26:16 119

119 什么是DDR SDRAM內(nèi)存

DDR是一種繼SDRAM后產(chǎn)生的內(nèi)存技術(shù),DDR,英文原意為“DoubleDataRate”,顧名思義,就是雙數(shù)據(jù)傳輸模式。之所以稱其為“雙”,也

2009-12-17 11:15:53 1646

1646 什么是DDR2 SDRAM

DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設(shè)備工程聯(lián)合委員會(huì))進(jìn)行開(kāi)發(fā)的新生代內(nèi)存技

2009-12-17 11:17:59 623

623 DDR SDRAM內(nèi)存

DDR SDRAM是Double Dat

2009-12-17 16:20:33 684

684 DDR4,什么是DDR4

DDR 又稱雙倍速率SDRAM Dual Date Rate SDRSM DDR SDRAM 是一種高速CMOS動(dòng)態(tài)隨即訪問(wèn)的內(nèi)存美國(guó)JEDEC 的固態(tài)技術(shù)協(xié)會(huì)于2000 年6 月公

2010-03-24 16:08:39 3146

3146 使用功能強(qiáng)大的FPGA來(lái)實(shí)現(xiàn)一種DDR2 SDRAM存儲(chǔ)器的用戶接口。該用戶接口是基于XILINX公司出產(chǎn)的DDR2 SDRAM的存儲(chǔ)控制器,由于該公司出產(chǎn)的這種存儲(chǔ)控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 237

237 DDR_SDRAM介紹和時(shí)序圖,DDR_SDRAM介紹和時(shí)序圖

2016-02-23 11:58:38 6

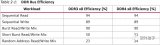

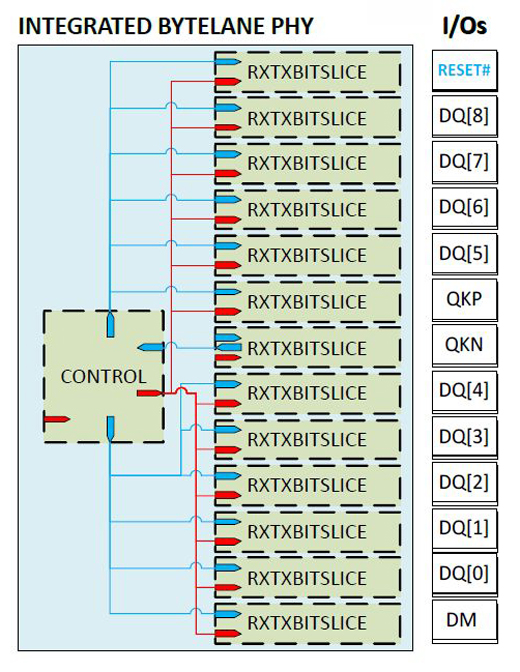

6 本內(nèi)容主要分析了基于FPGA的系統(tǒng)需求,賽靈思UltraScale FPGA DDR4和其他并行接口分析以及針對(duì)高性能高度靈活方案的PHY解決方案介紹。

2016-08-03 19:37:24 190

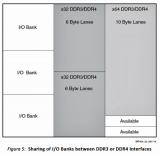

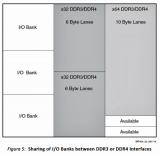

190 UltraScale架構(gòu)PCB設(shè)計(jì)用戶指導(dǎo)手冊(cè)(UG583)會(huì)給你提供很多不同的設(shè)計(jì)建議,頁(yè)數(shù)多達(dá)122頁(yè)。當(dāng)然不僅僅局限于存儲(chǔ)器的連接設(shè)計(jì),我發(fā)現(xiàn)對(duì)于DDR3與DDR4 SDRAM的連接設(shè)計(jì)也特別的有意思

2017-02-08 10:04:09 974

974

? 和 ?Xilinx Ehab Mohsen? 聊到了將 ?DDR4? 與 ?Xilinx UltraScale? FPGA? 相結(jié)合可實(shí)現(xiàn)的驚人性能優(yōu)勢(shì)和功能。 立即觀看在線座談 ??

2017-02-09 06:18:33 470

470 。 DDR4的I/O架構(gòu)稱為PSOD(Pseudo Open Drain),這個(gè)新的設(shè)計(jì),將會(huì)帶來(lái)接收端功耗的變化,以及Vref電平的差異。接下來(lái)的將會(huì)討論P(yáng)SOD輸出和上一代DDR3標(biāo)準(zhǔn)的差異。 POD

2017-10-13 20:13:18 10

10 DDR4提供比DDR3/ DDR2更低的供電電壓1.2V以及更高的帶寬,DDR4的傳輸速率目前可達(dá)2133~3200MT/s。DDR4 新增了4 個(gè)Bank Group 數(shù)據(jù)組的設(shè)計(jì),各個(gè)Bank

2017-11-07 10:48:51 52790

52790

雖然新一代電腦/智能手機(jī)用上了DDR4內(nèi)存,但以往的產(chǎn)品大多還是用的DDR3內(nèi)存,因此DDR3依舊是主流,DDR4今后將逐漸取代DDR3,成為新的主流,下面我們?cè)賮?lái)看看DDR4和DDR3內(nèi)存都有哪些區(qū)別。相比上一代DDR3,新一代DDR4內(nèi)存主要有以下幾項(xiàng)核心改變:

2017-11-08 15:42:23 30896

30896 DDR3 SDRAM(Double Data Rate Three SDRAM):為雙信道三次同步動(dòng)態(tài)隨機(jī)存取內(nèi)存。

DDR4 SDRAM(Double Data Rate Fourth

2017-11-17 13:15:49 25152

25152 如果你正在為你的下一個(gè)設(shè)計(jì)項(xiàng)目考慮DDR4 SDRAM,這里有一篇全新的白皮書(shū),你應(yīng)該研讀一番,題目叫做“UItraScale架構(gòu)FPGA的高性能低功耗內(nèi)存接口”(WP454)。很多下一代的系統(tǒng)將會(huì)

2017-11-18 08:16:10 833

833

DRAM (動(dòng)態(tài)隨機(jī)訪問(wèn)存儲(chǔ)器)對(duì)設(shè)計(jì)人員特別具有吸引力,因?yàn)樗峁┝藦V泛的性能,用于各種計(jì)算機(jī)和嵌入式系統(tǒng)的存儲(chǔ)系統(tǒng)設(shè)計(jì)中。本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 91644

91644 本文主要介紹了DDR4封裝規(guī)格.

2018-06-26 08:00:00 56

56 本文介紹了DDR4技術(shù)的特點(diǎn),并簡(jiǎn)單介紹了ANSYS工具用來(lái)仿真DDR4的過(guò)程。文章中主要介紹的對(duì)象為DDR4 3200MHz內(nèi)存,因?yàn)橛布O客對(duì)DDR4性能的不斷深挖,目前已經(jīng)有接近5000MHz的量產(chǎn)內(nèi)存。

2018-10-14 10:37:28 23341

23341 在安捷倫最新的測(cè)試解決方案之一Infinium 90000X系列示波器上驗(yàn)證,UltraScale FPGA上運(yùn)行的2400 Mb / s DDR4內(nèi)存接口設(shè)計(jì)具有出色的信號(hào)質(zhì)量和JEDEC兼容性。

2018-11-30 06:01:00 6710

6710 Xilinx推出業(yè)界首款面向All Programmable UltraScale?器件的高性能DDR4內(nèi)存解決方案,每秒數(shù)據(jù)速率高達(dá)2400 Mb.UltraScale器件采用ASIC級(jí)架構(gòu)

2018-11-30 05:33:00 3633

3633 該視頻重點(diǎn)介紹了UltraScale +產(chǎn)品系列的第一個(gè)成員Zynq?UltraScale+?MPSoC,并展示了使用可編程邏輯中的DDR4 SDRAM IP的存儲(chǔ)器接口系統(tǒng)的穩(wěn)健性。

2018-11-29 06:36:00 3044

3044 、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、DDR5 SDRAM、LPDDR、GDDR。

2018-12-19 08:00:00 76

76 DDR2 設(shè)備概述:DDR2 SDRAM接口是源同步、支持雙速率傳輸。比如DDR SDRAM ,使用SSTL 1.8V/IO電氣標(biāo)準(zhǔn),該電氣標(biāo)準(zhǔn)具有較低的功耗。與TSOP比起來(lái),DDR2 SDRAM的FBGA封裝尺寸小得多。

2019-06-22 10:05:01 1793

1793

DDR5相比DDR4有什么新特性?

2020-01-10 14:21:04 10082

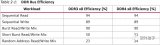

10082 Xilinx 提供了UltraScaleFPGA器件的高性能DDR4內(nèi)存解決方案,每秒數(shù)據(jù)速率高達(dá)2400 Mb。UltraScale器件采用ASIC級(jí)架構(gòu),可支持大量I/O和超大存儲(chǔ)帶寬,并能夠

2020-05-28 15:00:57 3996

3996 SDRAM從發(fā)展至今歷經(jīng)了五代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代DDR4 SDRAM,SDRAM有一個(gè)同步

2020-07-24 14:25:27 719

719 本篇主要針對(duì)Zynq UltraScale + MPSoC的DDR接口,從硬件設(shè)計(jì)的角度進(jìn)行詳細(xì)介紹,最后展示一下小編之前自己設(shè)計(jì)的基于ZU+的外掛8顆DDR4的設(shè)計(jì)。

2020-12-28 08:00:00 0

0 本篇主要針對(duì)Zynq UltraScale + MPSoC的DDR接口,從硬件設(shè)計(jì)的角度進(jìn)行詳細(xì)介紹,最后展示一下小編之前自己設(shè)計(jì)的基于ZU+的外掛8顆DDR4的設(shè)計(jì)。 目前比較常用的DDR

2021-09-16 10:17:02 4789

4789

DDR4的工作原理以及尋址方式DDR4是什么?DDR4全稱,DDR4-DRAM,與其他DDRDRAM一樣,是當(dāng)前電子系統(tǒng)架構(gòu)中使用最為廣泛的的RAM存儲(chǔ)器。這句話可以分解出3個(gè)關(guān)鍵字:存儲(chǔ)器

2021-11-06 13:51:01 143

143 DDR,

DDR2,

DDR3,

DDR4,LPDDR區(qū)別作者:AirCity

[email protected] 本文所有權(quán)歸作者Aircity所有1 什么是DDRDDR

2021-11-10 09:51:03 154

154 在Versal新一代ACAP器件上,除了延續(xù)之前Ultrascale/Ultrascale+系列器件上已有的DDR4 IP之外,還配置了最新的DDR4/LPDDR4 硬核控制器 (NOC IP

2022-07-06 10:42:17 3524

3524 本文檔定義了DDR4 SDRAM規(guī)范,包括特性、功能、交流和直流特性、封裝和球/信號(hào)分配。本標(biāo)準(zhǔn)旨在定義符合JEDEC 2 Gb的最低要求x4、x8和x16 DDR4 SDRAM設(shè)備通過(guò)16 Gb

2022-11-29 10:00:17 20

20 8Gb DDR4 SDRAM B裸片組織為128Mbit x 4 I/O x16banks或64Mbit x8 I/O x 16banks設(shè)備。此同步設(shè)備實(shí)現(xiàn)高達(dá)2666Mb/sec的高速雙數(shù)

2022-12-05 11:54:24 11

11 DDR3

SDRAM使用雙倍數(shù)據(jù)速率

架構(gòu)來(lái)實(shí)現(xiàn)高速操作。雙倍數(shù)據(jù)速率結(jié)構(gòu)是一種8n預(yù)取

架構(gòu),其

接口經(jīng)過(guò)設(shè)計(jì),可在I/O引腳上每個(gè)時(shí)鐘周期傳輸兩個(gè)數(shù)據(jù)字。

DDR3

SDRAM的單個(gè)讀或?qū)懖僮饔行У匕?/div>

2023-02-06 10:12:00 3

3 DDR4和DDR3內(nèi)存都有哪些區(qū)別? 隨著計(jì)算機(jī)的日益發(fā)展,內(nèi)存也越來(lái)越重要。DDR3和DDR4是兩種用于計(jì)算機(jī)內(nèi)存的標(biāo)準(zhǔn)。隨著DDR4內(nèi)存的逐漸普及,更多的人開(kāi)始對(duì)兩者有了更多的關(guān)注。 DDR

2023-10-30 09:22:00 3905

3905 PCB的DDR4布線指南和PCB的架構(gòu)改進(jìn)

2023-12-07 15:15:58 761

761 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論