1

設(shè)計(jì)簡(jiǎn)介

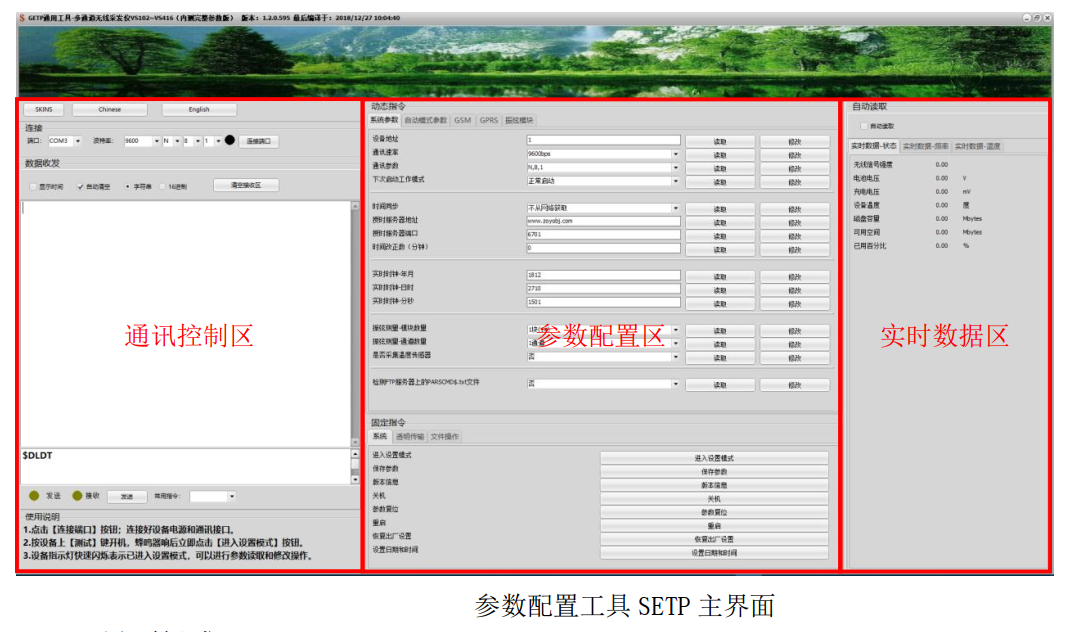

本次的demo設(shè)計(jì)將通過上位機(jī)的設(shè)置界面,完成AD9250的參數(shù)設(shè)置。界面通過USB2.0控制器Cy68013完成數(shù)據(jù)AD9250的配置工作。

AD9250的參數(shù)配置是通過SPI的接口完成,SPI的接口由3個(gè)IO組成:

the serial clock pin SCLK:

n SCLK的為時(shí)鐘IO,其最高的工作頻率為25MHz,并接50K的下拉電阻。

the serial data input/output pin SDIO。

n SDIO為數(shù)據(jù)傳輸?shù)碾p向IO口,在AD9250中,SDIO的初始狀態(tài)為輸入IO,在獲取讀寫命令后,IO的輸入輸出方向?qū)?huì)發(fā)生相應(yīng)的變化。

the chip select bar pin CSB。

n 片選信號(hào),低電平有效。

根據(jù)AD9250的配置參數(shù)的特性,配置的參數(shù)可以分為4個(gè)部分:

Configurationregister

Transfer register

Program register

JESD204B link setup parameter

2

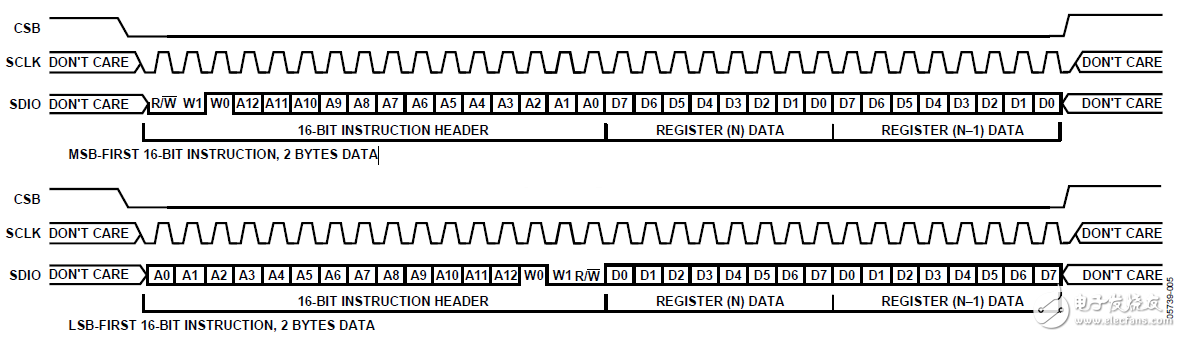

SPI接口時(shí)序

SPI的時(shí)序如圖所示,數(shù)據(jù)在CSB拉低時(shí)有效,并在SLCK的第一個(gè)上升沿開始SPI的數(shù)據(jù)傳輸。

數(shù)據(jù)在SCLK的下降沿進(jìn)行更新,在SCLK的上升沿進(jìn)行數(shù)據(jù)的讀取。

數(shù)據(jù)的具體格式為:

數(shù)據(jù)幀的第1bit的為讀寫控制信號(hào),Read為1,wirte為0.

數(shù)據(jù)幀的第2bit和第3bit為地址信號(hào)

n W1W0 = 11:數(shù)據(jù)幀的長(zhǎng)度不限,在CSB為低時(shí)將一直傳輸數(shù)據(jù)

n W1W0 = 10:數(shù)字幀的數(shù)據(jù)長(zhǎng)度為3

n W1W0 = 01:數(shù)字幀的數(shù)據(jù)長(zhǎng)度為2

n W1W0 = 00:數(shù)字幀的數(shù)據(jù)長(zhǎng)度為1

數(shù)據(jù)幀的第4-16bit:訪問AD的內(nèi)存地址。有效空間為0-255。

后續(xù)為寫入或者讀出的AD的控制數(shù)據(jù)。

3

參數(shù)配置

參數(shù)可以根據(jù)其功能的不同,分為4個(gè)部分進(jìn)行介紹:

Configuration register

n Global SPI config:LSB first 、Soft reset

Transfer register

n Transfer settings:該位置1表示將

Program register

n

JESD204B link setup parameter

1. Disable lanes before changingconfiguration

2. Select quick configurationoption

3. Configure detailed options

4. Check FCHK, checksum ofJESD204B interface parameters

5. Set additional digital outputconfiguration options

6. Re-enable lane(s)

4

配置流程

//配置AD9250的寄存器的工作方式

write(5F, 15); //204B link control,powerdown JESD204B link,ilas test mode

Write(0B,01); //選擇時(shí)鐘的分頻系數(shù)

Write(FF,01); //將寫入的控制數(shù)據(jù)統(tǒng)一更新,該功能可以讓輸入的控制數(shù)據(jù)在向0xFF寫1后統(tǒng)一獲得更新。

write(5E, 0x22); //SelectQuick Configuration Option

Write(FF,01); //將寫入的控制數(shù)據(jù)統(tǒng)一更新,該功能可以讓輸入的控制數(shù)據(jù)在向0xFF寫1后統(tǒng)一獲得更新。

write(0x6e, 0x01); // disabled scrambling

write(5F, 14); //204B link control,power onJESD204B link,

AD參數(shù)配置:5

1、 sof_reset(0x00):復(fù)位所有的寄存器()

2、 pdwn(0x08):關(guān)掉JESD204B

3、 global clock(0x09):(默認(rèn))

4、 global clock divide(0x0B):()

5、 ADC VREF (0x18):

6、 Pll low enable(0x21):

JESD鏈路配置:

1、204B Link CTRL1 (0x5f)

2、204B quick config (0x5e)

3、CML output adjust (0x15)

4、PDWN modes (0x08) :待機(jī)時(shí)JESD的電源工作模式

5、204B parameters subclass/Np (0x73)

6、204B Link CTRL 1 (測(cè)試采樣使能)

7、SYNCINB±/ SYSREF± CTRL (0x3a)

5

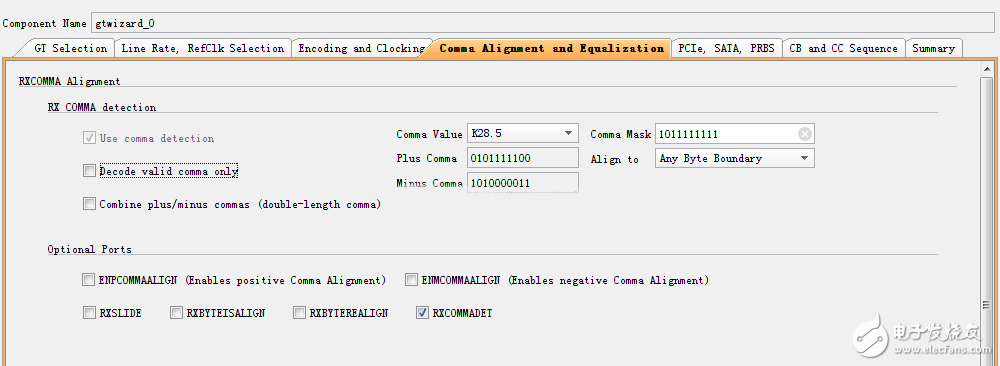

Kintex-7的GTX的配置注意事項(xiàng)

K碼 在配置gtx時(shí)需要配置兩個(gè)K碼 K28.5和K28.7 這兩個(gè)K碼譯碼后僅有一bit的數(shù)據(jù)不同,所以在設(shè)置時(shí)可以設(shè)置K28.5作為K碼,同時(shí)mask其中的第二bit的數(shù)據(jù)。

第二個(gè)問題:數(shù)據(jù)收到后,在數(shù)據(jù)解析時(shí),應(yīng)該注意的是其數(shù)據(jù)格式的分布 :

采樣數(shù)據(jù)的高位被先發(fā)送出來,所以數(shù)據(jù)采樣后應(yīng)該做一個(gè)調(diào)換。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論