1、引言

實時視頻圖像處理技術的應用十分廣泛,在民用領域有機器人視覺、資源探測和醫學圖像分析等;在軍用領域有導彈精確制導、敵方目標偵察與跟蹤等。

本設計中采用了DSP+FPGA的硬件結構,DSP采用ADI公司的高性能雙核DSP-BF561作為主處理器,負責整個算法的調度和數據流的控制,完成圖像數據的采集與顯示及核心算法的實現;而FPGA作為DSP的協處理器,依托其高度的并行處理能力,完成圖像預處理中大量的累乘加運算。DSP的2個內核與FPGA通過中斷進行通信響應,使系統的各處理器并行工作,提高了DSP內核及FPGA的利用效率,保證了系統采集與顯示的實時性。

2、系統原理與結構

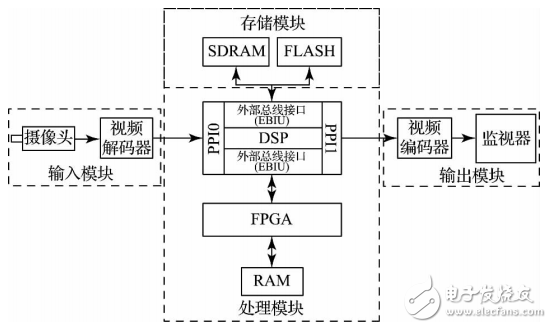

圖像采集與處理系統主要包括4大模塊:圖像采集模塊、存儲模塊、處理模塊和顯示模塊。圖1所示為DSP+FPGA的圖像采集與處理系統硬件結構框圖。

圖1 圖像采集與處理系統硬件結構

系統的前端輸入模塊由CCD攝像頭及視頻解碼器7181B實現,視頻解碼器將CCD接收到的模擬視頻信號轉換為標準的YUV4∶2∶2數字視頻格式,圖像大小為720×576。轉換后的圖像數據通過ADSP-BF561的專用視頻接口PPI0先存儲到RAM中,當采集完一幀圖像數據時DSP的DMA產生中斷,此時FPGA首先對采集來的圖像數據完成圖像的預處理,然后DSP再將預處理的數據取回完成相應圖像處理算法,最后通過PPI1接口由DMA控制器將處理完的視頻數據送到視頻編碼器7171,轉換成標準的模擬PAL視頻信號到監視器上進行顯示。FLASH的作用是存儲系統運行的程序,引導系統的啟動。

針對系統要求,DSP選用AnalogDevices公司的ADSP-BF561處理器,該DSP是專門針對多媒體和通信應用方面的一款16位定點DSP,它集成了2個Blackfin處理器內核,每個內核可實現600MHz持續工作。

FPGA選用Altera公司的EP2C5,它擁有4608個邏輯單元,13個18×18硬件乘法器,多達142個用戶自定義IO口。

2.1、采集模塊設計

CCD攝像頭采集來標準的PAL制式模擬視頻,設計選用ADI的ADV7181B視頻解碼芯片對模擬信號進行A/D轉換。ADV7181B是Analog公司的一款應用廣泛的視頻解碼芯片。該芯片可以自動檢測輸入的復合視頻信號,通過I2C總線配置接口,可選擇圖像輸出格式。由于黑白圖像已能夠滿足系統的檢測需要,因此把模擬信號以ITU-R-656格式YUV(4∶2∶2)輸出。Y信號是亮度信號,U、V信號是色度信號。這樣就可以直接提取該格式的亮度信號,操作比轉換為傳統的RGB格式要簡單得多。

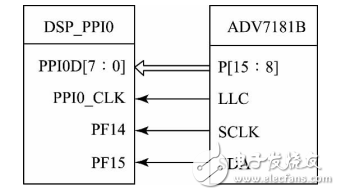

ADV7181B的8根數據線與DSP的PPI0口的8根數據線相連接,通過DSP的2根可編程標志引腳PF來模仿I2C總線,進而對7181B進行相關配置。從而將采集、量化后的視頻信號傳進DSP緩沖區中。輸入模塊的硬件連接如圖2所示。

圖2 采集模塊硬件連接

2.2、存儲模塊設計

由于一幀YUV(4∶2∶2)格式的圖像有720×5762=810KByte,而BF561和FPGA的內部存儲空間分別只有328KByte及14KByte,因此,將SDRAM和RAM存儲器分別作為DSP及FPGA的外擴存儲器。這樣輸入的視頻數據存到外部擴展存儲器中,可以使系統具有大容量、高吞吐率和高存取速度的特點,實現大數據量和實時性的要求。

系統采用2片32MB的HY57V561620CSDRAM,組成32位的數據輸入與輸出,通過4根數據屏蔽線(SDQM[3∶0]),可以進行8位、16位、32位的數據讀寫。選用1片4MByte,32位寬的RAM掛接到FPGA上,其地址線,數據線都與SDRAM的分開。其選通信號CS#與讀寫信號WE#、OE#也由FPGA控制。

2.3、處理模塊設計

DSP與FPGA作為圖像處理模塊的核心,協同完成圖像的處理任務,DSP作為系統的主控制器,FPGA上電后由DSP來完成配置。DSP和FPGA的功能劃分按照算法流程進行,DSP負責整個算法的調度和數據流的控制,而FPGA作為DSP的協處理器。DSP通過AMS3#來片選FPGA,AWE#、AOE#作為讀寫使能,同時DSP的24位地址線(A[25∶2])和32位數據線(D[31∶0])都掛接到FPGA上,這樣DSP與FPGA就可以進行數據的交換。它們各自在系統中完成的任務如下:

1)DSP控制數據流的流向,通過自己特有的PPI圖像接口完成圖像數據的采集與發送,并完成圖像中目標的識別算法;

2)FPGA是DSP的協處理器,FPGA作為DSP的邏輯擴展,幫助DSP來復位視頻編解碼器等這些外部設備;FPGA對采集到RAM中的原始圖像數據完成一些數據密集,但算法簡單、重復性高的圖像預處理功能。再將處理后的數據送回到DSP中完成最后的目標識別算法。

2.4、顯示模塊設計

在數字視頻數據處理完成后,選用ADI公司的視頻編碼器7171將數字信號轉換成PAL制式電視信號,用專用的監視器將圖像結果顯示出來。

BF561的PPI1口的8根數據線與7171的數據線相連,輸出時7171由DSP通過I2C總線配置為輸出PAL制式。

3、系統軟件設計

系統的軟件設計主要包括系統的初始化、圖像的采集與顯示2大部分。針對BF561的雙核結構,這里DSP的coreA完成系統的初始化以及圖像采集與顯示,coreB完成目標識別算法,這樣可以減少雙核的公共變量及數據共享,簡化雙核交互的時序控制設計,使系統更加穩定的工作,而FPGA進行圖像的預處理。

3.1、系統初始化

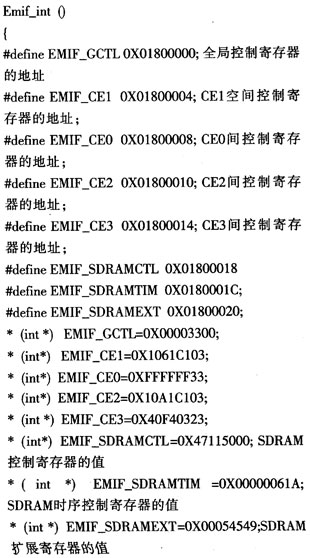

首先,要對BF561的PLL鎖相環時鐘、EBIU外部總線接口及中斷向量表進行初始化設置。外部晶振產生的27MHz時鐘通過PLL的20倍頻使內核工作在540MHz的時鐘頻率下;EBIU配置為外部總線接口打開。

EBIU配置好后,對DSP的外設進行初始化設置,依次對SDRAM、FPGA等外設進行初始化。將地址0x2E800000、0x2EF00000映射到FPGA上產生一個8位控制寄存器Reg1和32位控制寄存器Reg2,向寄存器Reg1寫控制字,控制7181、7171硬復位,并配置PPI口的驅動時鐘,向寄存器Reg2寫控制字,控制RAM地址總線及數據總線與DSP的對接。

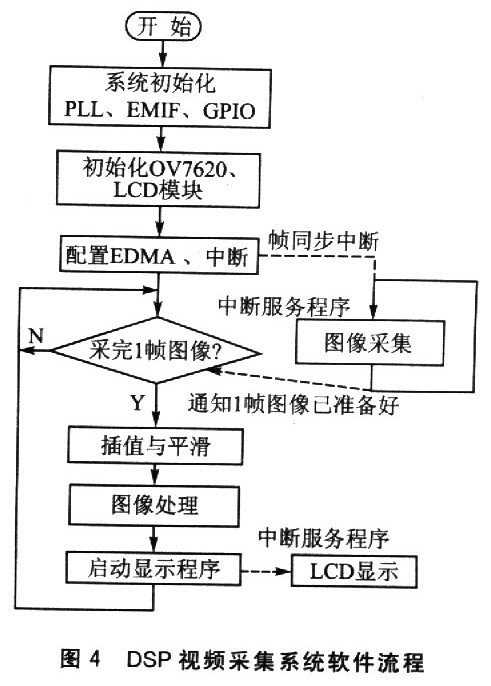

3.2、圖像的采集與顯示

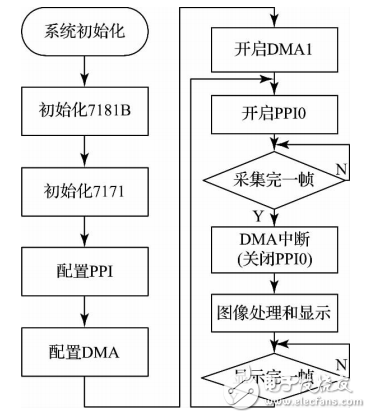

系統圖像采集與顯示的軟件流程圖如圖3所示。

圖3 ?圖像采集與顯示流程

系統初始化結束后,對負責圖像編解碼的7181B和7171通過I2C總線進行初始化。將7181配置輸出為ITU-R-656模式,7171配置輸出為PAL制式。通過編寫控制字到PPI口的控制寄存器PPIx_CONTROL,相應地PPI0口配置為接收ITU-R-656模式,并采用有效場模式,PPI0口僅輸出每場的有效數據到DSP中,而把消隱行的數據過濾掉,減小圖像數據的存儲空間,并節約內核開銷;PPI1口則配置為GP模式,這時需要BF561產生水平同步信號和垂直同步信號配合PPI1口完成數據輸出。

BF561的PPI口必須和DMA引擎一起使用。每個PPI_DMA通道可配置為發送或接收操作,最大的吞吐量是PPIx_CLK16bit/transfer,為了提高效率,這里采用8bit數據、PACK_EN=1(使能打包模式)、DMA32=1。即PPI和DMA都以其最大帶寬傳輸數據。系統中圖像采集與顯示都通過DMA完成,無需內核參與,最大限度地節約了內核開銷,使內核集中完成圖像的處理算法任務。

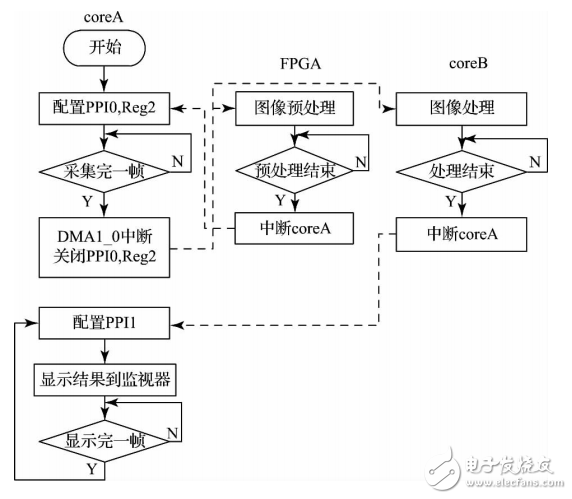

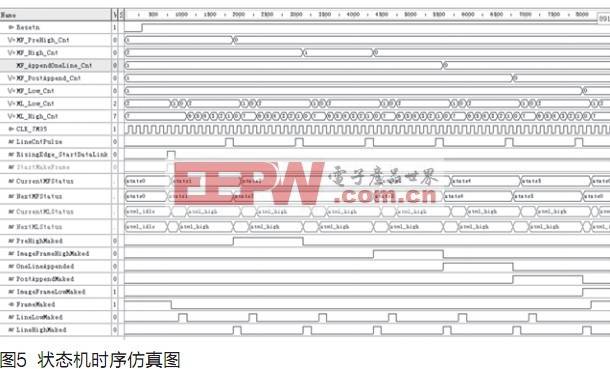

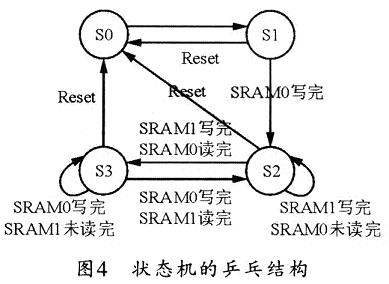

3.3、圖像數據流的存儲與傳輸及其時序設計

為了提高系統運行效率,發揮DSP的流水線執行及FPGA并行處理的優勢,把RAM分為3塊區域,Frame0和Frame2作為乒乓緩存,輪流作為圖像數據緩存的目的地和FPGA處理數據的源頭;Frame1存放FPGA預處理后的結果。同樣SDRAM開辟3塊區域,Buffer0、2存放從FPGA搬移的預處理結果,Buffer1存放最后結果。

在FPGA完成預處理后觸發DSP中斷,開啟PPI0口,并且DSP總線與RAM再次對接,coreA將預處理結果搬移到SDRAM中,同時DMA1_0控制PPI0采集新一幀的圖像數據到RAM。此時coreB已完成目標識別并將最終結果存入SDRAM,并中斷coreA,coreA打開PPI1,由DMA1_1控制PPI1完成最終結果的顯示。圖像的采集與顯示都由DMA控制,不會干預coreA對預處理結果的搬移。而搬移速度要快于采集速度,所以在PPI0采集完新的一幀后,上一幀的預處理結果已經搬完。DMA1_0產生中斷,PPI0、DSP總線與RAM對接再次關閉,如此循環往復。其實現過程流程圖如圖4所示。

圖4 ?圖像數據流處理流程

4、實驗結果及分析

對25frames/s、16bit、720×576像素的視頻圖像進行顯示速度測試,利用示波器檢測監視器上掃描一行圖像的波形如圖5所示。

圖5 顯示一行的波形

分析圖中波形,顯示一行圖像的時間為64μs,一幀完整圖像共有625行,所以顯示一幀圖像所用的時間為40ms。達到了CCD攝像頭25frames/s的刷新速度,實現了系統的實時采集處理。

5、結論

為實現圖像的實時采集與處理,設計了一種基于ADSP-BF561+FPGA的圖像采集與處理系統。結合BF561的PPI視頻接口與其DMA的特點,設計了圖像采集與顯示算法,充分利用了DSP的流水線執行與FPGA及雙核DSP并行處理的優勢。通過實驗論證,圖像顯示的刷新時間能夠達到25frame/s,達到了實時性要求。并且該圖像采集與處理系統還具有結構緊湊、功耗低、集成度高、執行效率高等優點。為整個數字圖像處理系統的設計實現奠定了重要的實踐基礎。

電子發燒友App

電子發燒友App

評論