創(chuàng)建自定義賽靈思板級描述(XBD)文件不僅有助于節(jié)省時間,而且還能確保設(shè)計項目按計劃推進(jìn)。為您設(shè)計的任意開發(fā)板創(chuàng)建一個XBD文件并非難事。

FPGA廠商推出了許多出色的評估板和專用開發(fā)板,既可用于評估FPGA,甚至還能作為開發(fā)系統(tǒng)的基礎(chǔ)。不過有時設(shè)計項目需要的功能可能在評估板上并未提供,或者需要一款較小型的終端系統(tǒng)。在此情況下,設(shè)計團(tuán)隊必須構(gòu)建一款定制開發(fā)板。

賽靈思每款評估板都配套提供一份XBD文件,其列出了FPGA的板載外設(shè)、配置、控制寄存器和引腳。XBD文件不僅可確保設(shè)計團(tuán)隊工作有條不紊地開展工作,而且還有助于他們?yōu)楫?dāng)前乃至未來在開發(fā)板上實現(xiàn)的設(shè)計制定最佳策略。

當(dāng)然,如果您創(chuàng)建的是定制開發(fā)板,那就無法獲得賽靈思提供的XBD文件支持。但是花時間開發(fā)自己的XBD文件還是值得的。專門制作的XBD文件能幫助設(shè)計團(tuán)隊管理項目,簡化設(shè)備驅(qū)動程序和固件開發(fā)。所幸的是,經(jīng)過一番研究和努力,用戶不費周折就可以為自己的開發(fā)板創(chuàng)建一份自定義XBD文件。(對使用Vivado設(shè)計套件的用戶而言,賽靈思在隨Vivado設(shè)計套件2014.1版本一并推出的新型實用工具Board Manager中提供了XBD優(yōu)化功能。如欲了解更多信息,敬請查閱“Vivado設(shè)計套件用戶指南” http:/china.xilinx.com/support/docu-mentation/sw_manuals/xilinx2013_3/ug898-vivado-embedded-design.pdf 。)

下面我們來看看開發(fā)自定義XBD文件的方法之一。就本實例設(shè)計而言,我們針對采用Virtex?-5 FX30T FPGA的定制開發(fā)板創(chuàng)建XBD文件。

我們從賽靈思和分銷商安富利(Avnet)提供的技術(shù)文檔入手。由于我們必須自己編寫XBD文件,因此必須遵循XBD語法。賽靈思已在平臺規(guī)范格式參考手冊中介紹了XBD語法(敬請查閱: )。

您的定制開發(fā)板極可能需要串行通信(RS232和RS422)、模數(shù)轉(zhuǎn)換器(ADC)、數(shù)模轉(zhuǎn)換器(DAC)、RAM和閃存存儲器。正好賽靈思和安富利的評估板也提供這些外設(shè),所以找到有類似部件的開發(fā)板并參考其相關(guān)XBD文件就能加快自定義XBD文件的開發(fā)進(jìn)程。

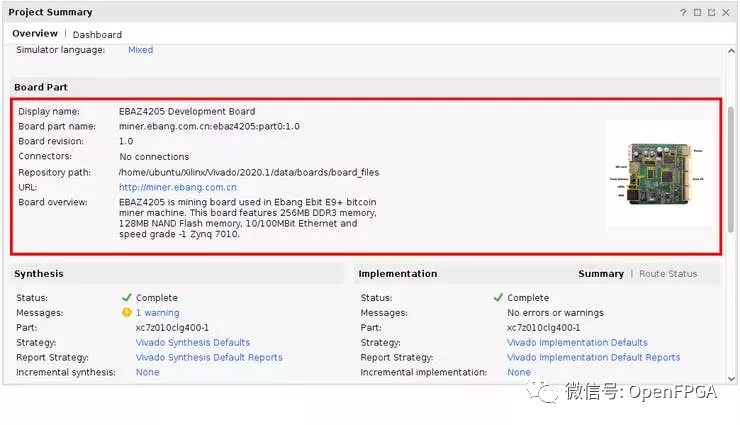

每個XBD文件都有不同的模塊,其定義了開發(fā)板支持的FPGA接口,并且每個模塊都有一系列屬性、參數(shù)和端口。因此文件第一項記錄就是全局屬性命令、廠商信息、開發(fā)板名稱及其版本號、輔助Web URL以及開發(fā)板描述的簡明版本和詳細(xì)版本。

文件的本地屬性命令在BEGIN-END模塊之間進(jìn)行定義,并用特定格式表達(dá),這也可以查閱平臺規(guī)范參考手冊。就本實例來說,我們將使用面向Virtex-5FX30T FPGA的ISE設(shè)計套件12.4版本。Virtex-5FX30T FPGA含有可配置邏輯單元和PowerPC? 440硬核。

除了FPGA之外,定制開發(fā)板將根據(jù)設(shè)計需要還包括不同外設(shè),如串行通信接口(RS232、RS422)、ADC、DAC、SRAM等。您可通過使用串行通信專用IP模塊來滿足多個UART需求。例如,您可用外部存儲器控制器(EMC) IP實現(xiàn)SRAM與FPGA的連接,并用通用I/O (GPIO) IP將ADC和DAC與FPGA相連接。

在我們的實例設(shè)計中,我們制作自定義XBD文件來滿足器件數(shù)據(jù)手冊中列出的功能及器件需求。FPGA的輸入時鐘信號為20 MHz。處理器運(yùn)行頻率為200MHz,而處理器本地總線(PLB)工作頻率為100 MHz。根據(jù)上述信息,我們能夠保證維持本地器件驅(qū)動時序。圖1給出了定制硬件的方框圖。

?

讓我們開始創(chuàng)建自定義文件。首先從全局屬性命令著手,隨后是時鐘信號,這是所有開發(fā)板都必須遵循的步驟,如下所示:

?

?

接下來我們要在文件中逐一列出開發(fā)板的所有外設(shè)。(對每個外設(shè)模塊詳細(xì)編碼信息感興趣的讀者可查閱配套提供的PDF文件《定制開發(fā)板XBD編碼詳情》,敬請訪問官方網(wǎng)站。)

數(shù)模轉(zhuǎn)換器

讓我們從Analog Devices提供的數(shù)模轉(zhuǎn)換器AD7841開始,該數(shù)模轉(zhuǎn)換器(DAC)具有8個通道、3條地址線和14位數(shù)據(jù)線以及一些可處理器件功能的控制信號。該器件通過賽靈思的GPIO IP核與FPGA相連。而器件的地址線(A0-A2)則與處理器地址線相連。

該DAC具有4種控制信號:LDACN、CSN、WRN和CLRN。組建這些信號有兩種方法,您既可以給每個信號分配一個位,也可以直接設(shè)計一個4位寄存器,具體取決于您的應(yīng)用所需的信號處理方式。該DAC為14位D0-D13。

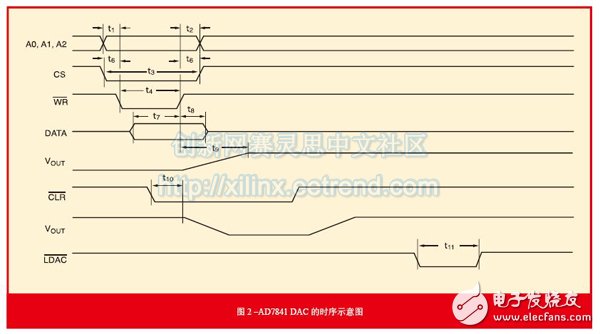

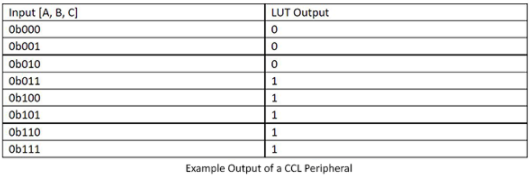

現(xiàn)在我們已經(jīng)了解XBD文件中所列首個器件DAC的一個細(xì)節(jié),下面我們來了解一下如何寫入固件。在開發(fā)器件驅(qū)動程序時,我們應(yīng)認(rèn)真研究數(shù)據(jù)手冊和時序示意圖。時序示意圖如圖2所示。

?

器件數(shù)據(jù)手冊說明了用戶必須閱讀時序示意圖并生成控制信號。時序信息t0-t11完全遵照Analog Devices提供的數(shù)據(jù)手冊(AD7841)。第一步要設(shè)置信號方向為出口,然后通過寫入1到相應(yīng)地址將其拉高。例如,將方向LDACN信號設(shè)為出口,然后通過以下語句將其拉高:

?

信號之間的延遲可用“for”循環(huán),也可選擇“NOP”指令來實現(xiàn)。每個信號的序列和建立-保持時序也同樣重要,這些規(guī)范均在器件數(shù)據(jù)手冊中予以提供。這里,當(dāng)處理器運(yùn)行頻率為200 MHz時,每個增量相當(dāng)于5納秒。

借助賽靈思EMCIP核與XBD文件,存儲器的接口連接和控制變得輕松簡便。我們在器件數(shù)據(jù)手冊中找到了時序約束,并將其列在XBD文件中。

通信與SRAM接口

我們將使用賽靈思的XIL UART IP將RS232和RS422驅(qū)動程序IC與Virtex-5 FPGA實現(xiàn)接口相連。我們針對RS422和RS232通信分別選擇了MAX3079和MAX3237這兩款Maxim器件。我們通過GPIO IP核來生成RS422 IC的控制信號。

就存儲器而言,我們選擇賽普拉斯的靜態(tài)RAM,即CY7C1061BV33器件,從而利用賽靈思外部存儲器控制器IP核(XIL_EMC)將其連接到FPGA。借助該IP核和XBD文件,存儲器的接口連接和控制變得輕松簡便。我們在器件數(shù)據(jù)手冊中找到了時序約束,并將其列在XBD文件中。由于賽靈思IP核足以處理該存儲器,因而無需使用單獨的器件驅(qū)動器。

ADC接口

在該設(shè)計中,將ADC與FPGA進(jìn)行接口相連是一個難題,因為來自不同傳感器的所有輸入模擬信號都在±10V范圍之內(nèi)。為了滿足實例板的功能要求,我們選用了Analog Devices的AD7891-1。該ADC具有8個通道和一個12位數(shù)據(jù)總線,并提供可選的串行和并行接口。在該設(shè)計中,經(jīng)實踐證明并行接口是更好的選擇。

該器件工作在5V輸入上,由于FPGA I/O電壓為3.3V,因此我們的設(shè)計需要可實現(xiàn)與FPGA接口相連的收發(fā)器。接下來我們將會把此收發(fā)器作為緩沖器。收發(fā)器在一側(cè)連接到FPGA,而在另一側(cè)則連接到ADC。FPGA可處理緩沖器的控制信號。我們需要認(rèn)真處理器件的方向引腳和輸出啟用引腳,以便控制FPGA到ADC的數(shù)據(jù)流,反之亦然。可將器件控制信號歸組為5位寄存器。

器件的轉(zhuǎn)換端(EOCN)應(yīng)在自定義XBD文件中分開列出,因為這是一個非常重要的信號。EOCN表明轉(zhuǎn)換已經(jīng)完成且新數(shù)據(jù)可用于FPGA進(jìn)行處理。

緩沖器接口

在本設(shè)計中,我們選擇了德州儀器的SN74ALVC164245電平位移收發(fā)器作為緩沖器。其是一款16位非反相總線收發(fā)器,擁有2個單獨的端口及供電軌。可將器件的端口B與5V ADC連接,而端口A則與3.3V FPGA連接。該配置支持從5V到3.3V的信號轉(zhuǎn)換,反之亦然。

方向引腳設(shè)為低,將端口B的數(shù)據(jù)傳輸至端口A。若設(shè)為高,則情況正好相反,端口A的數(shù)據(jù)將被傳輸?shù)蕉丝贐。要讀取ADC的數(shù)據(jù),需要將輸出使能(OEN)和方向(DIR)引腳設(shè)為低。在寫入操作中,F(xiàn)PGA將向ADC發(fā)送指令,且方向引腳為高而輸出啟用引腳為低。在我們的實例設(shè)計中,我們將緩沖器的輸出啟用引腳進(jìn)行拉高,從而避免了總線沖突。我們在該設(shè)計中使用了兩個緩沖器和兩個ADC。

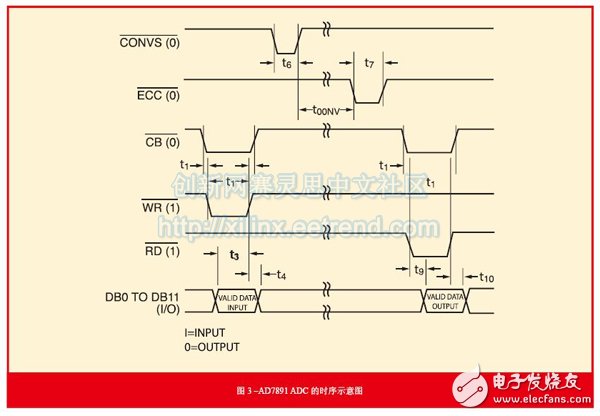

圖3為并行接口模式的時序示意圖,我們用它來生成控制信號。從t0到t11的信號時序通過Analog Devices的器件數(shù)據(jù)手冊引用。

?

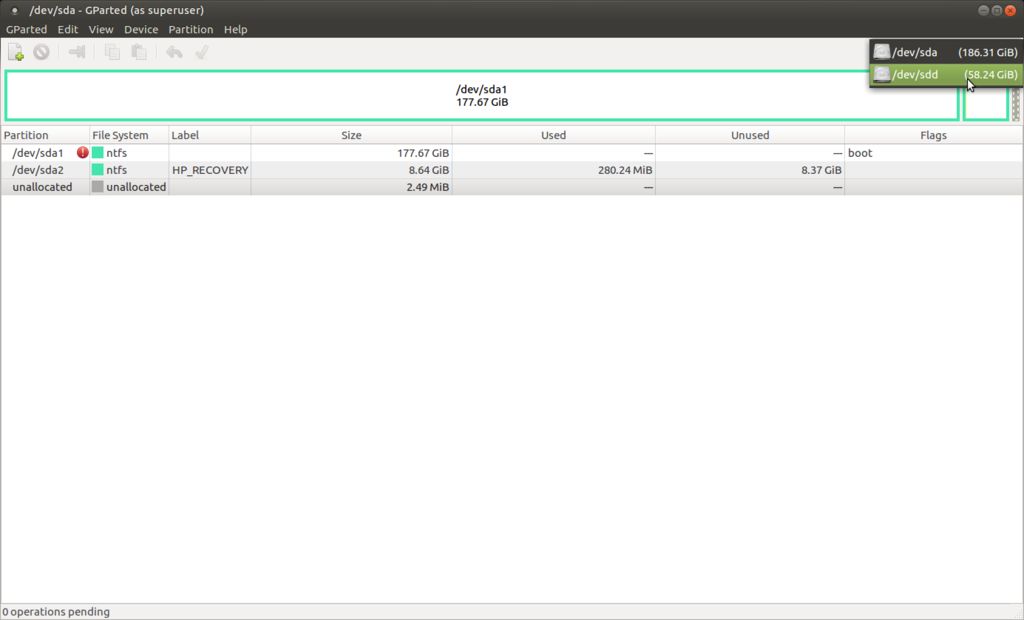

您可用Notepad或WordPad等任何編輯程序創(chuàng)建或修改該文件。您必須將此文件保存擴(kuò)展名為.xbd的格式文件。完成后,文件必須保存到特定的路徑下,當(dāng)創(chuàng)建新項目時,對EDK工具直接可見。啟動新項目時,應(yīng)為定制開發(fā)板選擇該文件。

例如,假設(shè)開發(fā)一個名為“customboard”的開發(fā)板,該開發(fā)板對EDK工具可見,您應(yīng)當(dāng)遵循特定的目錄結(jié)構(gòu)要求。這是很重要的一步。我們的實例“customboard_RevX_vX_X_0.xbd”一旦創(chuàng)建后,必須保存到以下目錄下:

示例路徑:

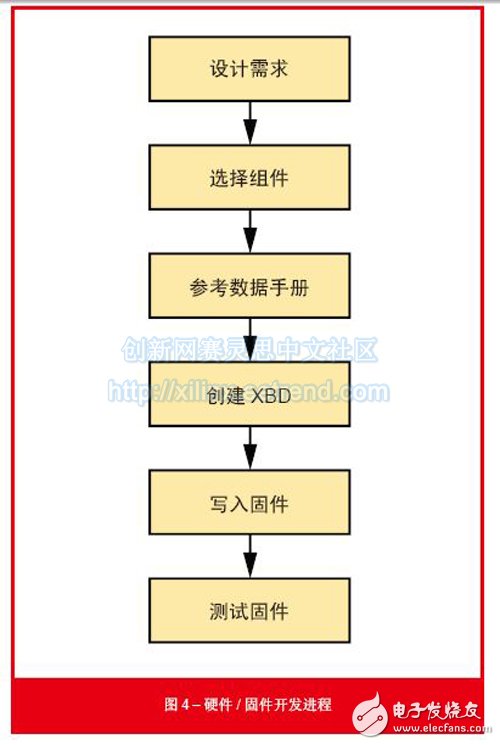

此外,針對任何應(yīng)用的硬件或固件開發(fā)也應(yīng)遵循特定的步驟,如圖4所示。

?

加速開發(fā)進(jìn)程

打造定制硬件以便為自己的特定應(yīng)用開發(fā)器件驅(qū)動程序,這對于嵌入式設(shè)計人員來說是一項充滿挑戰(zhàn)性的工作。賽靈思提供了大量有關(guān)開發(fā)過程的文獻(xiàn)資料,也為開發(fā)工作提供了通用板級描述文件。您可輕松定制并修改該文件以滿足您自身定制硬件的需求。硬件配置如需任何修改或改動,您只需參考一個統(tǒng)一的文件即可,并將所有器件相關(guān)的改動整合到該文件中。這樣,自定義XBD文件就能提高生產(chǎn)力,加速開發(fā)進(jìn)程。

電子發(fā)燒友App

電子發(fā)燒友App

評論