現(xiàn)有的工具和技術(shù)可幫助您有效地實(shí)現(xiàn)時(shí)序性能目標(biāo)。

當(dāng)您的FPGA 設(shè)計(jì)無法滿足時(shí)序性能目標(biāo)時(shí),其原因可能并不明顯。解決方案不僅取決于FPGA 實(shí)現(xiàn)工具為滿足時(shí)序要求而優(yōu)化設(shè)計(jì)的能力,還取決于設(shè)計(jì)人員指定前方目標(biāo),診斷并隔離下游時(shí)序問題的能力。目前,設(shè)計(jì)人員掌握了一些使用技巧,可以幫助您設(shè)置時(shí)鐘;通過Synopsys Synplify Premier 等工具正確設(shè)置時(shí)序約束;然后調(diào)整參數(shù),以滿足賽靈思FPGA 設(shè)計(jì)的性能目標(biāo)。

有多個(gè)攻克角度,其中包括:

?更好的設(shè)計(jì)設(shè)置,例如完整、準(zhǔn)確的時(shí)序約束和時(shí)鐘規(guī)格;

?節(jié)省時(shí)間的設(shè)計(jì)技術(shù),例如仔細(xì)RTL編碼,以求更佳的性能效果,以及將造成最大性能問題的設(shè)計(jì)部件整合在一起,從而縮短隨后調(diào)整設(shè)計(jì)時(shí)序的迭代運(yùn)行時(shí)間。

?綜合關(guān)聯(lián),并布局布線時(shí)序,以產(chǎn)生更好的時(shí)序結(jié)果質(zhì)量(QoR)和時(shí)序收斂。

現(xiàn)在從三個(gè)方面詳細(xì)介紹一下這些技術(shù),并檢測如何使用以實(shí)現(xiàn)您的時(shí)序目標(biāo)。

您需要確認(rèn)您已經(jīng)充分、完全地對您的設(shè)計(jì)進(jìn)行約束,且未過度約束。

第一步:更好的設(shè)計(jì)設(shè)置

最大的成本開銷來自于指定正確、完整的設(shè)計(jì)約束條件。這些約束條件可以在設(shè)計(jì)意圖和設(shè)計(jì)性能目標(biāo)與綜合工具之間實(shí)現(xiàn)通信。綜合設(shè)計(jì)之后,這些約束條件和關(guān)鍵路徑信息將自動傳遞至Vivado?Design Suite布局布線(P&R)工具,以進(jìn)一步確保滿足時(shí)序要求。

綜合工具可以幫助您應(yīng)對設(shè)置綜合前約束這項(xiàng)艱巨的任務(wù)。您的任務(wù)清單如下:

1.識別時(shí)鐘

2.識別并創(chuàng)建時(shí)鐘組和時(shí)鐘關(guān)系

3.約束時(shí)鐘

4.約束設(shè)計(jì)輸入和輸出

5.定義多周期路徑和錯(cuò)誤的路徑

您需要確認(rèn)已經(jīng)充分、完全地對您的設(shè)計(jì)進(jìn)行約束,且未過度約束。過度約束將導(dǎo)致運(yùn)行時(shí)間延長,并有可能報(bào)告錯(cuò)誤的關(guān)鍵路徑。務(wù)必要指定多周期和錯(cuò)誤路徑,并對衍生時(shí)鐘設(shè)置約束(define_path_delay, define_false_path)。

設(shè)置Vivado流程的初始約束文件

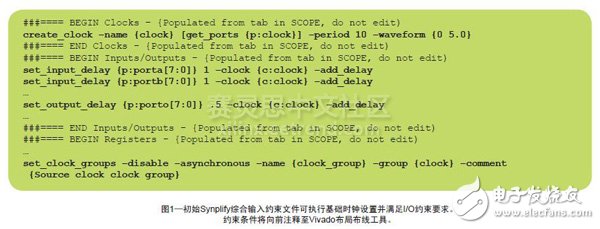

由于約束條件設(shè)置工作非常困難,因此綜合軟件可以提供一個(gè)初始約束模版,其中的基礎(chǔ)約束和語法可以作為此項(xiàng)工作的起點(diǎn)。例如,在Synplify綜合軟件中,運(yùn)行TCL實(shí)用程序?yàn)樘囟ǖ脑O(shè)計(jì)創(chuàng)建一個(gè)初始FDC文件:

TCL: create_fdc_template

圖1給出了該流程將生成的約束文件(.fdc)的實(shí)例。該實(shí)例中,您可以看到聲明時(shí)鐘、時(shí)鐘組(時(shí)鐘之間的關(guān)系)和輸入/輸出延遲等關(guān)鍵項(xiàng)目已經(jīng)納入考慮范圍。

針對Vivado Design Suite流程中約束設(shè)置的最佳實(shí)踐

在Vivado Design Suite流程中設(shè)置約束條件時(shí),要確保進(jìn)行以下操作:

?定義輸入端口或與輸入端口連接的網(wǎng)絡(luò)上的所有基礎(chǔ)時(shí)鐘。

?定義黑盒輸出引腳上的時(shí)鐘。

?定義網(wǎng)絡(luò)上生成的時(shí)鐘。

?不要定義邏輯選通時(shí)鐘。

?提供正確的時(shí)鐘約束:不要過度約束,并確保將不相關(guān)的(又稱異步)時(shí)鐘放置在單獨(dú)的時(shí)鐘組中。

?定義時(shí)序例外,例如錯(cuò)誤路徑和多周期路徑。

提示:在Vivado Design Suite中,時(shí)鐘約束應(yīng)盡量接近源時(shí)鐘,而不是賽靈思 ISE? Design Suite流程中的BUFG。

確保您的約束條件正確無誤

我們建議在設(shè)計(jì)設(shè)置階段采用四種約束驗(yàn)證技術(shù)。為了讓您了解應(yīng)該做的約束檢查類型,我們來看一下Synplify軟件執(zhí)行的各項(xiàng)檢查。

?

首先,運(yùn)行“語法檢查”—即快速進(jìn)行約束條件檢查,其中包括其嵌入的“get_XX” 和 “all_XX”命令,用以發(fā)現(xiàn)和清理任何約束語法錯(cuò)誤。錯(cuò)誤會顯示在日志文件中,并可以超鏈接至錯(cuò)誤手冊,以解釋錯(cuò)誤并提出修改建議。使用Tcl命令check_fdc_query。

第二,運(yùn)行“綜合檢查”以檢測與硬件相關(guān)的錯(cuò)誤,例如錯(cuò)誤編寫的觸發(fā)器。這些錯(cuò)誤會以單獨(dú)的日志文件報(bào)告。

第三,運(yùn)行基礎(chǔ)“快速綜合”,以檢查時(shí)鐘設(shè)置問題,包括聲明、衍生和推斷時(shí)鐘。快速綜合支持執(zhí)行時(shí)鐘設(shè)置檢查,因其可生成時(shí)鐘報(bào)告和時(shí)序報(bào)告,進(jìn)而使時(shí)鐘設(shè)置問題明朗化。

一些綜合工具可支持在“快速”模式下運(yùn)行綜合,其為了實(shí)現(xiàn)較短的運(yùn)行時(shí)間,其會禁用一些綜合優(yōu)化。在Synplify Premier綜合軟件中,您可以通過以下命令實(shí)現(xiàn):

set_option –fast_synthesis 1

綜合編譯器將創(chuàng)建一個(gè)綜合報(bào)告時(shí)鐘總結(jié),您可以使用其中有關(guān)推斷時(shí)鐘的信息用以識別、定義和約束時(shí)鐘。

第四,運(yùn)行全面的“約束條件檢查”。該檢查會查找關(guān)于時(shí)鐘關(guān)系、未約束開始/結(jié)束點(diǎn)、未鎖定I/O和無約束I/O的約束設(shè)置問題。

一個(gè)全面的約束檢查還會查找正確應(yīng)用的約束和實(shí)例名稱。例如,它會標(biāo)記出應(yīng)用于不存在或無效參數(shù)和對象的時(shí)序約束。然后該工具會針對不可應(yīng)用的約束和未找到的實(shí)例生成詳細(xì)的解釋性報(bào)告,以便糾正約束文件。Synplify綜合工具將在綜合預(yù)先映射階段自動運(yùn)行這些檢查,或者您可以在綜合開始時(shí)使用以下TCL命令運(yùn)行約束檢查:

TCL: project -run constraint_check

運(yùn)行這些基本的檢查類型可在綜合周期的早期就能找出潛在的錯(cuò)誤,從而改進(jìn)結(jié)果的質(zhì)量(見圖2)。

?

運(yùn)行綜合之后,請務(wù)必要分析后期綜合時(shí)序報(bào)告,因?yàn)槠淇梢蕴峁┲匾男畔ⅰ@缭谑褂肧ynplify軟件時(shí),時(shí)序報(bào)告的起始時(shí)鐘部分中的“系統(tǒng)時(shí)鐘”顯示,一些I/O沒有被約束。此報(bào)告的接口信息將確認(rèn)情況是否如此。

第二步:RTL代碼風(fēng)格和關(guān)鍵路徑調(diào)整

為了收斂更好的時(shí)序,我們建議您針對有限狀態(tài)機(jī)、RAMS、數(shù)學(xué)/DSP功能、時(shí)鐘樹和移位寄存器使用特定的代碼風(fēng)格。結(jié)果將改進(jìn)時(shí)序QoR,因?yàn)橥ㄟ^FPGA原語構(gòu)建模塊,綜合工具能夠更好地推斷實(shí)現(xiàn)。

另外,這些代碼風(fēng)格可以避免創(chuàng)建不必要的邏輯,例如推斷鎖存器、RAMS的讀取/寫入檢查邏輯,以及已經(jīng)裝入DSP原語中的邏輯。關(guān)于這個(gè)話題我們已經(jīng)談了很多,使用綜合工具中的核生成器性能是關(guān)鍵考慮因素。例如,Synplify軟件包含一個(gè)SynCore IP向?qū)В梢詾橹С肿止?jié)的RAM自動生成所需的RTL代碼風(fēng)格。其他IP生成器,例如賽靈思IP Catalog、Synopsys Synphony Model Compiler或Synopsys DesignWare coreTools和DesignWare Building Blocks,也可以幫助您配置IP,執(zhí)行許多DSP和數(shù)學(xué)功能,并創(chuàng)建良好的RTL代碼風(fēng)格。如果是手動編碼,請記住以下內(nèi)容:

針對有限狀態(tài)機(jī)

?對于賽靈思流程,啟動后請使用同步復(fù)位將硬件設(shè)置為有效狀態(tài),或者在操作期間復(fù)位硬件。

?將時(shí)序模塊從combinational-always模塊中分離。

?為所有可能的現(xiàn)態(tài)指定次態(tài)。

針對模塊RAM

?在一切可能的地方盡量編碼同步RAM,因?yàn)樗鼈円话銜暂^高的時(shí)鐘頻率運(yùn)行。

?將RAM編碼放置在單獨(dú)的模塊里,以便易于在網(wǎng)表級別進(jìn)行調(diào)試。

?在決定使用RAM(帶特定復(fù)位條件、支持雙端口或字節(jié)的RAM,或非對稱RAM)之前,請看一下推薦的代碼風(fēng)格,并查看是否支持推斷。如果不支持,則網(wǎng)表結(jié)束時(shí)可能創(chuàng)建較多的控制邏輯。

?請勿從寫入相同時(shí)鐘周期的同一個(gè)地址中讀取。

?如果其他方法均告失敗,可以使用屬性(syn_ramstyle for Synplify software)強(qiáng)制讓使用寄存器實(shí)現(xiàn),釋放RAM資源供以用于更重要的時(shí)序和更大的RAM。

針對DSP模塊

您可以使用這些原語執(zhí)行過濾器和數(shù)學(xué)函數(shù),例如計(jì)數(shù)器、加法器、乘法器、除法器等。

?將DSP編碼放在單獨(dú)的模塊里,以便易于在網(wǎng)表級別進(jìn)行調(diào)試。

?如果其他方法均告失敗,可以使用屬性(syn_ dspstyle for Synplify in Vivado Design Suite flows)強(qiáng)制使用DSP 模塊實(shí)現(xiàn)。

針對SRL

您可以將移位寄存器裝入選擇select_SRL Xilinx SRL原語或在寄存器中執(zhí)行。

?封裝自動進(jìn)行。對于移位寄存器鏈,Synplify軟件始終會將鏈中最后一個(gè)寄存器留在封裝select_srl之外,以便優(yōu)化時(shí)序QoR。

?如果其他方法均告失敗,可以使用syn_srl風(fēng)格屬性來控制SRL的實(shí)現(xiàn)方式。

針對時(shí)鐘樹

?由于在綜合期間其不會自動推斷,因此建議在RTL中實(shí)例化鎖相環(huán)(PLL)、時(shí)鐘生成器或時(shí)鐘多路復(fù)用器。

?PLL的輸入時(shí)鐘的時(shí)序約束會在PLL輸出針腳上自動生成衍生時(shí)鐘約束

為了更好地檢查時(shí)鐘約束,可以在原理圖查看器中進(jìn)行檢查。例如,Synplify HDL Analyst工具就可在時(shí)鐘樹上運(yùn)行過濾器,使您可以觀察并調(diào)試時(shí)鐘樹和時(shí)鐘約束(見圖3)。

使用模塊化以改進(jìn)關(guān)鍵路徑性能

設(shè)計(jì)的某些部分可能比其他部分對于時(shí)序更加關(guān)鍵,您需要調(diào)節(jié)并逐漸改進(jìn)不執(zhí)行的部分。有一項(xiàng)技術(shù)您可以用于在RTL和網(wǎng)表階段實(shí)現(xiàn)快速調(diào)節(jié),那就是將關(guān)鍵路徑隔離在單個(gè)模塊或子項(xiàng)目中,然后您可以不斷重復(fù)地逐漸改進(jìn)。另外,您可以強(qiáng)制Vivado布局布線工具將元素緊密放置,從而進(jìn)一步確保時(shí)序QoR。綜合期間您可針對該模塊使用的功能包括:

?綜合之前指定RTL分區(qū)(在Synplify軟件中,它被稱作“編譯點(diǎn)”)或者創(chuàng)建分級子項(xiàng)目。

?綜合之后隔離(導(dǎo)出)為子項(xiàng)目,由于設(shè)計(jì)的部分沒有使用層級項(xiàng)目管理流程執(zhí)行。迭代、修復(fù)和合并結(jié)果。

?使綜合軟件與Vivado布局布線工具實(shí)現(xiàn)通信,將關(guān)鍵路徑放置在多個(gè)SLR設(shè)備的同一個(gè)層級內(nèi),例如Virtex?-7 2000T FPGA,以避免跨SLR延遲。

第三步:實(shí)現(xiàn)最終時(shí)序收斂

一般時(shí)序可以在綜合后和布局布線后報(bào)告(見圖4)。例如,Synplify軟件支持使用TCL命令報(bào)告感興趣的設(shè)計(jì)特定部分(report_timing)。

為了進(jìn)一步改進(jìn)時(shí)序QoR,我們建議您關(guān)聯(lián)后綜合和后P&R的時(shí)序結(jié)果,尤其是針對時(shí)序關(guān)鍵路徑上的給定起點(diǎn)和終點(diǎn)的時(shí)序裕量。在Synplify Premier綜合軟件中,例如您可以并排顯示后綜合和P&R時(shí)序報(bào)告,以讀取時(shí)序結(jié)果。

關(guān)聯(lián)工具可并排對比結(jié)束點(diǎn)、起始點(diǎn)和所需階段的狀態(tài)。根據(jù)終點(diǎn)時(shí)鐘報(bào)告路徑。而在指定“時(shí)序裕量”條件中前后P&R時(shí)序沒有關(guān)聯(lián)好的路徑將標(biāo)記為“關(guān)聯(lián)不匹配”,以便您采取措施。典型的措施是針對綜合工具指定所謂的“布線”約束,其僅在綜合階段加強(qiáng)時(shí)序路徑約束。例如:

FDC約束輸入文件至綜合:

set_clock_route_delay {c:clka} 1.4

這些約束使綜合在這些路徑上“更加努力”地滿足時(shí)序性能的要求,從而產(chǎn)生更好的關(guān)聯(lián)和QoR。

時(shí)序關(guān)聯(lián)性能的好處是,您可以從深層次查看引起問題的準(zhǔn)確路徑,例如改變每個(gè)結(jié)束點(diǎn)顯示的路徑數(shù)量。您可以搜索感興趣的特定時(shí)鐘或?qū)嵗@示他們的時(shí)序路徑。此外,還可以對時(shí)鐘進(jìn)行比較和顯示,以進(jìn)一步幫助時(shí)序關(guān)聯(lián)(見圖5)。

您可以看到,您需要完成一些步驟并需要在Vivado Design Suite流程中花一些時(shí)間,才能實(shí)現(xiàn)更好的時(shí)序性能。我們所述的方法可以及早發(fā)現(xiàn)時(shí)鐘約束設(shè)置問題,同時(shí)還可以提供各種技術(shù)以調(diào)節(jié)和關(guān)聯(lián)設(shè)計(jì)和RTL中的時(shí)序,以快速實(shí)現(xiàn)時(shí)序收斂。

電子發(fā)燒友App

電子發(fā)燒友App

評論