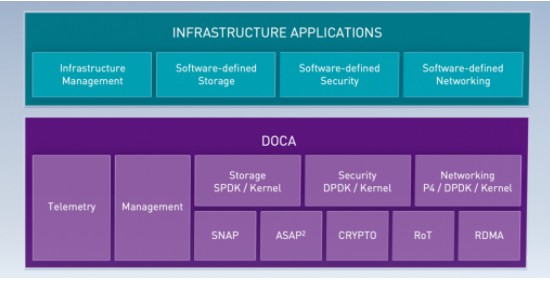

數據中心設備設計人員將結合采用基于FPGA的內核來提供安全的高性能以太網鏈路。

云存儲和IT 服務外包對IT 經理而言極富吸引力,因為這不僅能降低成本,而且還可減輕支持工作。然而有一個大的顧慮就是,這樣做會使敏感數據流出公司防火墻外,造成安全隱患。這種顧慮是完全可以理解的,因為信息對于許多公司而言是最寶貴的資產,無論是會計、客戶還是制造相關的數據。

而現在,設備制造商能夠通過使用賽靈思基于FPGA 的解決方案來提高性能和安全水平。滿足以太網新標準MACsec 要求的Algotronix 綜合安全子系統采用基于賽靈思FPGA 的高性能、低時延、高能效IP 核。

基于FPGA 的解決方案比基于軟件的解決方案速度要快得多。此外,專用硬件可接管系統處理器,使其處理其它任務,如深度數據包檢查等。或者,設計人員也可采用成本更低的處理器。

?

加密和認證

保護信息的一個顯著策略就是當數據在網絡中傳輸和在數據中心周圍移動時對其進行加密。一旦數據被非授權方滲透網絡鏈路而攔截,數據加密能夠確保其無法被讀取。原則上,數據還應經過認證,從而確保其完整性。消息認證旨在檢測原始加密數據是否已被篡改,包括因傳輸錯誤而造成變更,抑或是被攻擊者為從中牟利而惡意破壞。

目前以太網傳輸已成為主流通信方式,這是一種既高效又具有可擴展性的高速傳輸方法。隨著以太網標準的普及,以太網傳輸成本不斷降低,這一優勢使其更加引人注目,進而確保以太網繼續成為首選的L2 技術。不過,就在幾年以前,以太網標準還沒有任何加密規范要求,只能采用運行在通信協議棧上層的IPsec 等技術來完成加密工作。

現在,根據IEEE 802.1AE 標準,最新以太網標準擴展版本新增了大量安全措施。該技術在幾年前正式確定,其采用集成式安全系統來加密并認證消息,同時檢測并應對一系列網絡攻擊。該標準被稱為“媒體接入控制安全(Media Access Control Security)”標準,常常簡稱為“MACsec”。Algotronix 從幾年前就開始努力推出能夠根據多種不同數據速率要求提供硬件加速加密功能的IP 核。

(Algotronix 還可提供面向IPsec的IP 核,該產品與MACsec 產品的接口類似,對需要支持雙重標準的系統而言是不錯的選擇。)

簡要介紹MACsec 系統,幫助了解規范的全面性,同時深入說明實現該規范的復雜程度。

信任實體

MACsec 指的是由網絡上的節點組成的一系列信任實體。每個節點都能接收加密消息和明文消息,而系統策略則用于明確如何處理每條消息。內核包括明文消息的旁通選項,無需認證或驗證。與IPsec 等作為端到端技術運行在L3/L4 的協議不同,只要數據包進入或離開以太網LAN,MACsec就能對每個數據包進行解密和驗證。

MACsec 適用于星型或總線型LAN 等以太網拓撲結構,也可支持點對點系統。

M A C s e c 標準采用安全實體(SecY)方法,也就是每個節點或實體都具備與其以太網源地址相鏈接的唯一密鑰。為支持多個虛擬SecY,我們設計出了該IP 核的1G 版本。因此,單個以太網MAC 能針對多用戶LAN 等應用配備多個與之關聯的MACsec SecY。MACsec 通常與IEEE 801.1X-2010 或互聯網密鑰交換(IKE)配合使用,可實現網絡周圍的安全密鑰分配。

數據中心之所以會選擇L2 連接功能在數據中心內移動數據包,是為了提高速度,并最大程度地降低時延和減少數據包中的開銷數據。相比之下,如果用諸如IPsec 等安全的L3 技術進行通信,消息必須傳到協議上層進行處理,而這會增加時延。

此外,L2 解決方案也能避免創建L3 安全策略這一復雜工作。

數據中心能夠采用MACsec 提供防火墻后臺的保護,或將其用在數據中心之間的直接鏈路上。系統管理員可授權設備以安全方式進行通信。設備能夠檢測錯誤或誤用情況,如拒絕服務攻擊(DOS)。

符合可編程要求

市場因需求不同,日趨細分化。可定制FPGA 解決方案理想適合于MACsec。起初,MACsec 的設計是作為一項技術應用于城域網,而現在在數據中心中也找到了其用武之地,這就提高了對基于FPGA 的解決方案的整體需求。

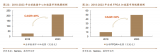

Algotronix 開發MACsec 內核是一個自然演進,因為我們已經打造了一系列稱為“AES-GCM”的加密引擎。這些內核的運行速率分別為1G、10G 和40G。我們通過流水線、提高時鐘速率并從賽靈思Artix?器件逐步發展到Kintex? 器件乃至Virtex? FPGA,來實現上述速率的。我們將利用這些技術來推動VirtexUltraScale ?器件上的吞吐量,使其達到100G。

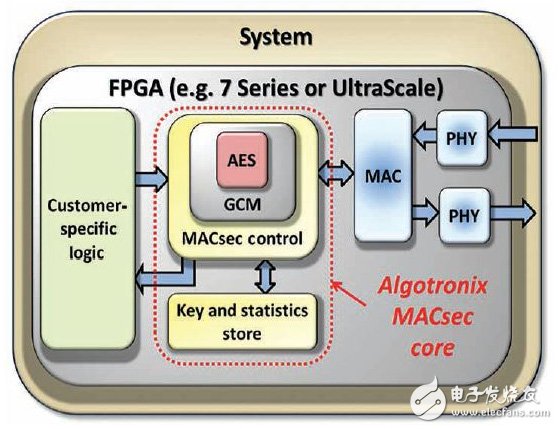

我們使用FPGA 中的IP 核能夠實現多種不同性能,可支持從1GbE到10 GbE 的不同速率(即,內核在最壞情況下的實際吞吐量)。此外我們還計劃推出40G 和100G 的版本。這比基于軟件的系統要快得多。內核通常直連接到硬件MAC(如圖1 所示),因為FPGA 芯片上的嵌入式存儲器的軟件會盡可能足夠快地傳輸數據,以滿足其吞吐量要求。如果在硬件上實現安全功能,同時從未向軟件提供未加密密鑰,那么系統就不那么容易受到特洛伊木馬(Trojan horse)和病毒等常見軟件攻擊。

?

圖1 – 整個MACsec IP核位于FPGA內,可實現最大安全性。

另一個重要考慮事項就是FPGA進行算法加速的系統要大幅降低功耗。加速的算法包括加密函數等,免得再用軟件去實現加速。FPGA 比軟件解決方案的能效明顯要高得多。

所有Algotronix 加密內核都內置了一項重要屬性,那就是能夠在Block RAM 或FPGA 架構的查找表(LUT)中實現稱為“S-Boxes”的關鍵模塊。有了該屬性,客戶可通過綜合平衡兩種資源類型便能利用現有資源實現設計。比方說,如果MACsec 內核外的設計未占用大量的BRAM,那么就可用Block RAM 來實現S-Boxes,否則就用LUT 來實現。

這樣就算IT專業人士必須考慮系統的整個軟件層面的情況時,也能更方便地分析系統漏洞。

MACSEC細節

MACsec 系統的設計理念是:每個數據源使用不同的加密密鑰。接收到消息后,接收器會在片上CAM 的列表中進行查找,明確用以解密數據包的正確密鑰。每個數據包都有編號,確保能檢測并拒絕接收重復或重新發送的數據包,這種方法可防范“中間人”攻擊。

MACsec 還會收集有關被拒收的數據包數量的統計數據以及拒絕的原因。提供統計數據以支持攻擊檢測是超出基本加密隱私、認證和防止重發功能之外的更高一層的安全性,能讓系統管理器主動應對正在進行的攻擊。

我們采取的方法是對業經驗證的AES-GCM 內核周圍的MACsec 邏輯進行“打包”。就此而言,設計高效快速的加密內核只是設計挑戰的一部分。MACsec 標準涉及面廣,包括許多變量。

舉例來說,該標準最初只指定128 位的加密密鑰。采用128 位密鑰, 數據進行10 次轉換( 被稱為“輪”)后在內核中完成加密過程。該標準經修訂后可提供256 位加密密鑰,整個數字加密過程歷經14 輪。這是通過添加流水線級數并提高密鑰存儲所需的內存帶寬才實現的。

MACsec 與以太網流量類型無關,也對更高層協議透明。推出這些內核后,就能方便地將MACsec 添加到系統中,從而進一步提高網絡防護。配備MACsec 的站點仍能與未采用MACsec 額外安全保障機制的其它站點進行通信。

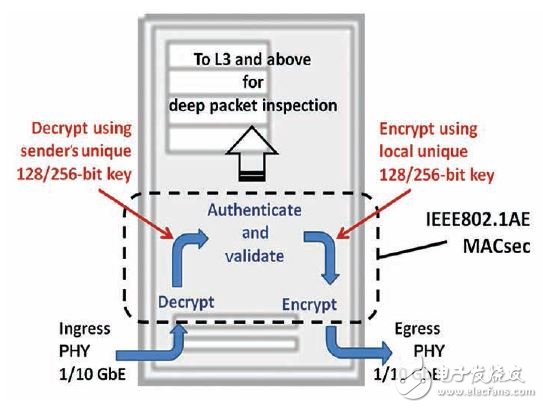

從媒體接入控制器(MAC)將以太網數據包提供給MACsec 內核。您可結合使用1G MACsec 內核、片上收發器和三模以太網MAC(TEMAC)構建高效的小型解決方案。每個數據包都包含發起傳輸的源碼的目的地和地址。該標準保存在MACsec 系統中,但一個重要的因素是,在多次反射傳輸中,“源碼”將是傳遞數據包的最終設備的地址。因此,與可被視為端到端方案的IPsec 不同,MACsec是以逐跳方式工作的。對于每次跳躍,MACsec 都要求輸入端的所有加密數據進行解密,然后使用分配給傳輸設備的唯一密鑰再重新加密。解密的明文可在每一級提供數據包檢查功能,如圖2 所示,也能供流量管理器用以管理數據流。

?

圖2 – 消息在入端口被解密,并在出端口被加密。

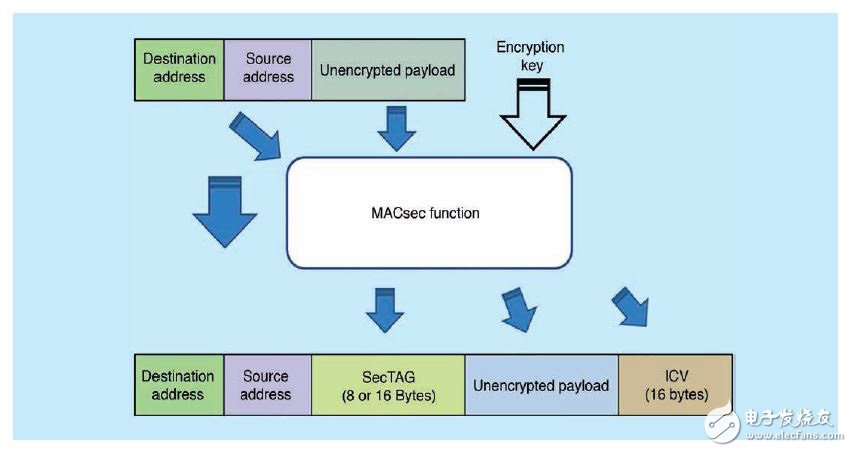

在MACsec 標準中,圖3 給出的報頭包含附加字段“MAC 安全標簽(SecTAG)”,其可定義EtherType,并標明數據包是否加密。數據附加在ICV 字段的消息末尾,則表示已經認證。

?

圖3 – MACsec幀結構包括MAC安全標簽(SecTAG)字段,其可定義EtherType,并標明數據包是否加密。

ICV 協同加密密鑰,可認證包括報頭和MACsec 標簽的幀,進而確保幀的源地址和目的地地址都不會被篡改。我們在FPGA 架構中實現該邏輯,確保其能夠具備快速的可預測的時序,從而最大程度地降低時延。

MACsec 內核包括連接到每個源地址的查找表。該表包含的密鑰必須能夠用來成功解密消息,我們精心設計該功能,使其能夠高效實現在LUT和器件的Block RAM 中。我們充分利用FPGA 解決方案的靈活性,采用實現方案選項(如可采用128 位或256位密鑰,也可修改內核支持的虛擬SecY 數量)來設計內核。

新標準的另一個重要特性就是,MACsec 可收集數據包級的統計數據。系統管理員能夠了解有關信息(如多少數據包因為延遲而被拒收,或者因為無效解密密鑰或使用錯誤密鑰而未通過完整性檢查),并將這些統計數據與正確傳輸的數據包數量進行比較。

MACsec 標準可面向點對點應用提供精簡選項。這樣就無需采用CAM 從數據包中的顯式安全通道標識符和單點到多點操作的選擇方案中確定密鑰。我們的內核還可支持關聯于單個以太網的多個虛擬SecY,這樣,不同的密鑰就能用來加密從MAC 傳輸到不同目的地的數據。MACsec 標準將這種配置定義為多用戶局域網,因為這就像這些目的地位于不同以太網LAN 上一樣。該特性使得系統能夠通過使用不同密鑰加密輸出來對接收設備進行分區。

數據中心可能會采用多個SecY來創建虛擬分區,這樣客戶A 的數據就可通過唯一的加密密鑰與客戶B 的數據劃分開。

數據中心內部通信可根據需要進行組織來分隔選定的機架,進而提供虛擬隔離區。這種功能可保護數據完整性,并應對數據中心和云應用中的隔離問題。無論是意外錯誤連接還是惡意行為(見圖4),MACsec 系統都能檢測到未經認證的數據包,系統管理員可通過設置策略將其隔離或刪除。

?

圖4 – MACsec將拒絕通過錯誤連接抵達的數據包,無論是因為意外情況造成還是惡意行為導致。

所有數據加密和解密都在端口級進行。除了附加的MACsec 報頭和較少的額外時延,打開端口級加密不會增加開支,也不會對性能造成其它影響。

通過采用符合IEEE 802.1AE 要求的加密Ethernet Lecel 2 方案,設備廠商現在能用這些內核推動其系統特色化。基于云的用戶可能與其他用戶相互之間不信任,但他們現在能夠從MACsec 提供的數據機密大獲裨益,并且數據源認證功能可進一步保護他們的數據。

設備制造商則能選擇可用的IP 核來滿足1Gb 和10 Gb 以太網吞吐量的需求。

這種架構設計能通過Kintex 或Virtex FPGA 器件輕松實現10Gbps 的速度。在最壞情況下,該設計只需更改每個數據包的密鑰便可支持巨型幀和最小型數據包。內核符合全面規范要求,每個MACsec 內核都能支持各種常用的FPGA 產品系列。

配套提供源碼

Algotronix 采取了不同尋常的措施,即為所有許可的內核提供HDL源碼。這樣做的主要動機是支持客戶檢查,以便確保代碼不含病毒或特洛伊木馬代碼,而且不會強制進入非授權狀態或操作。有了源碼,就能降低客戶安全審核的成本和復雜性。此外,源碼可加速設計進程,因為工程師能夠方便地嘗試使用諸如加密、解密或加密/ 解密等不同配置參數和密鑰長度,并了解其各自仿真內核中的信號狀態。

您可對內核進行配置,通過實現較寬的數據路徑來提高吞吐量,或通過選擇較窄的數據寬度來最大程度地減小FPGA 封裝尺寸。擁有源碼還有其它更多優勢,包括更便于了解內核工作情況;也讓文檔記錄和歸檔變得更快捷方便。

此外,還配套提供了廣泛的驗證測試平臺,可幫助客戶在ModelSim等工具中確認操作是否正確。測試平臺包括MACsec 的行為模型和MACsec IP 核的自檢版本,能針對行為模型檢查可綜合硬件的輸出。這種自檢設計可在用戶仿真中實現實例化,便于測試實際用戶設計環境下的內核表現,并在錯誤驅動的情況下提供有用的診斷信息。

內核可提供許多選項,因此精確的資源數量將取決于您如何選擇參數,如數據速率、密鑰長度和所選SecY 數量以及其它。然而,賽靈思網站IP 部分列出的10G MACsec 內核采用6,638 個slice、20,916 個LUT 和53 個BRAM 塊。如需獲取許可證選項,敬請聯系Algotronix。

賽靈思低功耗 FPGA 與Algotronix MACsec 內核的完美結合為設備制造商實現產品差異化提供了高性能、低時延的解決方案。安全特性使得數據中心能夠確保其客戶機密,同時還可幫助安全管理員檢測并打擊惡意行為。

電子發燒友App

電子發燒友App

評論