本案例介紹了如何使用Silexica的SLX FPGA優化人臉檢測數據中心的OpenCL AI內核。

引言

FPGA正越來越多地被用作數據中心的協處理器。這一轉變背后的驅動力是利用FPGA的并行特性的AI應用。Xilinx Alveo系列加速器卡使用PCI Express接口連接到x86處理器,在這個領域非常流行。對于這些加速器卡的編程,你可以使用自上而下的方法,從頂級的C/C++和OpenCL應用程序開始,然后向低級別的內核工作,或者使用自下而上的方法,將內核塊編譯成Xilinx對象(.xo),然后可以在以后的階段連接成二進制。

與自頂向下的流相比,自底向上的流程有幾個優點。(1) 它允許將內核的設計、驗證和優化與主應用程序分開。(2) 它通過將設計分割成更小的組件,為內核的開發和優化提供更快的迭代周期。(3) 它有利于重復使用;一個(.xo)文件的集合可以像庫一樣被重復使用。

在本應用案例中,我們使用人臉檢測應用作為參考設計,展示設計者在使用Vitis自下而上流程時,如何使用SLX FPGA來優化內核。請注意,同樣的方法也適用于從頭開始設計內核或從Vitis HLS導入現有內核。

開發流程

創建該應用需要使用Silexica和Xilinx的以下開發工具。

● SLX FPGA版本2020.4-sp1● VitisLibraries 2020.2版● Vitis高級合成2020.2版

● Vitis統一軟件平臺2020.2版

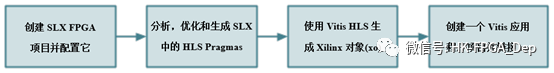

整個端到端流程如圖1所示。該流程從創建一個新的SLX項目開始。但是,如果您有一個現有的Vitis HLS項目,SLX FPGA可以直接導入它。

圖1:Vitis自底向上項目的SLX FPGA工作流程

一、創建并配置SLX FPGA項目

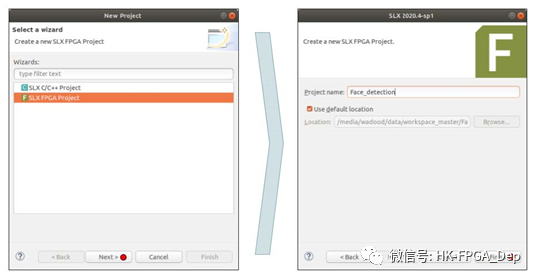

啟動SLX FPGA,點擊“New SLX project”圖標,啟動項目創建向導。創建一個新的SLX FPGA項目,如圖2所示。下一步是配置這個項目。

啟動SLX FPGA,點擊“New SLX project”圖標,啟動項目創建向導。創建一個新的SLX FPGA項目,如圖2所示。下一步是配置這個項目。

圖2:創建一個新的SLX FPGA項目

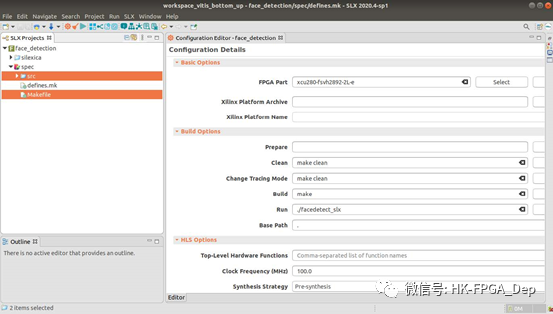

當你創建一個新的項目時,配置編輯器會自動出現,但你也可以通過點擊橙色的齒輪按鈕隨時調出它。如圖3所示,將你的應用程序源文件拖放到項目的spec文件夾中。在本案例中,我們從Rosette基準1中抽取人臉檢測應用。接下來,你需要指定FPGA部件號和構建選項。對于這個應用,我們的目標是Alveo U280 FPGA。在FPGA部件欄,選擇xcu280-fsvh2892-2L-e。要設置構建選項,輸入clean、build和run命令,如圖3所示。對于‘make’項目,如圖,請確認makefile沒有使用硬編碼編譯器,而是使用(CC)和(CXX)環境變量來分別引用C和C++編譯器。SLX將在不同的分析階段用其專有的編譯器覆蓋這些變量。Run命令執行testbench(也包括在基準套件中),以確保功能的正確性,也用于分析應用程序的動態行為。

圖3:配置一個新的SLX FPGA項目

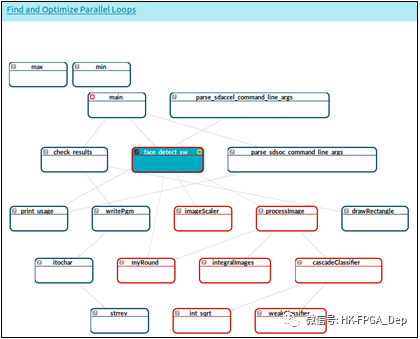

這些基本配置完成后,我們可以繼續為我們的應用程序選擇頂級硬件函數,并設置正確的接口。點擊“函數映射”按鈕,打開功能映射編輯器。如果你確定頂層硬件函數,檢查它的可綜合性問題,并使用函數映射編輯器中的右鍵菜單將其映射到FPGA上。或者,運行自動選擇FPGA功能,讓SLX自動選擇頂層的硬件函數。對于這個人臉識別應用,我們選擇face_detect_sw作為我們的頂級硬件函數。一旦正確選擇了頂層硬件函數,函數映射編輯器將看起來像圖4,所有映射到FPGA的函數將有一個紅色邊框。

這些基本配置完成后,我們可以繼續為我們的應用程序選擇頂級硬件函數,并設置正確的接口。點擊“函數映射”按鈕,打開功能映射編輯器。如果你確定頂層硬件函數,檢查它的可綜合性問題,并使用函數映射編輯器中的右鍵菜單將其映射到FPGA上。或者,運行自動選擇FPGA功能,讓SLX自動選擇頂層的硬件函數。對于這個人臉識別應用,我們選擇face_detect_sw作為我們的頂級硬件函數。一旦正確選擇了頂層硬件函數,函數映射編輯器將看起來像圖4,所有映射到FPGA的函數將有一個紅色邊框。

圖4:SLX FPGA函數映射編輯器

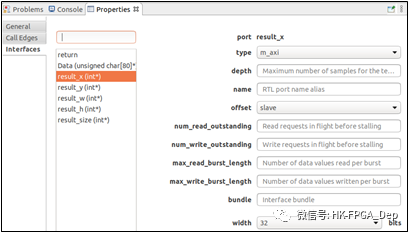

現在我們準備為這個函數選擇接口。在函數映射編輯器中選擇頂級硬件函數后,點擊properties標簽,用左側的菜單打開接口選擇,如圖5所示。為所有數組和指針接口選擇axi_m接口,為標量選擇s_axilite接口。這將生成在Alveo加速器卡上使用Xilinx對象所需的接口pragmas。此外,SLX的優化引擎現在意識到了接口限制,并相應地選擇了優化原則。

圖5:SLX FPGA接口選擇

在正確選擇了所有接口后,我們現在設置使用SLX FPGA優化和生成pragmas。

二、在SLX FPGA中生成HLS pragmas

生成HLS pragmas有兩個步驟:

1. 在FPGA中查找并并行化循環

2. 生成插入HLS注釋的代碼

在第一步中,SLX的優化引擎搜索可能的解決方案的設計空間,以確定最優的實用程序和參數集。設計空間包括:(1)循環的不同并行化選項,即針對不同展開因子采用流水線或unroll;(2)數組的多維分割和重構選項(完全分割或循環分割);

(3)函數層次結構:內聯或阻塞。

對于這個特定的例子,這將導致大約1.32 x e19的設計點,SLX的優化引擎將在70秒內收斂到一個解決方案。

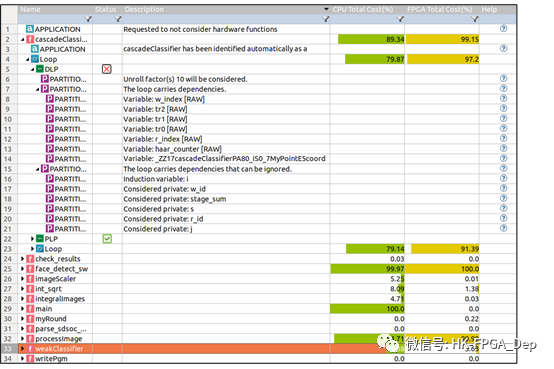

圖6:SLX FPGA提示視圖

圖6顯示了SLX FPGA提示視圖。提示視圖中的第四列和第五列顯示了應用程序中不同函數和循環的CPU總成本和FPGA總成本。FPGA總成本是對特定功能或回路的延遲估計。這對于幫助開發人員集中精力進行優化特別有用。例如,第33行(圖6)上的weekClassifier函數在純軟件實現中花費24.4%的CPU時間。然而,它對FPGA實現中的關鍵路徑延遲的貢獻僅為3.63%。

相比之下,在純軟件實現中,cascadeClassifier函數的第4行上的循環(圖6)花費了79.9%的CPU時間,但貢獻了97.2%的FPGA關鍵路徑延遲。提示視圖還突出顯示了攜帶依賴關系的關鍵循環。請注意,SLX FPGA不認為所有的lcd都是相等的,并將可以忽略的lcd(例如,歸納和縮減變量)從關鍵的lcd中分離出來。這些信息可以幫助開發人員節省時間,使他們能夠將精力集中在FPGA實現中真正重要的應用程序部分。

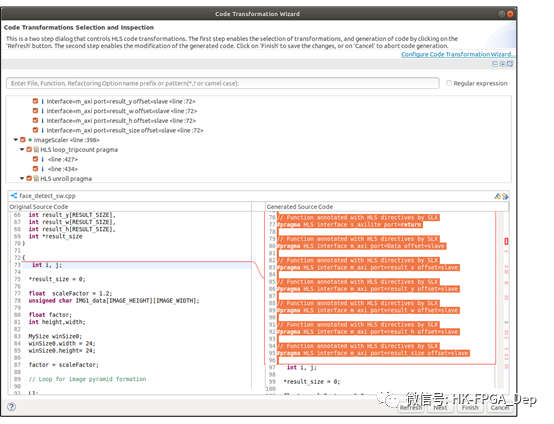

圖7:顯示自動編譯插入的SLX FPGA代碼生成向導單擊“Generate HLS Code”按鈕 將打開代碼轉換向導,如圖7所示。在這里,用戶可以檢查生成的代碼與原始版本的代碼并選擇/取消代碼生成的pragmas,以便對實現進行微調。

三、在Vitis應用項目中導入Xilinx對象

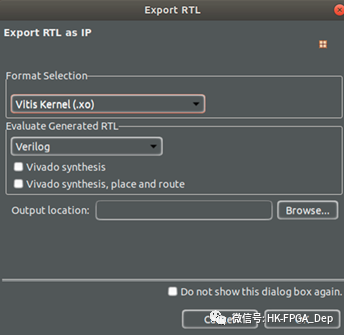

在一個SLX FPGA項目的hls文件夾包含一個Vitis hls項目SLX優化的源代碼。我們使用VitisHLS打開這個項目,并將RTL導出為Xilinx對象,如圖8所示。在導出到Vitis之前,我們需要添加Extern“C”包裝器以確保C鏈接。

在一個SLX FPGA項目的hls文件夾包含一個Vitis hls項目SLX優化的源代碼。我們使用VitisHLS打開這個項目,并將RTL導出為Xilinx對象,如圖8所示。在導出到Vitis之前,我們需要添加Extern“C”包裝器以確保C鏈接。

圖8:從Vitis HLS導出Xilinx對象

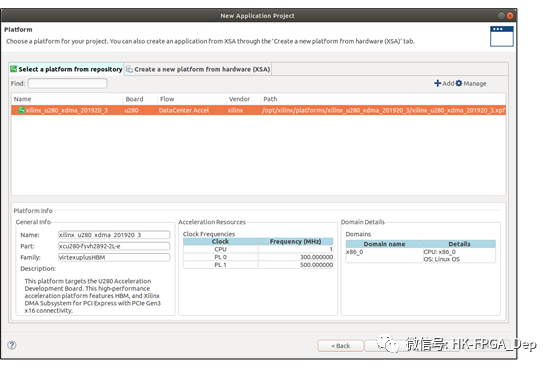

在Vitis工作空間中,創建一個新的應用程序,使用一個alveso U280卡作為目標設備,如圖9所示。

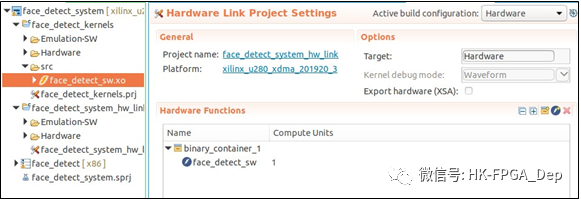

圖9:在Vitis統一平臺中創建應用程序項目創建項目之后,我們將.xo文件導入內核的src文件夾,如圖10所示。導入.xo文件后,單擊“添加硬件功能”按鈕,并選擇列表face_detect_sw。

圖10:在Vitis應用程序項目中導入內核開發人員現在可以利用加速的face_detect_sw內核創建更廣泛的應用程序,該應用程序運行在x86主機上。

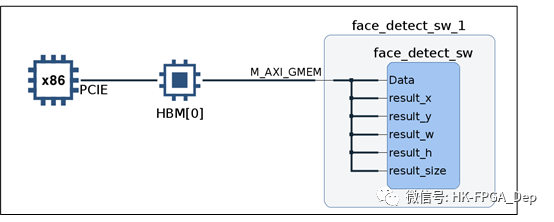

圖11:Vitis Analyzer系統圖

性能改進

在綜合設計的基礎上,對SLX優化后的內核與未優化前的內核的性能和資源利用率進行了比較。對于這個特殊的設計,我們允許SLX FPGA使用選定設備上的所有可用資源;但是,如果有必要,還可以添加其他約束。表1顯示了結果的摘要。我們發現LUT增加3倍,延遲減少7.8倍,FF增加2.4倍,DSP塊增加2.7倍。對于alveso卡來說,這種資源利用率的增加并不是一個大問題,因為所有資源的利用率仍然低于5%。如果需要更高的性能,SLXFPGA中可以提供大量額外的分析功能,以幫助指導設計者更快更有效地重構他們的代碼。

結論

本案例展示了如何利用Vitis自下而上的內核流程,將SLX FPGA用于優化針對PCIe連接Alveo卡的內核。在這個例子中,SLX FPGA能夠減少一個常用的人工智能內核的延遲,用于人臉檢測。該方法可應用于大多數基于賽靈思的數據中心應用,包括亞馬遜F1實例。無論是從頭開始開發應用,還是重復使用現有的設計并根據需求進行定制,都可以應用這種方法。

原文標題:虹科方案 | 使用HLS優化人臉識OpenCL AI內核

文章出處:【微信公眾號:FPGA技術支持】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1643文章

21964瀏覽量

614110 -

AI

+關注

關注

87文章

34233瀏覽量

275392 -

Vitis

+關注

關注

0文章

147瀏覽量

7828

原文標題:虹科方案 | 使用HLS優化人臉識OpenCL AI內核

文章出處:【微信號:HK-FPGA_Dep,微信公眾號:FPGA技術支持】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

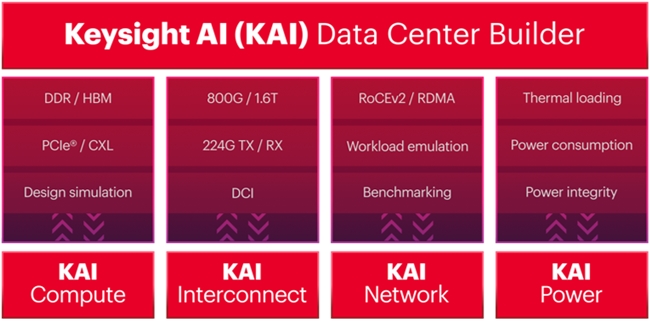

是德科技推出AI數據中心構建器以驗證和優化網絡架構和主機設計

適用于數據中心和AI時代的800G網絡

華為全新升級星河AI數據中心網絡

優化800G數據中心:高速線纜、有源光纜和光纖跳線解決方案

Cadence顛覆AI數據中心設計

FPGA+AI王炸組合如何重塑未來世界:看看DeepSeek東方神秘力量如何預測......

韓國將建全球最大AI數據中心

當我問DeepSeek AI爆發時代的FPGA是否重要?答案是......

亞馬遜云科技發布全新數據中心組件

Meta AI數據中心網絡用了哪家的芯片

AI時代,我們需要怎樣的數據中心?AI重新定義數據中心

如何使用SLX FPGA優化人臉檢測數據中心的OpenCL AI內核?

如何使用SLX FPGA優化人臉檢測數據中心的OpenCL AI內核?

評論