在使用MAX II給用戶做替代模塊的過程中,出現了一些很詭異的狀況,這些狀況也往往發生在上電伊始。因此,特權同學特別的花心思好好研究了一下MAX II的上電過程和簡單的RC復位。當然,最終問題的解決其實和本文要說的上電過程和復位并沒有什么關系,但仍然不妨礙好好的梳理一下這些看似簡單卻又非常基礎的知識點。

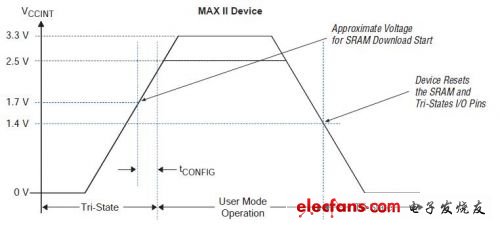

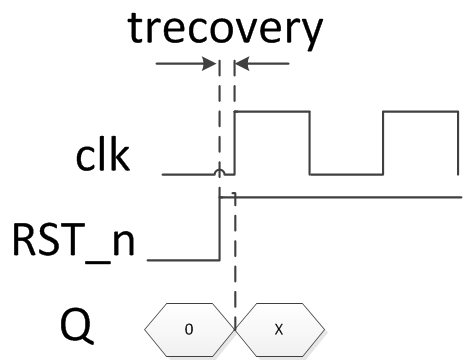

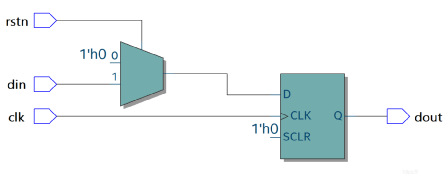

首先來說MAX II的上電過程,在handbook中已有較詳細的說明。如圖1所示,在VCCINT從0V不斷上升的過程中,一旦買過1.7V的閘值電壓后,MAX II內部便開始進行邏輯的配置,大約需要Tconfig時間,這個時間長短取決于邏輯資源多少。Tconfig時間內對外IO的狀態也是可以通過Quartus II選項進行配置的,在這個時間后,器件便進入正常的用戶模式。

圖1 MAX II的上電過程圖

對于前面提到的Tconfig時間,不同邏輯資源的器件稍有區別,如表1所示。

表1 不同邏輯資源的器件的Tconfig時間的區別

接下來要討論復位的問題,原文在圖1的下方有一段注釋:

After SRAM configuration, all registers in the device are cleared and released into user function before I/O tri-states are released. To release clears after tri-states are released, use the DEV_CLRn pin option. To hold the tri-states beyond the power-up configuration time, use the DEV_OE pin option.

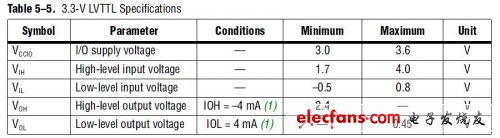

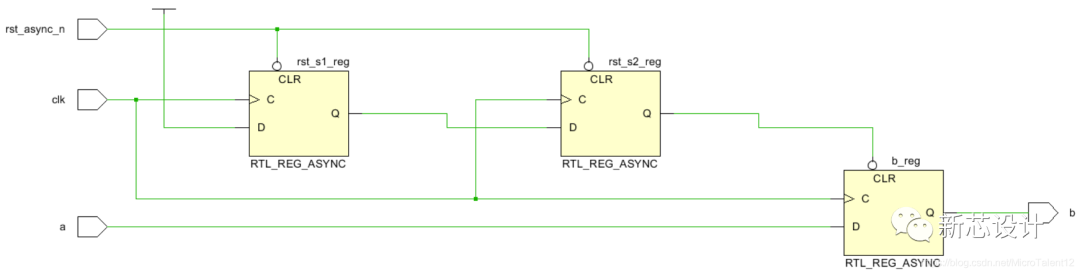

簡單的說,在CPLD內部配置完成后,所有寄存器通常是出于清零狀態,IO腳進入用戶模式。而用戶如果希望這時候內部各個寄存器的狀態處于可控或者特定的狀態(尤其當其值不一定是清零的狀態),那么用戶可以使用器件提供的專用管腳DEV_CLRn或DEV_OE來達到所期望的效果。一般而言,使用其他的IO(當然最好是全局時鐘輸入管腳)作為內部復位管腳也沒問題,反正是通過在Tconfig時間過后的一段初始時間內繼續使器件處于復位或者期望的狀態即可。這里也只討論復位的狀況,如表2所示,MAX II的3.3V LVTTL電平的輸入高電平也是>1.7V。

表2 復位的狀況

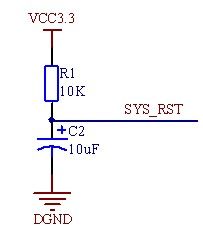

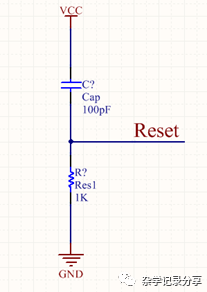

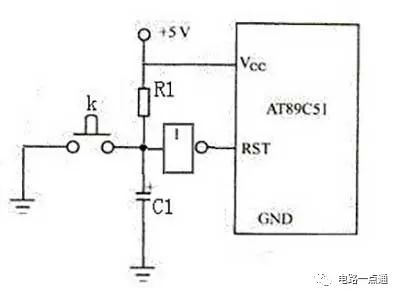

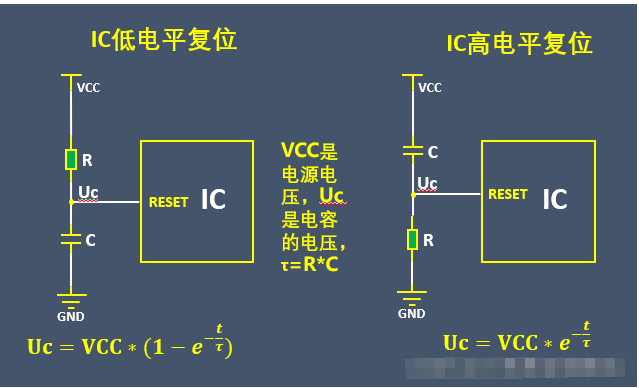

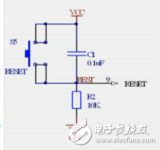

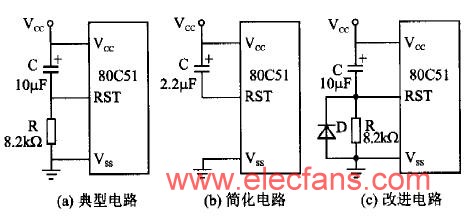

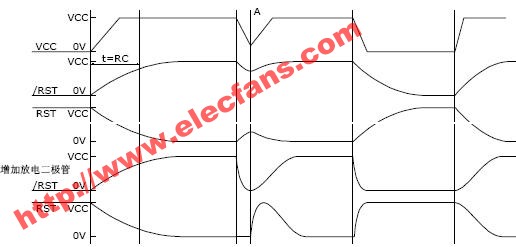

一個最簡單的低電平復位電路如圖2所示。

圖2 低電平復位電路

這個電路在上電初始過程中,可以起到延緩SYS_RST信號電壓從DGND突變到VCC3.3。其延時時間的計算方法如下:

V0 為電容上的初始電壓值,初上電時通常該電壓值為0V。

V1 為電容最終可充到或放到的電壓值,通常為電源電壓VCC。

Vt 為t時刻電容上的電壓值,即RESET信號的電壓值。

則從t0時刻到電壓到達Vt所需要的時間為:t = RC*Ln[(V1-V0)/(V1-Vt)]

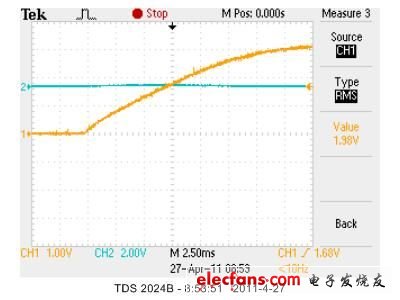

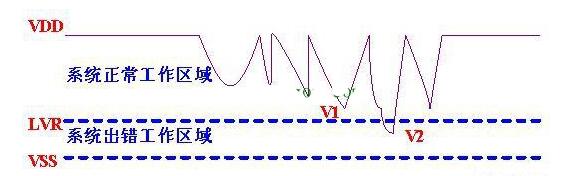

特權同學也簡單的對公示做了一些驗證。這里取C=1uF,R=10k,V0=0,V1=VCC,Vt=1.7V。那么計算到的延時值約為7.24ms。而實際檢測到的波形如圖3所示。約為7.25ms,和理論值很接近。

圖3 實際檢測到的波形圖

電子發燒友App

電子發燒友App

評論