引言

??本文主要是提供了 ASIC 設(shè)計中關(guān)于復(fù)位技術(shù)相關(guān)的概念和設(shè)計。

一、同步復(fù)位 Sync

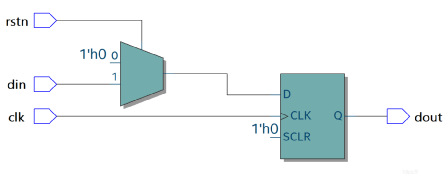

??當(dāng)時鐘上升沿檢測到復(fù)位信號時,執(zhí)行復(fù)位操作(有效的時鐘沿是前提)。

always @( posedge clk )begin

if(!rst_n)

b <= 0;

else

b <= a;

end

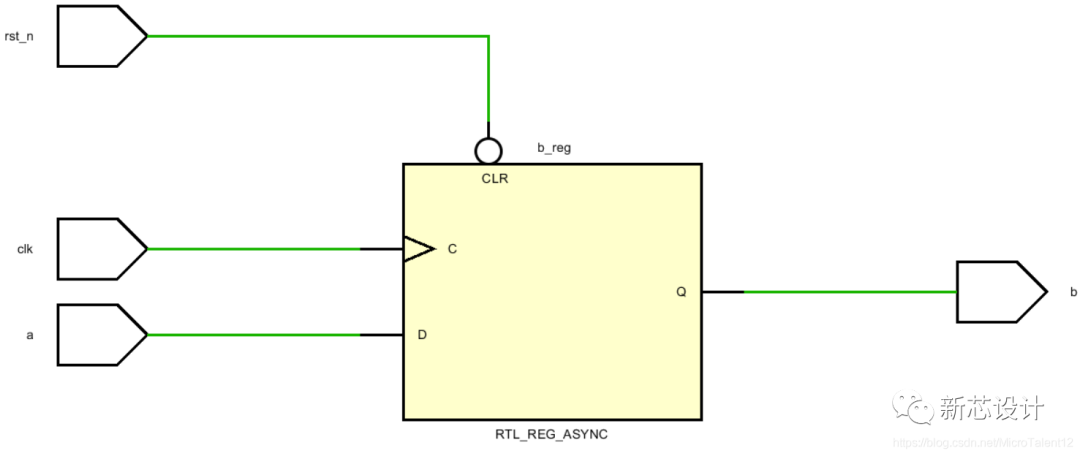

同步復(fù)位的 RTL 電路圖

優(yōu)點

- 有利于仿真器的仿真;

- 可以使所設(shè)計的系統(tǒng)成為 100% 的同步時序電路,有利于時序分析,而且可綜合出較高的 Fmax;

- 由于只在時鐘有效電平到來時才有效,所以可以濾除高于時鐘頻率的復(fù)位毛刺。

缺點

- 復(fù)位信號的有效時長必須大于時鐘周期,才能真正被系統(tǒng)識別并完成復(fù)位任務(wù),同時還要考慮諸如 Clock Skew、組合邏輯路徑延時、復(fù)位延時等因素;

- 由于大多數(shù)的邏輯器件的目標庫內(nèi)的 DFF 都只有異步復(fù)位 SR 端口,所以,倘若采用同步復(fù)位的話,綜合器就會在寄存器的數(shù)據(jù)輸入端口上插入組合邏輯,這樣就會一方面額外增加 FPGA 內(nèi)部的邏輯資源,另一方面也增加了相應(yīng)的組合邏輯門時延。

二、異步復(fù)位 ASync

??無論時鐘上升沿是否到來,只要復(fù)位信號有效,就執(zhí)行復(fù)位操作。

always @( posedge clk or negedge rst_n )begin

if(!rst_n)

b <= 0;

else

b <= a;

end

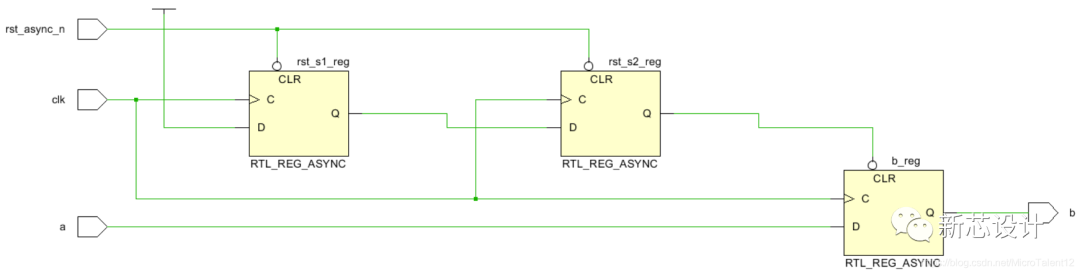

異步復(fù)位的 RTL 電路圖

優(yōu)點

- 大多數(shù)目標器件庫的 DFF 都有異步復(fù)位 SR 端口,直接使用的話,就不需要額外的組合邏輯,從而節(jié)省資源;

- 設(shè)計相對簡單;

- 異步復(fù)位信號識別方便(電路在任何情況下都能復(fù)位而不管是否有時鐘出現(xiàn))。

缺點

- 最大的問題在于它屬于異步邏輯,問題出現(xiàn)在復(fù)位釋放時,而不是有效時,如果復(fù)位釋放接近時鐘有效沿,則觸發(fā)器的輸出可能進入亞穩(wěn)態(tài)(此時 clk 檢測到的 rst_n 的狀態(tài)就會是一個亞穩(wěn)態(tài),即是 0 是 1 是不確定的),從而導(dǎo)致復(fù)位的失敗;

- 可能因為噪聲或者毛刺造成虛假復(fù)位信號(比如以前的游戲機玩到一半突然復(fù)位)(注意:時鐘端口、清零和置位端口對毛刺信號十分敏感,任何一點毛刺都可能會使系統(tǒng)出錯,因此判斷邏輯電路中是否存在冒險以及如何避免冒險是設(shè)計人員必須要考慮的問題);

- 靜態(tài)時序分析比較困難;

- 對于 DFT 設(shè)計,如果復(fù)位信號不是直接來自于 I/O 引腳,在 DFT 掃描和測試時,復(fù)位信號必須被禁止,所以還要消耗額外的同步電路。

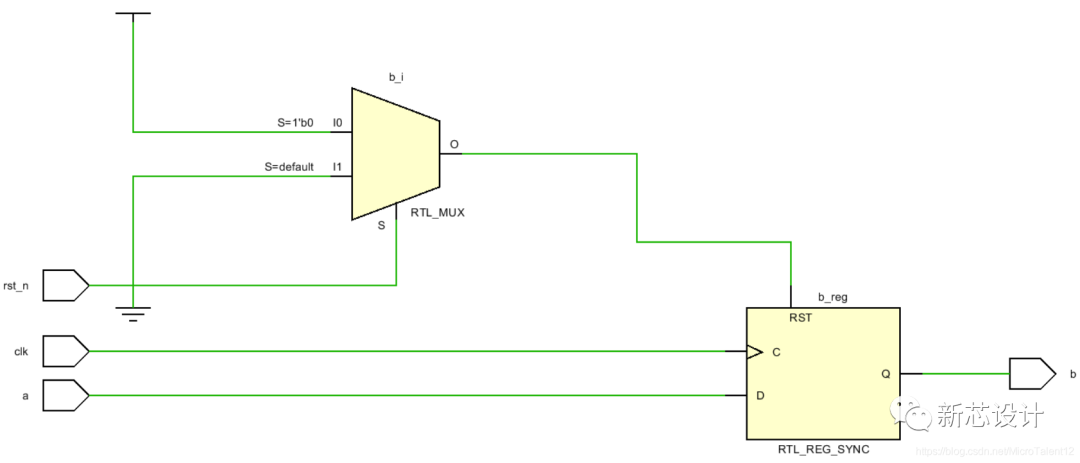

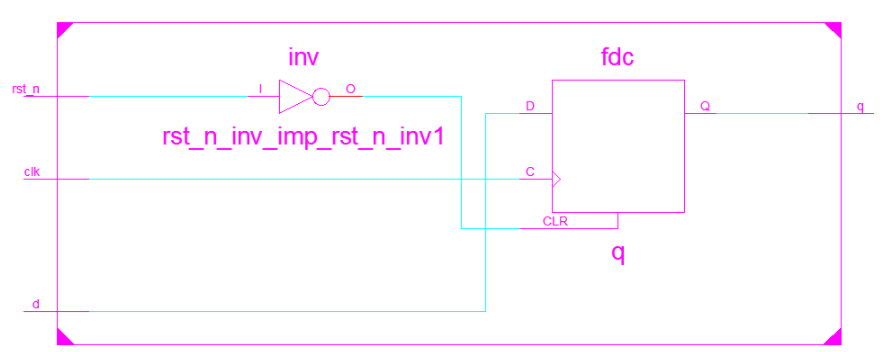

三、異步復(fù)位、同步釋放

??推薦異步復(fù)位、同步釋放的方式,并且復(fù)位信號為低電平有效:異步復(fù)位、同步釋放指的是復(fù)位信號的到來與撤除都與 clk 無關(guān),但是復(fù)位信號的撤除是在下一個 clk 到來之后才執(zhí)行,也就是復(fù)位信號 rst_sync_n 由高到低時實現(xiàn)異步復(fù)位。電路的目的是防止復(fù)位信號的撤除時可能產(chǎn)生的亞穩(wěn)態(tài)。

珍貴的手繪圖

??對于同步釋放,這個是關(guān)鍵,即當(dāng)復(fù)位信號 rst_async_n 撤除時(由低到高),由于雙緩沖電路(雙寄存器)的作用,rst_sync_n 不會隨著 rst_async_n 的撤除而撤除。假設(shè) rst_async_n 撤除時發(fā)生在 clk 上升沿,如果不加此電路則可能發(fā)生亞穩(wěn)態(tài)事件。

??但是,加上此電路之后,假設(shè)第一級 D 觸發(fā)器 clk 上升沿時 rst_async_n 正好撤除,(第一個 DFF 此時是出于亞穩(wěn)態(tài)的,假設(shè)此時識別到高電平;若是識別到低電平,則增加一個 Delay)則 DFF1 輸出高電平,此時第二級觸發(fā)器也會更新輸出,但是輸出值為前一級觸發(fā)器 clk 來之前時的 Q1 輸出狀態(tài)。顯然,Q1 之前為低電平,所以第二級觸發(fā)器輸出保持復(fù)位低電平,直到下一個 clk 來之后,才隨著變?yōu)楦唠娖剑赐结尫拧?/p>

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

rst_r <= 2'b00;

else

rst_r <= {rst_r[0],1'b1};

end

assign sys_rst_n = rst_r[1];

always @(posedge clk or negedge sys_rst_n)begin

if(!sys_rst_n)

b <= 1'b0;

else

b <= a;

end

異步復(fù)位、同步釋放的 RTL 電路圖

-

asic

+關(guān)注

關(guān)注

34文章

1242瀏覽量

121970 -

時鐘

+關(guān)注

關(guān)注

11文章

1879瀏覽量

132827 -

SYNC

+關(guān)注

關(guān)注

1文章

15瀏覽量

11700 -

同步復(fù)位

+關(guān)注

關(guān)注

0文章

27瀏覽量

10838 -

異步復(fù)位

+關(guān)注

關(guān)注

0文章

47瀏覽量

13470

發(fā)布評論請先 登錄

異步復(fù)位與同步復(fù)位的綜合后電路圖講解

Xilinx FPGA異步復(fù)位同步釋放—同步后的復(fù)位該當(dāng)作同步復(fù)位還是異步復(fù)位?

同步復(fù)位和異步復(fù)位有什么聯(lián)系與區(qū)別,優(yōu)缺點!

如何區(qū)分同步復(fù)位和異步復(fù)位?

Xilinx FPGA的同步復(fù)位和異步復(fù)位

同步復(fù)位和異步復(fù)位的優(yōu)缺點和對比說明

復(fù)位電路的同步復(fù)位和異步復(fù)位講解

同步復(fù)位和異步復(fù)位講解

同步復(fù)位和異步復(fù)位講解

評論