?

表1 PE3293(以20腳TSSOP封裝為例)的引腳定義

??? PLL1(RF)的VCO頻率fin1的大小與fr的值有關(guān),它們之間的關(guān)系如下:

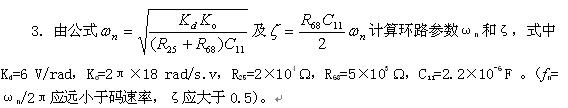

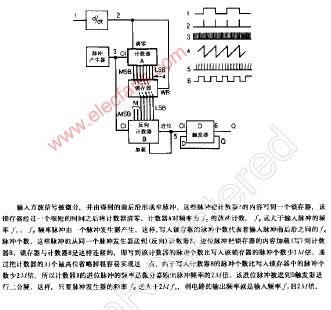

??? 數(shù)據(jù)輸入端Data輸入的數(shù)據(jù)在時鐘輸入Clock 的上升沿逐次移入21bit的移位寄存器且MSB(M16)在先,因此,當(dāng)LE為高時,數(shù)據(jù)送入由圖4所示的最后2位地址位所決定的21bit移位寄存器的相應(yīng)地址中。比如,當(dāng)程序?qū)τ嫈?shù)器A1進(jìn)行控制 時,送入寄存器的最后兩比特(S0, S1)應(yīng)為(1,1),計數(shù)器A1中的5比特位可以按表2設(shè)置。因此,在正常情況下,即使不用PLL2?IF?? S16也應(yīng)設(shè)為0。應(yīng)注意的是,PE3293的工作模式、鑒相器極性和功率控制均可以由C10~C14和C20~C24來控制。

表2 PE3293的計數(shù)器設(shè)計表

5 結(jié)語

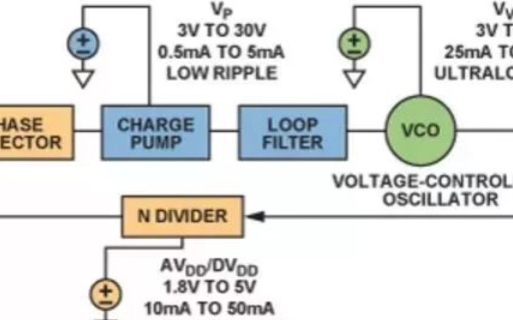

摘要:在無線通信中,降低頻率合成器的相位噪聲和抑制其相應(yīng)的寄生輸出,一直是設(shè)計者追求的目標(biāo)。PE3293是Peregrine公司生產(chǎn)的高性能1.8GHz/550MHz雙模整數(shù)分頻集成鎖相環(huán)電路,它具有超低的寄生輸出。文中介紹了PE3293的特點功能和組成原理,給出了PE3293在頻率綜合器設(shè)計中的應(yīng)用電路。

關(guān)鍵詞:頻率合成器;相位噪聲;寄生輸出;PLL;PE3293

1 引言

同時頻率切換時間和寄生輸出的抑制對系統(tǒng)也很重要。頻率合成器作為一種高質(zhì)量的信號源,與電子系統(tǒng)的性能有很大關(guān)系。在通信系統(tǒng)中,使用高穩(wěn)定的信號源,可以充分利用頻率資源。實際上,在電子對抗、導(dǎo)航等電子系統(tǒng)中,高指標(biāo)的信號源會給系統(tǒng)帶來良好的性價比,從而為系統(tǒng)設(shè)計師提供可靠的技術(shù)保障。

2 PE3293的特點功能

表1 PE3293(以20腳TSSOP封裝為例)的引腳定義

| 序? 號 | 名? 稱 | 類? 型 |

功?? 能?? 描?? 述 |

| 1 | N/C | 不連接 | |

| 2 | VDD | 電源,2.7~3.3V,需用一個電容就近旁路接地 | |

| 3 | CP1 | 輸出 | PLL1內(nèi)部的脈沖成形輸出,用作外部VCO的輸入驅(qū)動 |

| 4 | GND | 地端 | |

| 5 | fin1 | 輸入 | 從PLL1(RR)VCO來的預(yù)分頻器輸入,最大頻率為1.8GHz |

| 6 | Dec1 | PLL1的電源去耦端,有必要用一個電容就近接地 | |

| 7 | VDD1 | PLL1預(yù)分頻器的電源,一般經(jīng)3.3kΩ的電阻連到VDD | |

| 8 | fr | 輸入 | 參考頻率輸入 |

| 9 | GND | 地端 | |

| 10 | f0LD | 輸出 | 復(fù)用器輸出,包括PLL1和PLL2主計數(shù)器或參考計數(shù)器輸出/時鐘檢測信號,以及移位寄存器移出數(shù)據(jù) |

| 11 | Clock | 輸入 | CMOS時鐘輸入,在時鐘信號的上升沿,各種計數(shù)器的串行數(shù)據(jù)將送入21bit的移位寄存器 |

| 12 | Data | 輸入 | 二進(jìn)制串行數(shù)據(jù)輸入,為CMOS輸入數(shù)據(jù),MSB先,2bit的LSB為控制比特 |

| 13 | LE | 輸入 | 負(fù)載使能CMOS入,當(dāng)LE為高時,21bit的串行移位移位寄存器中的數(shù)據(jù)字將被送入相應(yīng)的四個鎖存器之一中(由控制比特決定) |

| 14 | VDD2 | 輸出 | PLL1預(yù)分頻器的電源,使用時經(jīng)3.3kΩ的電阻連到VDD0 |

| 15 | Dec2 | 輸出 | PLL1的電源去耦端,有必要用一個電容就近接地 |

| 16 | fin2 | 輸入 | 從PLL1(IF)VCO來的預(yù)分頻器輸入,最大頻率為500MHz |

| 17 | GND | 地端 | |

| 18 | CP2 | 輸出 | PLL1內(nèi)部的脈沖成形輸出,用作外部VCO的輸入驅(qū)動 |

| 19 | VDD | 2.7~3.3V電源,需經(jīng)一個電容就近接地 | |

| 20 | VDD | 電源,2.7~3.3V,需經(jīng)一個電容就近接地 |

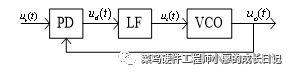

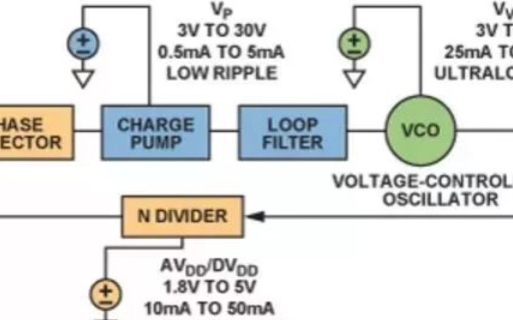

3 PE3293的組成原理

??? PLL1(RF)的VCO頻率fin1的大小與fr的值有關(guān),它們之間的關(guān)系如下:

??? 數(shù)據(jù)輸入端Data輸入的數(shù)據(jù)在時鐘輸入Clock 的上升沿逐次移入21bit的移位寄存器且MSB(M16)在先,因此,當(dāng)LE為高時,數(shù)據(jù)送入由圖4所示的最后2位地址位所決定的21bit移位寄存器的相應(yīng)地址中。比如,當(dāng)程序?qū)τ嫈?shù)器A1進(jìn)行控制 時,送入寄存器的最后兩比特(S0, S1)應(yīng)為(1,1),計數(shù)器A1中的5比特位可以按表2設(shè)置。因此,在正常情況下,即使不用PLL2?IF?? S16也應(yīng)設(shè)為0。應(yīng)注意的是,PE3293的工作模式、鑒相器極性和功率控制均可以由C10~C14和C20~C24來控制。

表2 PE3293的計數(shù)器設(shè)計表

| 分頻比 | MSB | LSB | 地址位 | ||||

| S11 | S10 | S9 | S8 | S7 | S1 | S0 | |

| A14 | A13 | A12 | A11 | A10 | 1 | 1 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

| 2 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

| - | - | - | - | - | - | 1 | 1 |

| 31 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

5 結(jié)語

- 鎖相環(huán)(86948)

相關(guān)推薦

高性能鎖相環(huán)PE3293及其應(yīng)用

摘要:在無線通信中,降低頻率合成器的相位噪聲和抑制其相應(yīng)的寄生輸出,一直是設(shè)計者追求的目標(biāo)。PE3293是Peregrine公司生產(chǎn)的高性能1.8GHz/550MHz雙模整數(shù)分頻

2006-03-11 13:33:39 486

486

486

486

鎖相環(huán)相位噪聲與環(huán)路帶寬的關(guān)系是什么

電荷泵鎖相環(huán)的基本原理是什么?電荷泵鎖相環(huán)的噪聲模型與相位噪聲特性是什么?電荷泵鎖相環(huán)的相位噪聲與環(huán)路帶寬關(guān)系是什么?

2021-06-07 06:57:53

什么是鎖相環(huán) 鎖相環(huán)的組成 鎖相環(huán)選型原則有哪些呢?

大家都知道鎖相環(huán)很重要,它是基石,鎖相環(huán)決定了收發(fā)系統(tǒng)的基礎(chǔ)指標(biāo),那么如此重要的鎖相環(huán)選型原則有哪些呢?

2023-08-01 09:37:05 672

672

672

672

鎖相環(huán)

鎖相環(huán)英文為PLL,即PLL鎖相環(huán)。可以分為模擬鎖相環(huán)和數(shù)字鎖相環(huán)。兩種分類的鎖相環(huán)原理有較大區(qū)別,通過不同的鎖相環(huán)電路實現(xiàn)不同的功能。

2011-10-26 12:40:28

模擬鎖相環(huán)和數(shù)字鎖相環(huán)區(qū)別

模擬鎖相環(huán)和數(shù)字鎖相環(huán)的主要區(qū)別在于它們的控制方式不同。模擬鎖相環(huán)是通過模擬電路來控制頻率和相位,而數(shù)字鎖相環(huán)是通過數(shù)字信號處理技術(shù)來控制頻率和相位。此外,模擬鎖相環(huán)的精度較低,而數(shù)字鎖相環(huán)的精度較高。

2023-02-15 13:47:53 2765

2765

2765

2765鎖相環(huán)(PLL),鎖相環(huán)(PLL)是什么意思

鎖相環(huán)(PLL),鎖相環(huán)(PLL)是什么意思

PLL的概念

我們所說的PLL。其

2010-03-23 10:47:48 5913

5913

5913

5913如何使用FPGA實現(xiàn)高性能全數(shù)字鎖相環(huán)的設(shè)計

本文提出了一種適用范圍廣泛的全數(shù)字鎖相環(huán)(ADPLL)實現(xiàn)方法.在鎖相環(huán)輸入頻率未知的情況下,實現(xiàn)鎖相鎖頻功能。本文從全數(shù)字鎖相環(huán)的基本實現(xiàn)方式入手.進(jìn)行改進(jìn),并使用VH DL語言建模,使用FPGA進(jìn)行驗證。

2021-01-26 15:03:00 65

65

65

65如何使用FPGA實現(xiàn)高性能全數(shù)字鎖相環(huán)的設(shè)計

本文提出了一種適用范圍廣泛的全數(shù)字鎖相環(huán)(ADPLL)實現(xiàn)方法.在鎖相環(huán)輸入頻率未知的情況下,實現(xiàn)鎖相鎖頻功能。本文從全數(shù)字鎖相環(huán)的基本實現(xiàn)方式入手.進(jìn)行改進(jìn),并使用VH DL語言建模,使用FPGA進(jìn)行驗證。

2021-01-26 15:03:00 18

18

18

18數(shù)字鎖相環(huán)(DPLL),數(shù)字鎖相環(huán)(DPLL)是什么?

數(shù)字鎖相環(huán)(DPLL),數(shù)字鎖相環(huán)(DPLL)是什么?

背景知識:

隨著數(shù)字電路技術(shù)的發(fā)展,數(shù)字鎖相環(huán)在調(diào)制解調(diào)、頻率合成、FM 立體聲解碼、彩色副

2010-03-23 15:06:21 5312

5312

5312

5312軟件鎖相環(huán)的設(shè)計與應(yīng)用

根據(jù)虛擬無線電技術(shù)的特點和鎖相環(huán)的基本原理,提出一種適于計算機(jī)軟件化實現(xiàn)的鎖相環(huán)數(shù)學(xué)模型,分析不同參數(shù)對鎖相環(huán)捕獲和跟蹤性能的影響,得出不同情況下參數(shù)設(shè)定的基

2008-08-15 12:36:19 98

98

98

98鎖相環(huán)是如何實現(xiàn)倍頻的?

鎖相環(huán)是如何實現(xiàn)倍頻的?? 鎖相環(huán)(Phase Locked Loop, PLL)是一種電路,用于穩(wěn)定和恢復(fù)輸入信號的相位和頻率。它可以廣泛應(yīng)用于通信、計算機(jī)、音頻等領(lǐng)域中。其中一個重要的應(yīng)用就是

2023-09-02 14:59:37 386

386

386

386鎖相環(huán)原理

鎖相環(huán)原理

鎖相環(huán)路是一種反饋電路,鎖相環(huán)的英文全稱是Phase-Locked Loop,簡稱PLL。其作用是使得電路上的時鐘和某一外部時鐘的相位同步。因鎖相環(huán)可以

2007-08-21 14:46:04 4689

4689

4689

4689模擬鎖相環(huán),模擬鎖相環(huán)原理解析

模擬鎖相環(huán),模擬鎖相環(huán)原理解析

背景知識:

鎖相技術(shù)是一種相位負(fù)反饋控制技術(shù),它利用環(huán)路的反饋原理來產(chǎn)生新的頻率點。它的主要

2010-03-23 15:08:20 5716

5716

5716

5716鎖相環(huán)PLL的基礎(chǔ)知識

鎖相環(huán) (PLL) 電路存在于各種高頻應(yīng)用中,從簡單的時鐘清理電路到用于高性能無線電通信鏈路的本振 (LO),再到矢量網(wǎng)絡(luò)分析儀 (VNA) 中的超快速開關(guān)頻率合成器。本文解釋了鎖相環(huán)電路的一些構(gòu)建模塊,并參考了每種應(yīng)用,以幫助指導(dǎo)新手和鎖相環(huán)專家導(dǎo)航器件選擇以及每種不同應(yīng)用固有的權(quán)衡取舍。

2022-12-23 14:03:54 2293

2293

2293

2293

模擬鎖相環(huán)應(yīng)用實驗

一、實驗?zāi)康?、掌握模擬鎖相環(huán)的組成及工作原理。2、學(xué)習(xí)用集成鎖相環(huán)構(gòu)成鎖相解調(diào)電路。3、學(xué)習(xí)用集成鎖相環(huán)構(gòu)成鎖相倍頻電路。

二、鎖相環(huán)路的基本原理

2009-03-22 11:44:37 124

124

124

124德州儀器推出業(yè)內(nèi)具有集成壓控振蕩器的最高性能鎖相環(huán)

德州儀器推出了業(yè)內(nèi)具有集成壓控振蕩器(VCO)的最高性能鎖相環(huán)(PLLs)。

2020-05-18 10:41:41 815

815

815

815詳解FPGA數(shù)字鎖相環(huán)平臺

一、設(shè)計目標(biāo) 基于鎖相環(huán)的理論,以載波恢復(fù)環(huán)為依托搭建數(shù)字鎖相環(huán)平臺,并在FPGA中實現(xiàn)鎖相環(huán)的基本功能。 在FPGA中實現(xiàn)鎖相環(huán)的自動增益控制,鎖定檢測,鎖定時間、失鎖時間的統(tǒng)計計算,多普勒頻偏

2017-10-16 11:36:45 18

18

18

18鎖相環(huán)技術(shù)在頻率跟蹤中的應(yīng)用研究

本文介紹鎖相環(huán)及其頻率跟蹤的基本原理,給出二階鎖相環(huán)和四階鎖相環(huán)的設(shè)計依據(jù)。在此基礎(chǔ)上,對四階鎖相環(huán)實現(xiàn)頻率跟蹤的轉(zhuǎn)換時間進(jìn)行了仿真,就如何減小頻率跟蹤的轉(zhuǎn)換時間

2010-07-29 16:28:14 42

42

42

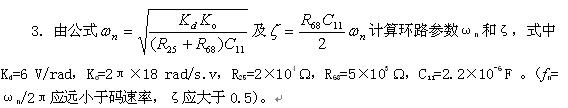

42鎖相環(huán)設(shè)計舉例

鎖相環(huán)設(shè)計舉例:鎖相環(huán)設(shè)計主要包括:確定所需環(huán)的類型,選擇適當(dāng)?shù)膸挘赋鱿M姆€(wěn)定度。下面將舉例說明要滿足這些設(shè)計要求而常用的基本方法。

2009-09-05 08:51:42 101

101

101

101鎖相環(huán)(PLL)的工作原理及應(yīng)用

鎖相環(huán)路是一種反饋控制電路,簡稱鎖相環(huán)(PLL,Phase-Locked Loop)。鎖相環(huán)的特點是:利用外部輸入的參考信號控制環(huán)路內(nèi)部振蕩信號的頻率和相位。

2022-03-29 09:54:55 10729

10729

10729

10729并網(wǎng)逆變器鎖相環(huán)設(shè)計

直接影響到逆變器的性能。如何利用DSP等數(shù)字芯片,設(shè)計出一個可以克服各種電網(wǎng)畸變及故障的軟件鎖相環(huán),是當(dāng)今科學(xué)研究的熱點問題。 本文首先論述的鎖相環(huán)技術(shù)的發(fā)展歷史及前景,簡單闡述了傳統(tǒng)的鎖相環(huán)技術(shù),指出了它們的缺點并

2017-12-08 11:12:07 23

23

23

23基于FPGA的自適應(yīng)鎖相環(huán)設(shè)計

利用鎖相環(huán)進(jìn)行載波跟蹤是獲取本地載波的一種重要方法,針對鎖相環(huán)的噪聲性能和跟蹤速度不能同時達(dá)到最優(yōu)的限制,在鎖相環(huán)PLL中引入自適應(yīng)模塊,根據(jù)環(huán)路所處

2010-11-25 17:19:33 29

29

29

29pll鎖相環(huán)的作用 pll鎖相環(huán)的三種配置模式

pll鎖相環(huán)的作用 pll鎖相環(huán)的三種配置模式? PLL鎖相環(huán)是現(xiàn)代電子技術(shù)中廣泛應(yīng)用的一種電路,它的作用是將一個特定頻率的輸入信號轉(zhuǎn)換為固定頻率的輸出信號。PLL鎖相環(huán)的三種配置模式分別為

2023-10-13 17:39:48 167

167

167

167pll鎖相環(huán)倍頻的原理

pll鎖相環(huán)倍頻的原理? PLL鎖相環(huán)倍頻是一種重要的時鐘信號處理技術(shù),廣泛應(yīng)用于數(shù)字系統(tǒng)、通信系統(tǒng)、計算機(jī)等領(lǐng)域,具有高可靠性、高精度、快速跟蹤等優(yōu)點。PLL鎖相環(huán)倍頻的原理涉及到鎖相環(huán),倍頻器

2023-09-02 14:59:24 444

444

444

444鎖相環(huán)的研究和頻率合成

鎖相環(huán)的研究和頻率合成一、實驗?zāi)康模?. 振蕩器(VCO)的V—f 特性的研究2. 對稱波鎖相環(huán)基本特性的研究3. 利用鎖相環(huán)實現(xiàn)頻率合成二、鎖相環(huán)原理:

2009-03-06 20:02:52 1771

1771

1771

1771

鎖相環(huán)的構(gòu)成和工作原理講解

鎖相環(huán)電路,是調(diào)頻電路的重要組成之一,鎖相環(huán)電路的原理的認(rèn)識是DDS學(xué)習(xí)的一個重點之一。

2023-07-24 15:37:05 791

791

791

791

數(shù)字鎖相環(huán)基礎(chǔ)知識

鎖相環(huán)的鎖定是指鎖相環(huán)的輸出頻率等于輸入頻率,而輸出信號的相位跟隨輸入信號的變化而變化。

2023-01-31 16:31:12 1439

1439

1439

1439TI推出高性能寬頻帶RF鎖相環(huán)并集成了壓控振蕩器

德州儀器(TI)日推出了業(yè)內(nèi)具有集成壓控振蕩器(VCO)的最高性能鎖相環(huán)(PLLs)。

2020-05-28 10:21:14 664

664

664

664鎖相環(huán)的基本組成和工作原理

因鎖相環(huán)可以實現(xiàn)輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環(huán)通常用于閉環(huán)跟蹤電路。鎖相環(huán)在工作的過程中,當(dāng)輸出信號的頻率與輸入信號的頻率相等時,輸出電壓與輸入電壓保持固定的相位差值,即輸出電壓與輸入電壓的相位被鎖住,這就是鎖相環(huán)名稱的由來。

2022-05-10 14:25:19 6544

6544

6544

6544如何實現(xiàn)高性能的鎖相環(huán)(PLL)設(shè)計

鎖相環(huán)(PLL)是現(xiàn)代通信系統(tǒng)的基本構(gòu)建模塊,通常用在無線電接收機(jī)或發(fā)射機(jī)中,主要提供"本振"(LO)功能;也可用于時鐘信號分配和降噪,而且越來越多地用作高采樣速率模數(shù)或數(shù)模轉(zhuǎn)換的時鐘源。

2022-03-04 14:45:01 2941

2941

2941

2941

基于鎖相環(huán)的低頻函數(shù)發(fā)生器

介紹了鎖相環(huán)的原理以及Freescale公司的鎖相環(huán)頻率合成器件MC145151-2的主要特點,給出了MC145151-2和ICL8038低頻鎖相環(huán)函數(shù)發(fā)生器的工作原理、設(shè)計思想、電路結(jié)構(gòu)、模塊設(shè)計方法及其

2010-12-11 17:45:49 51

51

51

51軟件鎖相環(huán)在頻率突變時鎖不住 鎖相環(huán)無法鎖定怎么辦?

軟件鎖相環(huán)在頻率突變時鎖不住 鎖相環(huán)無法鎖定怎么辦?? 鎖相環(huán)(PLL)是一種用于在電路中生成穩(wěn)定頻率的技術(shù)。它是在1960年代開發(fā)的,并被廣泛應(yīng)用于通信、雷達(dá)、衛(wèi)星技術(shù)等領(lǐng)域中。鎖相環(huán)的主要作用

2023-10-13 17:39:58 97

97

97

97實驗 數(shù)字鎖相環(huán)與位同步

實驗五? 數(shù)字鎖相環(huán)與位同步

一、?實驗?zāi)康?

??? 1. 掌握數(shù)字鎖相環(huán)工作原理以及觸發(fā)式數(shù)字鎖

2009-04-01 09:27:45 4862

4862

4862

4862

模擬鎖相環(huán)與載波同步實驗

實驗 模擬鎖相環(huán)與載波同步

一、?實驗?zāi)康?

??? 1. 掌握模擬鎖相環(huán)的工作原理,以及環(huán)路的鎖定狀

2009-04-01 08:57:32 7733

7733

7733

7733

智能全數(shù)字鎖相環(huán)的設(shè)計

智能全數(shù)字鎖相環(huán)的設(shè)計:在FPGA片內(nèi)實現(xiàn)全數(shù)字鎖相環(huán)用途極廣。本文在集成數(shù)字鎖相環(huán)74297的基礎(chǔ)上進(jìn)行改進(jìn),設(shè)計了鎖相狀態(tài)檢測電路,配合CPU對環(huán)路濾波參數(shù)進(jìn)行動態(tài)智能配

2009-06-25 23:32:57 70

70

70

70鎖相環(huán)的性能,仿真和設(shè)計(第3版)

鎖相環(huán)的性能,仿真和設(shè)計(第3版):

PLL BASICS ......9CHAPTER 1 BASIC PLL OVERVIEW .....11CHAPTER 2 THE CHARGE PUMP

2009-07-25 16:56:22 340

340

340

340基于高壓VCO的高性能鎖相環(huán)設(shè)計

鎖相環(huán)(PLL) 是現(xiàn)代通信系統(tǒng)的基本構(gòu)建模塊。PLL 通 常用在無線電接收機(jī)或發(fā)射機(jī)中,主要提供本振(LO) 功 能;也可用于時鐘信號分配和降噪,而且越來越多地用作高采 樣速率模數(shù) (A

2011-03-30 16:01:16 49

49

49

49鎖相環(huán)的基本組成及工作原理

因鎖相環(huán)可以實現(xiàn)輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環(huán)通常用于閉環(huán)跟蹤電路。鎖相環(huán)在工作的過程中,當(dāng)輸出信號的頻率與輸入信號的頻率相等時,輸出電壓與輸入電壓保持固定的相位差值,即輸出電壓與輸入電壓的相位被鎖住,這就是鎖相環(huán)名稱的由來。

2020-11-03 14:55:49 14026

14026

14026

14026

基于數(shù)字鎖相環(huán)消除反饋滯后的方法

針對傳統(tǒng)數(shù)字鎖相環(huán)存在的反饋滯后造成系統(tǒng)動、靜態(tài)性能退化的問題,提出一種消除反饋滯后一拍的方法,以無反饋滯后理想數(shù)字鎖相環(huán)為參考模型,利用數(shù)字鎖相環(huán)當(dāng)前輸出與上一時刻輸出,計算得到與理想數(shù)字鎖相環(huán)

2018-01-02 10:30:41 9

9

9

9智能全數(shù)字鎖相環(huán)的設(shè)計

摘要: 在FPGA片內(nèi)實現(xiàn)全數(shù)字鎖相環(huán)用途極廣。本文在集成數(shù)字鎖相環(huán)74297的基礎(chǔ)上進(jìn)行改進(jìn),設(shè)計了鎖相狀態(tài)檢測電路,配合CPU對環(huán)路濾波參數(shù)進(jìn)行動態(tài)智

2009-06-20 12:39:32 1313

1313

1313

1313

集成鎖相環(huán)頻率合成器,什么是集成鎖相環(huán)頻率合成器

集成鎖相環(huán)頻率合成器,什么是集成鎖相環(huán)頻率合成器

頻率合成的歷史

頻率合成器被人們喻為眾多電子系統(tǒng)

2010-03-23 11:45:44 750

750

750

750鎖相環(huán)設(shè)計仿真與應(yīng)用

鎖相環(huán)設(shè)計仿真與應(yīng)用:PLL Performance, Simulation, and Design3rd EditionI would like to thank the following people for their as

2008-08-16 10:14:53 68

68

68

68鎖相環(huán)設(shè)計與仿真的基本知識

鎖相環(huán):在通信領(lǐng)域中,鎖相環(huán)是一種利用反饋控制原理實現(xiàn)的頻率及相位同步技術(shù),其作用是將電路輸出的時鐘與其外部的參考時鐘保持同步。

2023-06-30 15:53:39 1199

1199

1199

1199

關(guān)于鎖相環(huán)(PLL)的工作原理

鎖相環(huán)英文名稱PLL(Phase Locked Loop),中文名稱相位鎖栓回路,現(xiàn)在簡單介紹一下鎖相環(huán)的工作原理。

2023-04-28 09:57:31 3168

3168

3168

3168

一種基于FPGA實現(xiàn)的全數(shù)字鎖相環(huán)

鎖相環(huán)被廣泛應(yīng)用于電力系統(tǒng)的測量和控制中。介紹了一種新型的基于比例積分控制邏輯的全數(shù)字鎖相環(huán)。通過對其數(shù)學(xué)模型的分析,闡述了該鎖相環(huán)的各項性能指標(biāo)與設(shè)計參數(shù)的

2010-07-02 16:54:10 29

29

29

29鎖相環(huán)(PLL)基本原理 當(dāng)鎖相環(huán)無法鎖定時該怎么處理的呢?

鎖相環(huán)(PLL)基本原理 當(dāng)鎖相環(huán)無法鎖定時該怎么處理的呢? 鎖相環(huán)(Phase Locked Loop, PLL)是一種電路系統(tǒng),它可以將輸入信號的相位鎖定到參考信號的相位。在鎖相環(huán)中,反饋回路

2023-10-23 10:10:15 47

47

47

47鎖相環(huán)的原理及應(yīng)用詳細(xì)資料說明

鎖相環(huán)(PLL)電路存在于各種高頻應(yīng)用中,從簡單的時鐘凈化電路到用于高性能無線電通信鏈路的本振(LO),以及矢量網(wǎng)絡(luò)分析儀(VNA)中的超快開關(guān)頻率合成器。鎖相環(huán)是一種反饋系統(tǒng),其中電壓控制振蕩器

2020-12-16 13:57:00 24

24

24

24鎖相環(huán)技術(shù)及CD4046的結(jié)構(gòu)和應(yīng)用

敘述了鎖相環(huán)的應(yīng)用及其結(jié)構(gòu)特點, 較詳細(xì)地介紹了鎖相集成電路CD4046的結(jié)構(gòu)特點和應(yīng)用。

2012-04-17 15:04:03 556

556

556

556使用MAX9382的鎖相環(huán)應(yīng)用

本應(yīng)用筆記討論了影響鎖相環(huán)(PLL)死區(qū)和抖動性能的鑒頻鑒相器特性。在采用電荷泵環(huán)路濾波器設(shè)計的PLL中,提供最短持續(xù)時間的鑒相器輸出脈沖幾乎消除了PLL死區(qū)行為和相關(guān)鎖相環(huán)抖動。

2023-02-23 17:52:07 368

368

368

368

使用MC145170鎖相環(huán)實現(xiàn)調(diào)頻鎖相環(huán)收音機(jī)的PCB原理圖免費下載

本文檔的主要內(nèi)容詳細(xì)介紹的是使用MC145170鎖相環(huán)實現(xiàn)調(diào)頻鎖相環(huán)收音機(jī)的PCB原理圖免費下載。

2020-11-02 17:15:00 72

72

72

72使用FPGA實現(xiàn)數(shù)字鎖相環(huán)的設(shè)計資料說明

鎖相環(huán)路是一種反饋控制電路,簡稱鎖相環(huán)( PLL)。鎖相環(huán)的特點是:利用外部輸入的參考信號控制環(huán)路內(nèi)部振蕩信號的頻率和相位。因鎖相環(huán)可以實現(xiàn)輸出信號頻率對輸入信號頻率的自動跟蹤, 所以鎖相環(huán)通常

2020-08-06 17:58:25 24

24

24

24全數(shù)字鎖相環(huán)的設(shè)計

智能全數(shù)字鎖相環(huán)的設(shè)計

摘要: 在FPGA片內(nèi)實現(xiàn)全數(shù)字

2008-08-14 22:12:51 52

52

52

52小數(shù)分頻鎖相環(huán)的工作原理

議程PLL介紹及小數(shù)分頻鎖相環(huán)的優(yōu)點小數(shù)分頻鎖相環(huán)的錯誤使用小數(shù)分頻鎖相環(huán)詳解參考雜散及如何減少雜散總結(jié)

2010-05-28 14:58:36 168

168

168

168使用PLD內(nèi)部鎖相環(huán)解決系統(tǒng)設(shè)計難題

摘要: 從整個應(yīng)用系統(tǒng)的角度,理解和分析PLD內(nèi)部鎖相環(huán);在此基礎(chǔ)上,深入剖析鎖相環(huán)的相移結(jié)構(gòu),同時用這個技術(shù)解決系統(tǒng)設(shè)計難題。

關(guān)鍵

2009-06-20 12:40:02 651

651

651

651

什么是鎖相環(huán)?PLL和DLL都是鎖相環(huán)區(qū)別在哪里?

什么是鎖相環(huán)?PLL和DLL都是鎖相環(huán)區(qū)別在哪里? 鎖相環(huán)(Phase Locked Loop,PLL)是一種基于反饋的控制系統(tǒng),用于提供穩(wěn)定的時鐘信號。它可以將參考信號的相位與輸出信號的相位進(jìn)行

2023-10-13 17:39:53 106

106

106

106基于TRAC器件的鎖相環(huán)設(shè)計研究

以TRAC020LH 完全可重配置模擬器件和TRAC 開發(fā)軟件為基礎(chǔ),設(shè)計模擬鎖相環(huán);給出仿真結(jié)果和利用PIC 單片機(jī)對器件進(jìn)行配置的應(yīng)用電路。該鎖相環(huán)成功應(yīng)用于逆變器的頻率跟蹤,性能

2009-04-15 11:42:39 11

11

11

11快速了解Pasternack推出的高性能USB控制鎖相環(huán)頻率合成器

穩(wěn)定性、高精度以及優(yōu)異的相位噪聲特性,從而可使信號鏈中的器件以最佳性能工作。這些新式鎖相環(huán)頻率合成器的用途包括信號發(fā)生器、臺式測試和測量、電子戰(zhàn)及微波無線電。

2018-04-26 11:16:00 601

601

601

601 電子發(fā)燒友App

電子發(fā)燒友App

評論