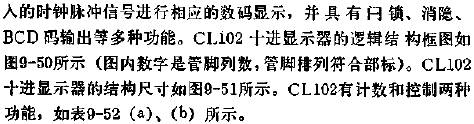

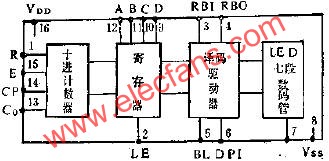

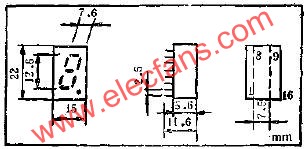

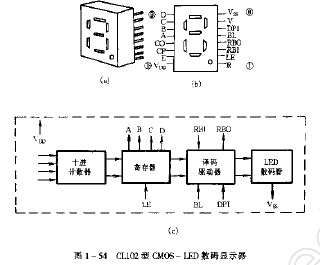

CL102十進(jìn)制計(jì)數(shù)顯示器的應(yīng)用電路圖

- 顯示器(136592)

- 計(jì)數(shù)(19913)

相關(guān)推薦

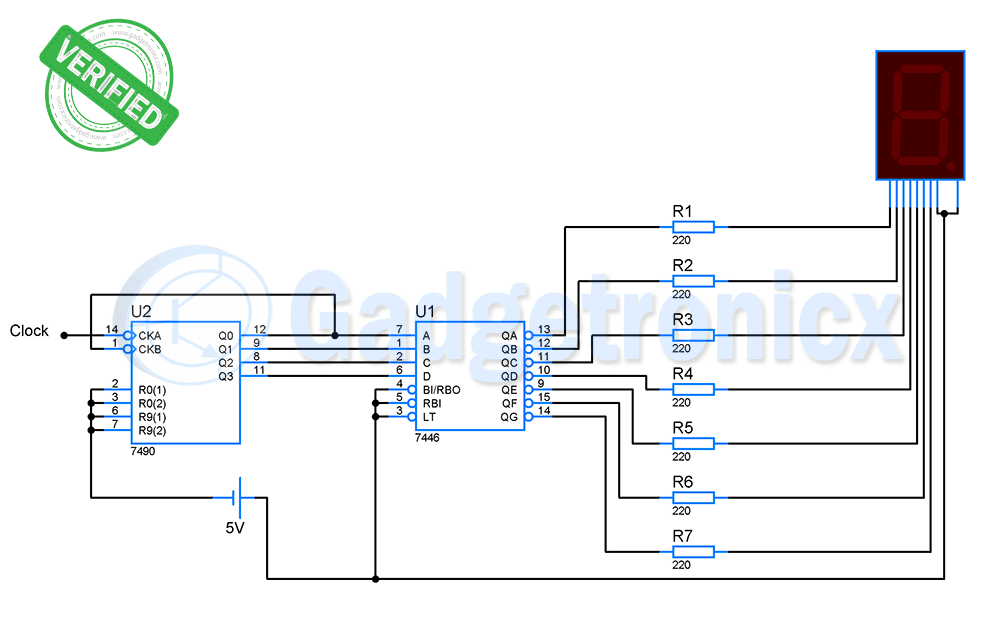

基于異步十進(jìn)制計(jì)數(shù)器IC7490的電路

圖所示電路是靜態(tài)的0到9顯示,使用能夠顯示7到0數(shù)字的9段。它在日常生活中有很多應(yīng)用,并使用兩個簡單的IC的7490和7446實(shí)現(xiàn)。該電路基于異步十進(jìn)制計(jì)數(shù)器7490(IC2)、7段顯示器(D1

2023-07-05 15:51:15 435

435

435

435

可預(yù)置同步BCD十進(jìn)制計(jì)數(shù)器;異步復(fù)位-74HC160

可預(yù)置同步BCD十進(jìn)制計(jì)數(shù)器;異步復(fù)位-74HC160

2023-02-20 20:05:50 4

4

4

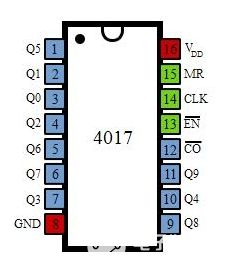

4帶 10 個解碼輸出的 Johnson 十進(jìn)制計(jì)數(shù)器-74HC_HCT4017_Q100

帶 10 個解碼輸出的 Johnson 十進(jìn)制計(jì)數(shù)器-74HC_HCT4017_Q100

2023-02-17 19:59:07 0

0

0

0帶 10 個解碼輸出的 Johnson 十進(jìn)制計(jì)數(shù)器-74HC_HCT4017

帶 10 個解碼輸出的 Johnson 十進(jìn)制計(jì)數(shù)器-74HC_HCT4017

2023-02-16 20:29:32 0

0

0

0基于FPGA的十進(jìn)制計(jì)數(shù)器

本方案是一個基于 FPGA ?的十進(jìn)制計(jì)數(shù)器。共陽極 7 段顯示器上的 0 到 9 十進(jìn)制計(jì)數(shù)器,硬件在 Xilinx Spartan 6 FPGA 板上實(shí)現(xiàn)。

2022-12-20 14:52:25 2

2

2

2十進(jìn)制計(jì)數(shù)器的工作原理

二進(jìn)制編碼的十進(jìn)制是一個串行數(shù)字計(jì)數(shù)器,可計(jì)數(shù)十位數(shù)字,它會為每個新的時鐘輸入重置。由于它可以通過10種獨(dú)特的輸出組合,因此也被稱為“十進(jìn)制(BCD)計(jì)數(shù)器”。十進(jìn)制計(jì)數(shù)器可以計(jì)數(shù)0000、0001、0010、1000、1001、1010、1011、1110、1111、0000和0001等。

2022-10-31 16:25:37 11019

11019

11019

11019

CD4017十進(jìn)制計(jì)數(shù)器的基本概念及應(yīng)用電路

通常,我們更喜歡說1、2、3、4……而不是001、010、011、100。也就是說,在許多情況下,我們需要十進(jìn)制編碼輸出,而不是原始二進(jìn)制輸出。

2022-10-31 15:46:35 19282

19282

19282

19282

使用Arduino和OLED顯示器的二進(jìn)制到十進(jìn)制轉(zhuǎn)換器

電子發(fā)燒友網(wǎng)站提供《使用Arduino和OLED顯示器的二進(jìn)制到十進(jìn)制轉(zhuǎn)換器.zip》資料免費(fèi)下載

2022-10-31 14:30:12 6

6

6

6關(guān)于數(shù)字邏輯電路計(jì)數(shù)器的實(shí)驗(yàn)

一、實(shí)驗(yàn)?zāi)康?

1、熟悉計(jì)數(shù)器、譯碼器和顯示器的使用方法。

2、提高綜合實(shí)踐的技能。

3、設(shè)計(jì)十進(jìn)制,并用譯碼器和顯示器,顯示計(jì)數(shù)結(jié)果。

2022-10-21 16:48:49 0

0

0

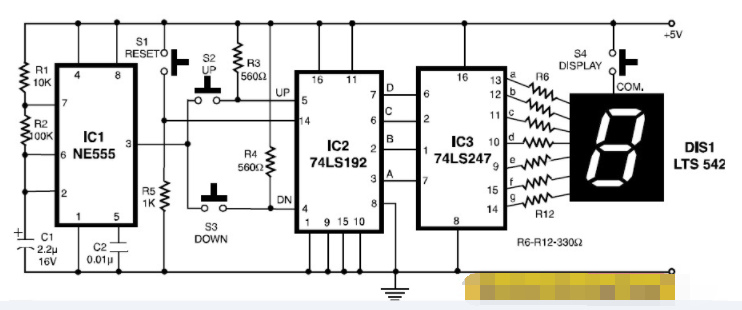

0使用7段LED的比賽計(jì)分顯示電路圖介紹

這是使用7段LED的比賽計(jì)分顯示電路圖。該電路由一個定時器IC、兩個十進(jìn)制計(jì)數(shù)器和一個顯示驅(qū)動器以及一個用于顯示分?jǐn)?shù)的7段LED顯示屏組成。

2022-05-30 17:20:44 2671

2671

2671

2671

CD4017十進(jìn)制計(jì)數(shù)器的應(yīng)用實(shí)驗(yàn)

CD4017 十進(jìn)制計(jì)數(shù)器的應(yīng)用實(shí)驗(yàn)

2022-05-11 16:58:25 47

47

47

47十進(jìn)制數(shù)的位權(quán)圖

十進(jìn)制 好,那就讓我們來看看十進(jìn)制 所謂十進(jìn)制就是以10為基數(shù)的計(jì)數(shù)體制,其計(jì)數(shù)規(guī)律是逢十進(jìn)一。 圖1.3.1展示了十進(jìn)制的位號和位權(quán)之間關(guān)系的圖解。位號3210-1-2-3十進(jìn)制數(shù)

2009-04-06 23:47:02

74ls161十進(jìn)制計(jì)數(shù)器電路圖

)。 ? ? ? ? 74LS161電路圖: ?(a)用前十個有效狀態(tài)? ?(b)用后十個有效狀態(tài) ? ? 文章綜合來源:eeworld 編輯:ymf

2021-07-09 16:12:21 73502

73502

73502

73502

74ls160價格 74ls160十進(jìn)制計(jì)數(shù)器簡介

芯片74ls160是十進(jìn)制計(jì)數(shù)器,這種同步可預(yù)置十進(jìn)計(jì)數(shù)器是由四個D型觸發(fā)器和若干個門電路構(gòu)成。

2021-06-05 14:35:38 12686

12686

12686

12686十進(jìn)制計(jì)數(shù)器的Multisim仿真實(shí)例電路圖免費(fèi)下載

本文檔的主要內(nèi)容詳細(xì)介紹的是十進(jìn)制計(jì)數(shù)器的Multisim仿真實(shí)例電路圖免費(fèi)下載。

2020-09-04 16:55:00 81

81

81

81二進(jìn)制編碼的十進(jìn)制表示轉(zhuǎn)換解碼器

二進(jìn)制編碼小數(shù)的主要優(yōu)點(diǎn)是它允許在decimal(base-10)和binary(base-2)表單之間輕松轉(zhuǎn)換。但是,缺點(diǎn)是BCD代碼是浪費(fèi)的,因?yàn)椴皇褂?1010 (十進(jìn)制10)和 1111 (十進(jìn)制15)之間的狀態(tài)。然而,二進(jìn)制編碼的十進(jìn)制有許多重要的應(yīng)用,特別是使用數(shù)字顯示。

2019-06-24 09:31:19 12524

12524

12524

12524

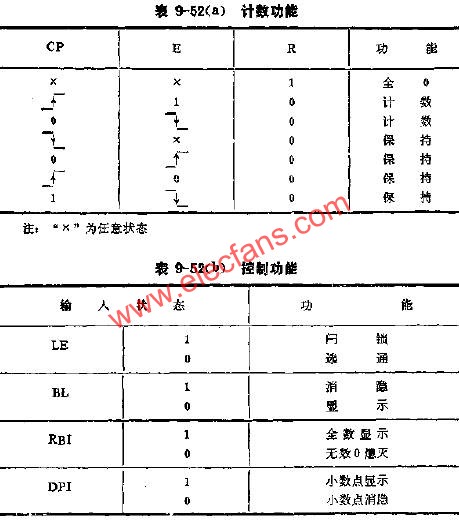

CD40110十進(jìn)制加減計(jì)數(shù)器鎖存器譯碼器驅(qū)動器的數(shù)據(jù)手冊免費(fèi)下載

40110 為十進(jìn)制可逆計(jì)數(shù)器/鎖存器/譯碼器/驅(qū)動器,具有加減計(jì)數(shù),計(jì)數(shù)器狀態(tài)鎖存,七段顯示譯碼輸出等功能。

2019-04-30 08:00:00 6

6

6

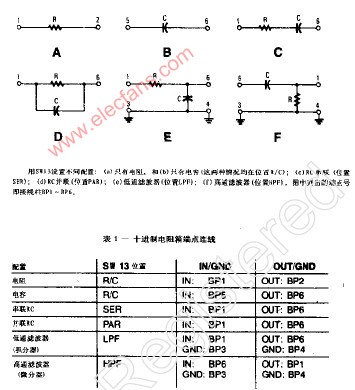

6由TTL十進(jìn)制計(jì)數(shù)器構(gòu)成的分頻器

關(guān)鍵詞:TTL , 分頻器 , 計(jì)數(shù)器 , 十進(jìn)制 如圖所示為由TTL十進(jìn)制計(jì)數(shù)器構(gòu)成的分頻電路。在許多情況下。需要對脈沖序列進(jìn)行N(N為整數(shù))分頻。例如,數(shù)字鐘需要進(jìn)行60分頻,得到重復(fù)頻率為

2018-10-03 18:46:02 2650

2650

2650

2650二進(jìn)制與十進(jìn)制數(shù)對照顯示實(shí)驗(yàn),十進(jìn)制,二進(jìn)制對照

原理 電路圖如下圖所示。

這是一個可以對照顯示0~9這10個數(shù)字的二進(jìn)制和十進(jìn)制的電路。二進(jìn)制數(shù)字用4個發(fā)光二極管顯示;它們排成一行,亮表示1,滅表示0。十進(jìn)制數(shù)字用一個數(shù)碼管表示。數(shù)字的變化采用

2018-09-20 18:26:41 2050

2050

2050

205074ls190應(yīng)用電路圖大全(五款74ls190不同進(jìn)制計(jì)數(shù)器電路)

本文主要介紹了五款74ls190應(yīng)用電路圖。包括了60和100進(jìn)制計(jì)數(shù)器(遞增)電路,56進(jìn)制遞減計(jì)數(shù)器與100進(jìn)制遞減計(jì)數(shù)器電路和2位十進(jìn)制可加減計(jì)數(shù)器電路。

2018-05-28 16:18:11 54071

54071

54071

54071

74ls192計(jì)數(shù)器應(yīng)用電路圖大全(五款電子骰子/計(jì)時/定時電路)

本文主要介紹了五款74ls192計(jì)數(shù)器應(yīng)用電路圖。其中包括了74ls192電子骰子電路、74ls192計(jì)時電路、74ls192定時電路、74ls19230進(jìn)制計(jì)數(shù)器電路及兩位十進(jìn)制計(jì)數(shù)器。

2018-05-28 10:20:01 116393

116393

116393

116393

cd4026應(yīng)用電路圖大全(555時基電路/按鍵計(jì)數(shù)器/脈沖計(jì)數(shù)器)

本文主要介紹了cd4026應(yīng)用電路圖大全(555時基電路/按鍵計(jì)數(shù)器/脈沖計(jì)數(shù)器)。由CD4026、555時基電路等組成的數(shù)字顯示門鈴電路,是由十進(jìn)制計(jì)數(shù)/7段譯碼器CD4026、555時基電路等

2018-05-10 16:44:50 11589

11589

11589

11589

74ls163應(yīng)用電路圖大全(N進(jìn)制計(jì)數(shù)器\分頻電路\時鐘脈沖)

本文主要介紹了74ls163應(yīng)用電路圖大全(N進(jìn)制計(jì)數(shù)器\分頻電路\時鐘脈沖)。74LS163是(模16)四位二進(jìn)制同步計(jì)數(shù)器。該計(jì)數(shù)器能同步并行預(yù)置數(shù)據(jù),同步清零,具有清零、置數(shù)、計(jì)數(shù)和保持四種

2018-05-08 14:27:23 51924

51924

51924

51924

74ls163實(shí)現(xiàn)十進(jìn)制計(jì)數(shù)器電路

本文主要介紹了74ls163實(shí)現(xiàn)十進(jìn)制計(jì)數(shù)器電路。改變74LS163二進(jìn)制計(jì)數(shù)器為十進(jìn)制計(jì)數(shù)器,即用一FDS4435BZ個與非門,其兩個輸人取自QA和QD,輸出接清零端α‘R。當(dāng)?shù)?個脈沖結(jié)束時,鈑

2018-05-08 11:31:20 44957

44957

44957

44957

74ls290計(jì)數(shù)器電路大全(六種進(jìn)制計(jì)數(shù)器電路)

74ls290是一個二,五,十進(jìn)制計(jì)數(shù)器,本文為大家介紹由74ls290構(gòu)成的各種進(jìn)制計(jì)數(shù)器的電路。

2018-01-26 09:26:11 106188

106188

106188

106188

74LS290組成的十進(jìn)制計(jì)數(shù)器電路圖分享

計(jì)數(shù)器在數(shù)字系統(tǒng)中應(yīng)用廣泛,如在電子計(jì)算機(jī)的控制器中對指令地址進(jìn)行計(jì)數(shù),以便順序取出下一條指令,在運(yùn)算器中作乘法、除法運(yùn)算時記下加法、減法次數(shù),又如在數(shù)字儀器中對脈沖的計(jì)數(shù)等等。本文為大家介紹74LS290組成的十進(jìn)制計(jì)數(shù)器。

2018-01-25 14:52:47 25181

25181

25181

25181

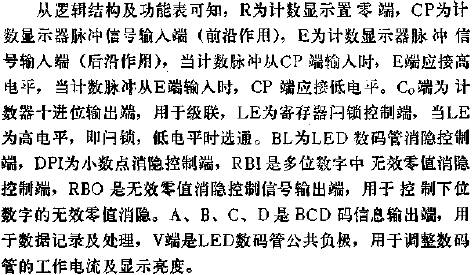

74ls290構(gòu)成31進(jìn)制計(jì)數(shù)器電路圖文詳解

74LS290為異步二-五-十進(jìn)制加法計(jì)數(shù)器。本文為大家介紹74ls290構(gòu)成31進(jìn)制計(jì)數(shù)器電路。

2018-01-25 14:36:39 16924

16924

16924

16924

74ls160構(gòu)成24進(jìn)制計(jì)數(shù)器

的CLK端,電路在計(jì)數(shù)脈沖的作用下按二進(jìn)制自然序依次遞增1,當(dāng)個位計(jì)數(shù)到9時,輸出進(jìn)位信號給十位充當(dāng)使能信號進(jìn)位。當(dāng)計(jì)數(shù)到24,這顯示器個位輸出0010(也就是4),顯示器十位輸出0010也就是2),將十位的QC、個位的QB端接一個二輸入與非門,與非門輸出一路送入十位計(jì)數(shù)器的清零端。

2018-01-18 15:43:05 145644

145644

145644

145644

74ls160十進(jìn)制計(jì)數(shù)器

本文主要介紹了74ls160十進(jìn)制計(jì)數(shù)器電路的設(shè)計(jì)與實(shí)現(xiàn)。74LS160是二~十進(jìn)制同步可預(yù)置計(jì)數(shù)器,1腳Cr為清零端,低電平有效.2腳CP為時鐘脈沖輸人端,上升沿觸發(fā).3~6V腳D1一D4為數(shù)據(jù)

2018-01-18 15:14:45 182091

182091

182091

182091

74ls90設(shè)計(jì)60進(jìn)制計(jì)數(shù)器

60進(jìn)制計(jì)數(shù)器,由于24進(jìn)制、60進(jìn)制計(jì)數(shù)器均由集成計(jì)數(shù)器級聯(lián)構(gòu)成,且都包含有基本的十進(jìn)制計(jì)數(shù)器,從設(shè)計(jì)簡便考慮,芯片選擇同步十進(jìn)制計(jì)數(shù)器

2017-12-22 13:55:48 148134

148134

148134

148134

十進(jìn)制計(jì)數(shù)器/分頻器

約翰遜MC14017B是五級十進(jìn)制計(jì)數(shù)器內(nèi)置代碼轉(zhuǎn)換器。 高速運(yùn)行和約翰遜spike-free輸出是通過使用十進(jìn)制計(jì)數(shù)器的設(shè)計(jì)。 十個解碼輸出通常是低,只在適當(dāng)?shù)?b style="color: red">十進(jìn)制時間走高。 輸出的正向變化的時鐘脈沖。 這部分可用于分頻應(yīng)用程序以及十進(jìn)制計(jì)數(shù)器或十進(jìn)制譯碼顯示應(yīng)用程序。

2017-04-06 09:03:48 28

28

28

28數(shù)字邏輯電路計(jì)數(shù)器_實(shí)驗(yàn)六

實(shí)驗(yàn)?zāi)康模?

1、熟悉計(jì)數(shù)器、譯碼器和顯示器的使用方法。

2、提高綜合實(shí)踐的技能。

3.設(shè)計(jì)十進(jìn)制,并用譯碼器和顯示器,顯示計(jì)數(shù)結(jié)果。

2016-10-11 17:41:59 37

37

37

37二五十進(jìn)制計(jì)數(shù)器

數(shù)字電子技術(shù)--中規(guī)模集成計(jì)數(shù)器及其應(yīng)用--同步、異步二五十進(jìn)制計(jì)數(shù)器-PPT

2016-03-22 14:33:06 1

1

1

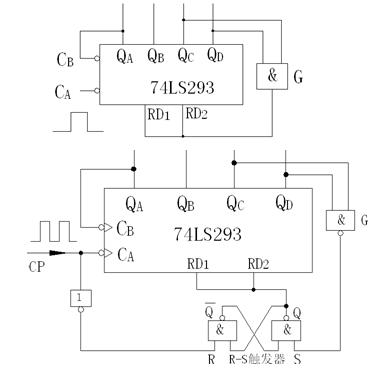

1十進(jìn)制可逆計(jì)數(shù)器74LS192引腳圖管腳及功能表

十進(jìn)制可逆計(jì)數(shù)器74LS192引腳圖管腳及功能表

2011-05-19 11:22:27 118057

118057

118057

1180574位十進(jìn)制可逆計(jì)數(shù)器電路

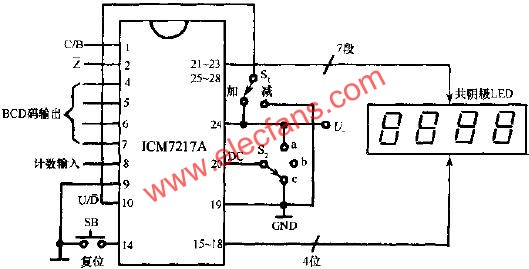

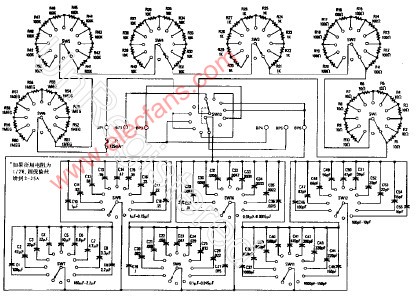

使用一片ICM7217A配4只共陰極LED數(shù)碼管,可構(gòu)成4位十進(jìn)制可逆計(jì)數(shù)器,其

2010-12-10 13:55:24 6871

6871

6871

6871

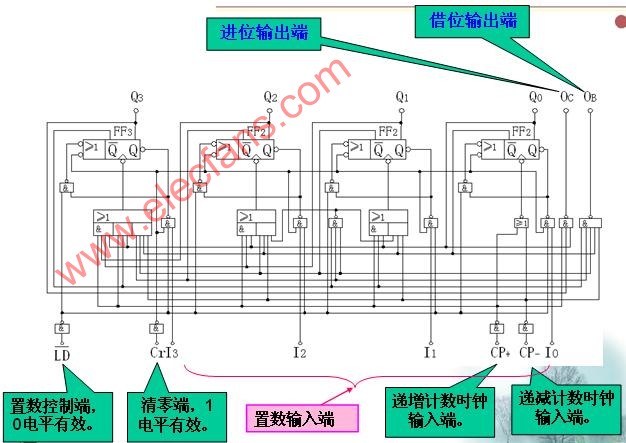

CL102組成五位數(shù)碼顯示器線路圖

圖中所示是用CL102進(jìn)制計(jì)數(shù)顯示器組成的五位數(shù)碼顯示器線路.單塊CL102十進(jìn)計(jì)數(shù)顯示器對輸入時鐘脈沖就能直接進(jìn)行數(shù)碼顯示,不須外接其它元件.將多塊CL102十進(jìn)計(jì)數(shù)

2010-10-20 15:30:51 2315

2315

2315

2315

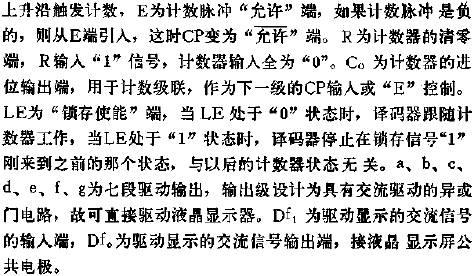

ZC256十進(jìn)計(jì)數(shù)、鎖存、譯碼、顯示驅(qū)動器(驅(qū)動液晶顯示器)

CMOS ZC256電路是具有十進(jìn)制計(jì)數(shù)功能、輸出鎖存功能、BCD到七段的譯碼功能和顯示驅(qū)動功能的"四合一"電

2010-10-20 14:15:30 1681

1681

1681

1681

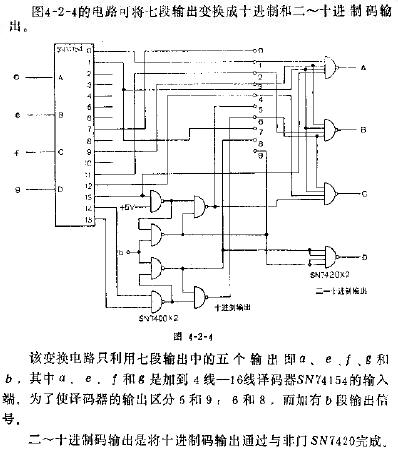

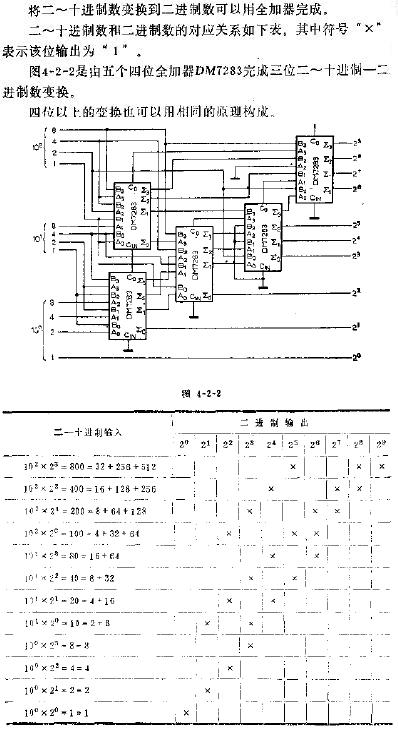

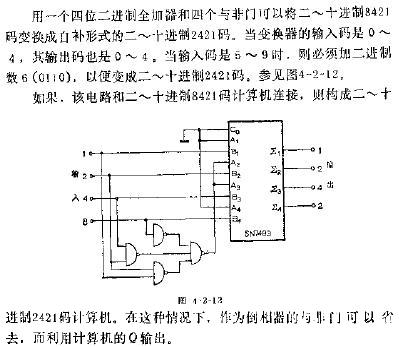

十進(jìn)制加法器,十進(jìn)制加法器工作原理是什么?

十進(jìn)制加法器,十進(jìn)制加法器工作原理是什么?

十進(jìn)制加法器可由BCD碼(二-十進(jìn)制碼)來設(shè)計(jì),它可以在二進(jìn)制加法器的基礎(chǔ)上加上適當(dāng)?shù)摹靶U边壿媮韺?shí)現(xiàn),該校正邏

2010-04-13 10:58:41 12142

12142

12142

12142十進(jìn)制計(jì)數(shù)器,十進(jìn)制計(jì)數(shù)器原理是什么?

十進(jìn)制計(jì)數(shù)器,十進(jìn)制計(jì)數(shù)器原理是什么?

二進(jìn)制計(jì)數(shù)器具有電路結(jié)構(gòu)簡單、運(yùn)算方便等特點(diǎn),但是日常生活中我們所接觸的大部分都是十進(jìn)制數(shù),特

2010-03-08 13:19:54 23684

23684

23684

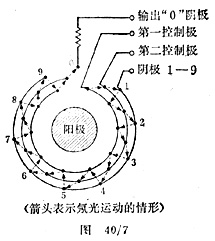

23684十進(jìn)制計(jì)數(shù)管

十進(jìn)制計(jì)數(shù)管 十進(jìn)制計(jì)數(shù)管是由中央的圓板狀陽極和圍繞著它放置的三十根線狀的電極組成。這些線狀電極三根一組,共十組,每

2009-10-13 15:05:12 1357

1357

1357

1357

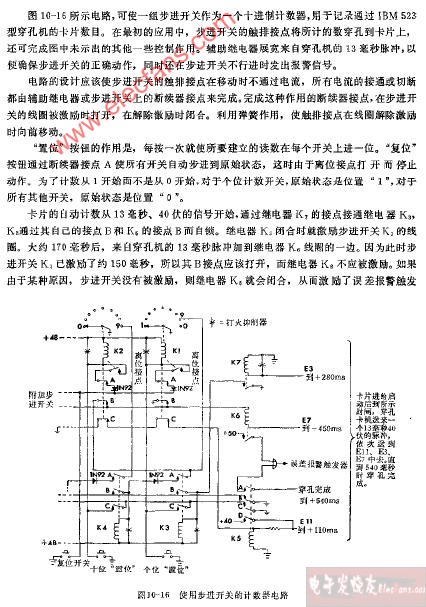

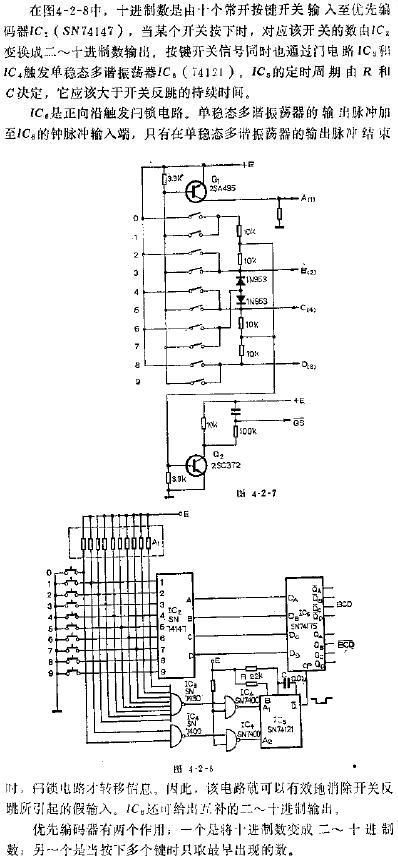

步進(jìn)開關(guān)作為十進(jìn)制計(jì)數(shù)器電路圖

步進(jìn)開關(guān)作為十進(jìn)制計(jì)數(shù)器電路圖

2009-06-30 13:08:13 867

867

867

867

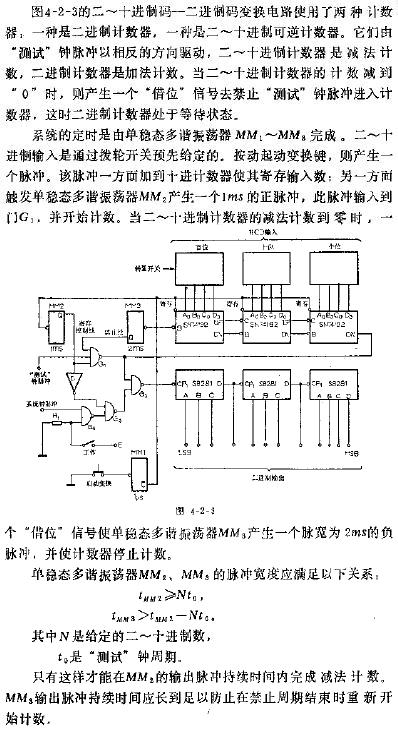

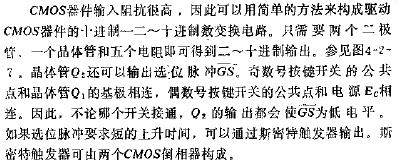

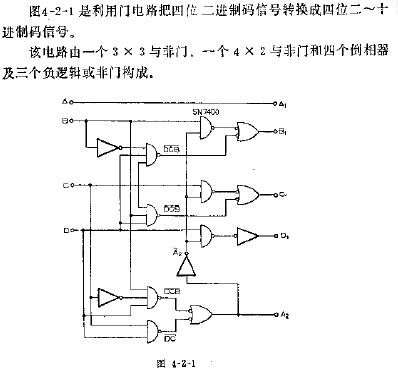

采用減法計(jì)數(shù)簡化二~十進(jìn)制一二進(jìn)制碼變換

采用減法計(jì)數(shù)簡化二~十進(jìn)制一二進(jìn)制碼變換

2009-04-10 10:06:11 562

562

562

562

十進(jìn)制和二進(jìn)制之間的轉(zhuǎn)換

十進(jìn)制和二進(jìn)制之間的轉(zhuǎn)換

既然一個數(shù)可以用二進(jìn)制和十進(jìn)制兩種不同形式來表示,那么兩著之間就必然有一定的轉(zhuǎn)換關(guān)系。 由十進(jìn)制數(shù)的一

2009-04-06 23:53:36 6970

6970

6970

6970

十進(jìn)制

十進(jìn)制

好,那就讓我們來看看十進(jìn)制 所謂十進(jìn)制就是以10為基數(shù)的計(jì)數(shù)體制,其計(jì)數(shù)規(guī)律是逢十進(jìn)一。 圖1.3.1展示了十進(jìn)制的位號和位權(quán)之間關(guān)系的圖解

2009-04-06 23:46:24 1940

1940

1940

1940

74LS161構(gòu)成的五十(50)進(jìn)制計(jì)數(shù)器電路圖-原理圖

兩片4位二進(jìn)制數(shù)加法計(jì)數(shù)器74LS161級聯(lián)成五十進(jìn)制計(jì)數(shù)器。

2009-03-28 10:10:23 33045

33045

33045

33045

十進(jìn)制計(jì)數(shù)器工作原理

十進(jìn)制計(jì)數(shù)器工作原理

同二進(jìn)制計(jì)數(shù)器相比,十進(jìn)制計(jì)數(shù)器較為復(fù)雜。分析步驟一般是:

2008-01-21 13:15:22 27668

27668

27668

27668

2位十進(jìn)制可加減計(jì)數(shù)器電路-74LS190應(yīng)用電路

2位十進(jìn)制可加減計(jì)數(shù)器電路-74LS190應(yīng)用電路

2007-12-07 00:12:12 9254

9254

9254

9254

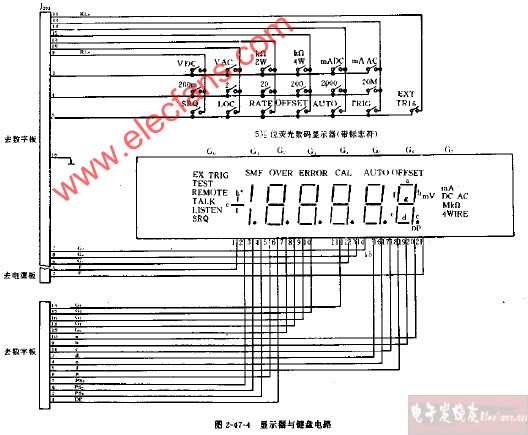

74LS161計(jì)數(shù)器及顯示應(yīng)用電路圖

74LS161計(jì)數(shù)器及顯示應(yīng)用電路圖

電路中由兩個與非門構(gòu)成單脈沖發(fā)生器,計(jì)數(shù)器74LS161對其

2007-12-02 22:25:26 10890

10890

10890

10890

計(jì)數(shù)器的級連使用

計(jì)數(shù)器的級連使用

一個十進(jìn)制計(jì)數(shù)器只能顯示0~9十個數(shù),為了擴(kuò)大計(jì)數(shù)器范圍,常用多個十進(jìn)制計(jì)數(shù)器級連使用。

2007-11-22 12:53:25 3143

3143

3143

3143

十進(jìn)制計(jì)數(shù)器

十進(jìn)制計(jì)數(shù)器

二進(jìn)制計(jì)數(shù)器具有電路結(jié)構(gòu)簡單、運(yùn)算方便等特點(diǎn),但是日常生活中我們所接觸的大部分都是十進(jìn)制數(shù),特別是當(dāng)二進(jìn)制數(shù)的位數(shù)較多時,閱讀非常困難,還

2007-06-20 13:46:05 3559

3559

3559

3559 電子發(fā)燒友App

電子發(fā)燒友App

評論