易靈思RAM在使用時可以會遇到一些問題,這里把常用的問題總結下。

除通過外部多功能IO來選擇之外,易靈思通過內部重配置實現遠程更新操作也非常簡單。

MIPI Dsi的使用相比于CSI多了一些寄存器控制,生成的example直接仿真是可以的,但是修改....

MIPI Dsi的使用相比于CSI多了一些寄存器控制,生成的example直接仿真是可以的,但是修改....

MIPI Dsi的使用相比于CSI多了一些寄存器控制,生成的example直接仿真是可以的,但是修改....

說明:該下載器把SPI與JTAG管腳進行了分開處理。 鑒于JTAG使用較多,SPI使用較少,所以把J....

關于clkout4的說明其實不多,在PLL的說明中提到CLKOUT4只用于top和bottom的區域....

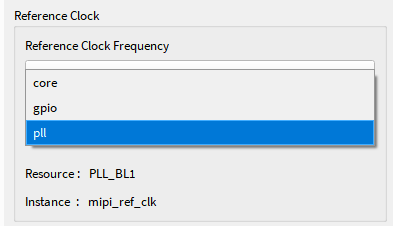

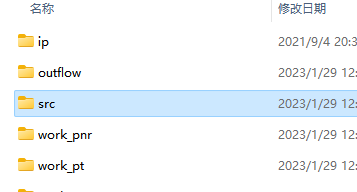

最近陸續有客戶在評估易靈思的Ti180。Ti180的MIPI 2.5G是硬核。今天做一個簡單的移植來....

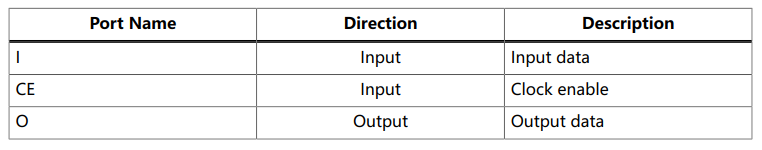

如果普通的GPIO怎么走全局時鐘網絡,其實很簡單,打開原主文檔,找到EFX_GBUFCE,該部分提供....

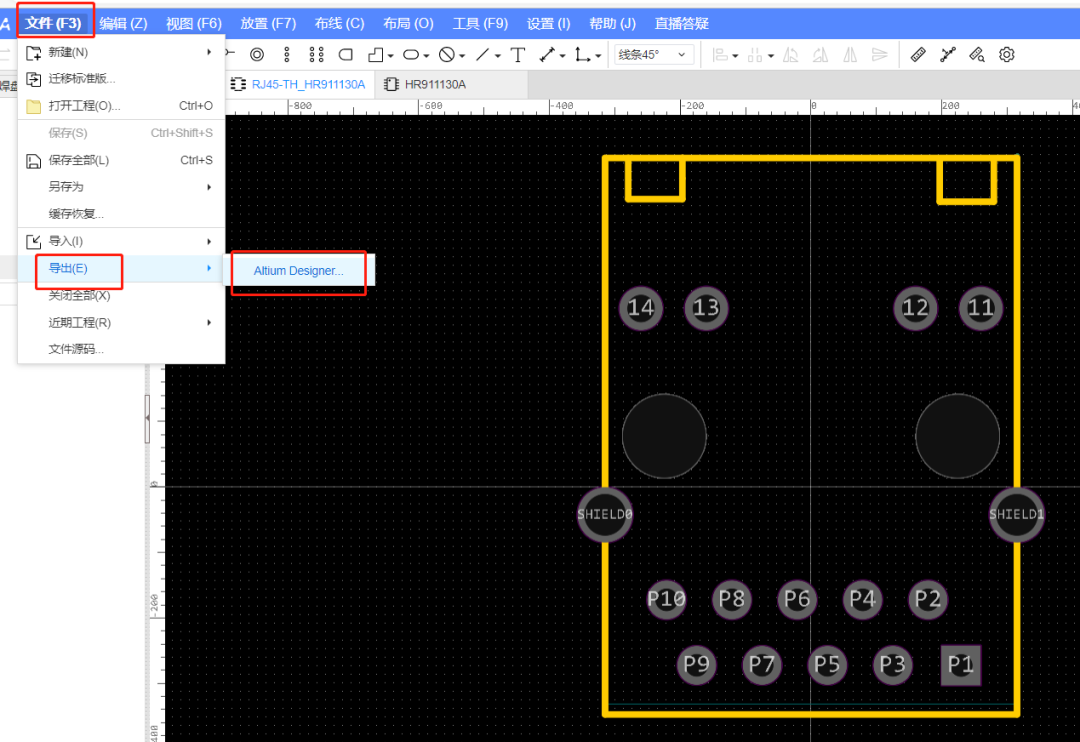

怎樣把立創的PCB轉成allegro的

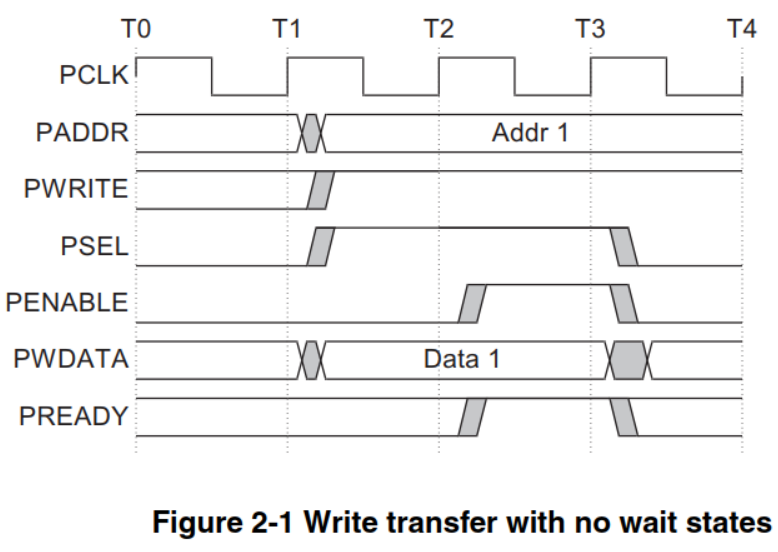

APB3是一個低功耗低成本接口。所有信號在時鐘上升沿傳輸,每次傳輸需要兩個時鐘周期。

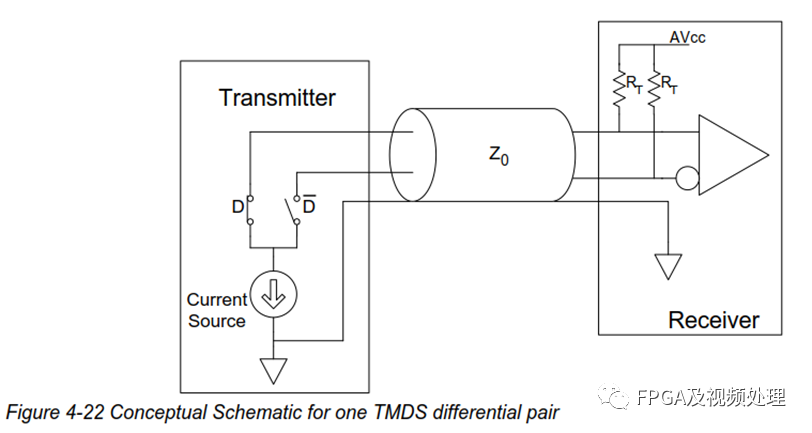

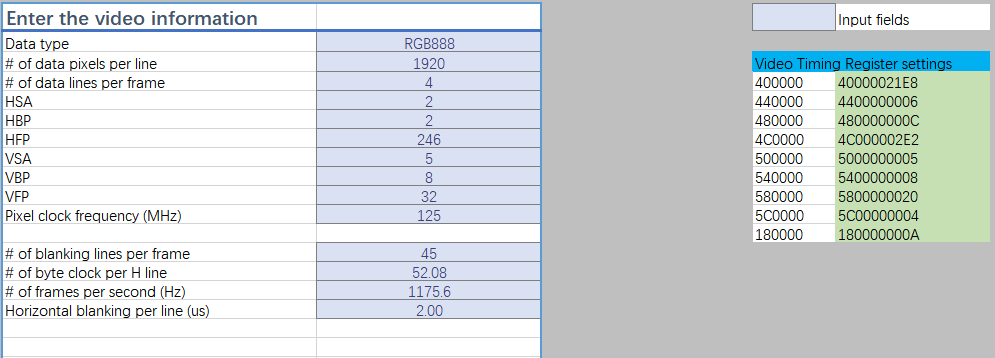

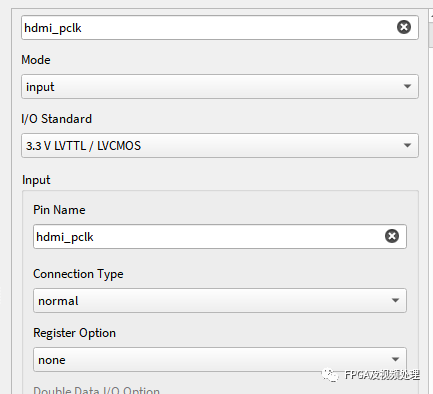

xilinx和altera都有通過IO驅動HDMI的方案,支持的分辨率各有不同,這跟不同系列的FPG....

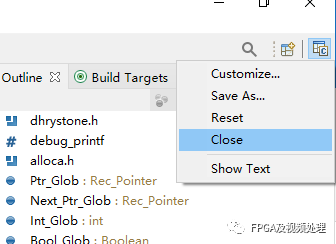

如果工程直接復制另一個工程,路徑一定要修改,建議重新eclipse工程。

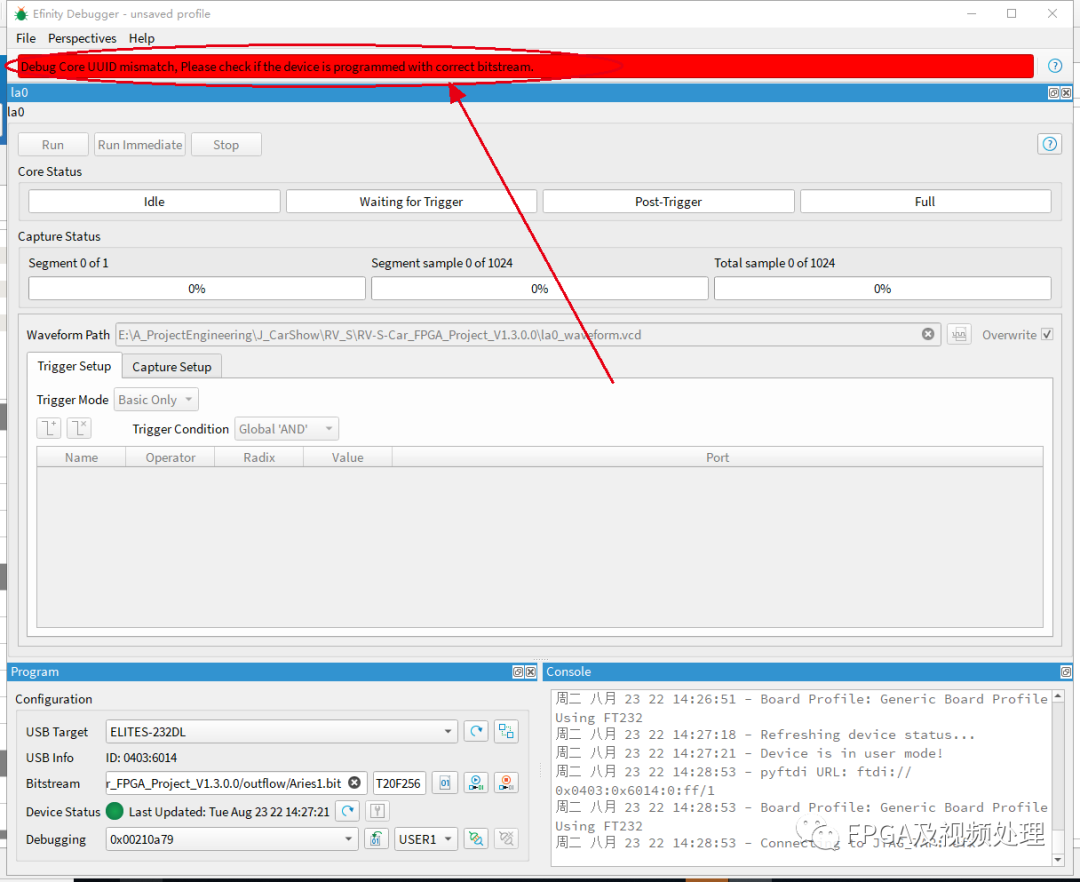

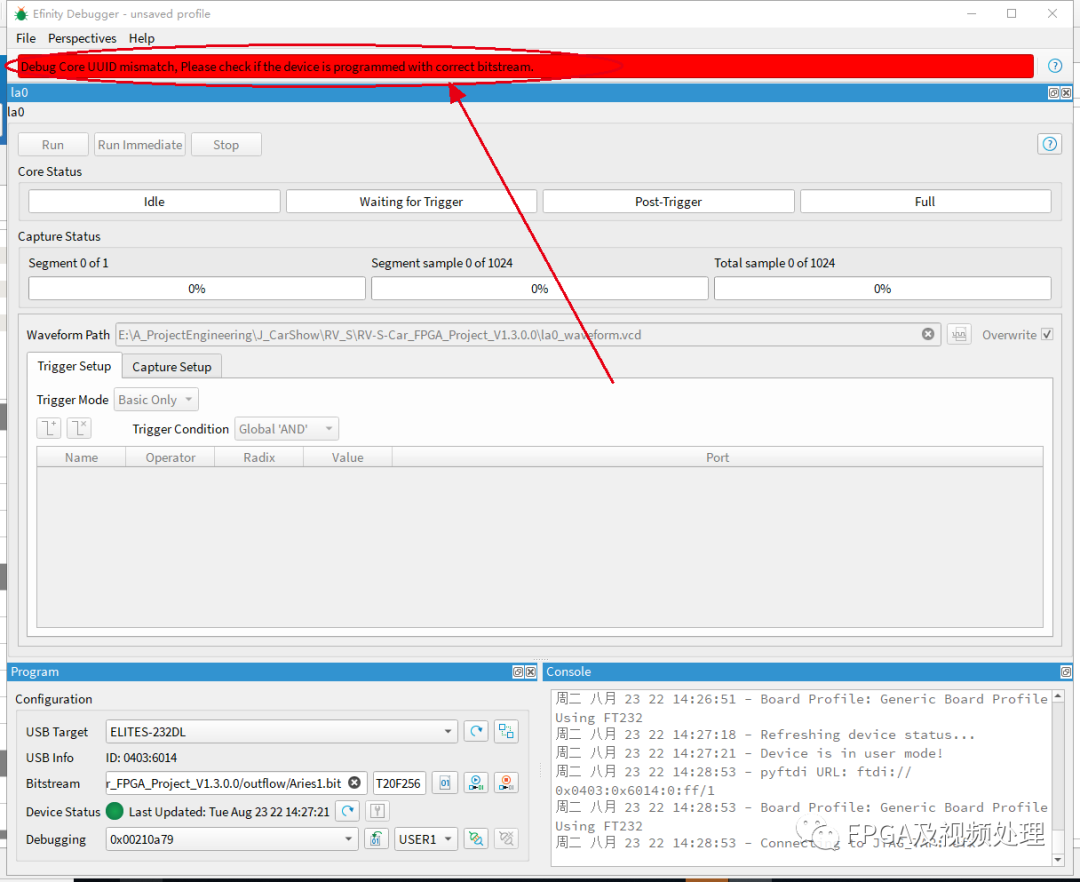

Efinity在Debug時會出現UUID mismatch錯誤。很多剛開始使用的人經常遇到。

Ti60F100內部是一個16Mbit的flash,每個地址對應的是一個8位的數據,所以,地址范圍是....

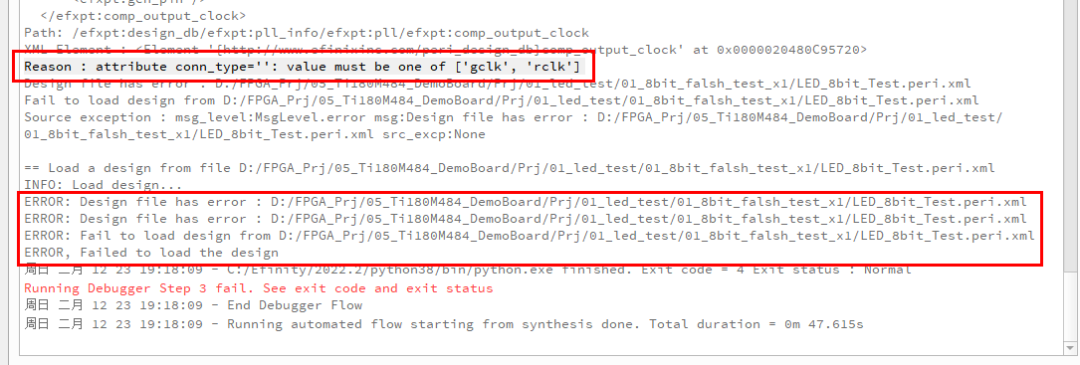

Efinity用新版本的軟件打開老工程時,可能會出現編譯不能通過的情況,并且打不開interface....

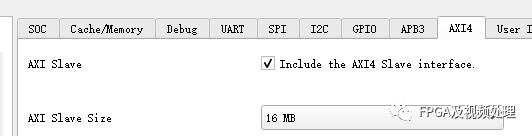

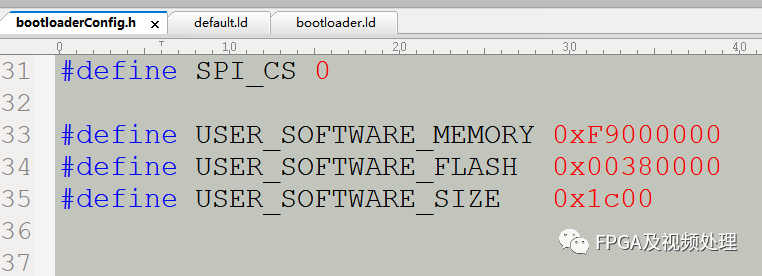

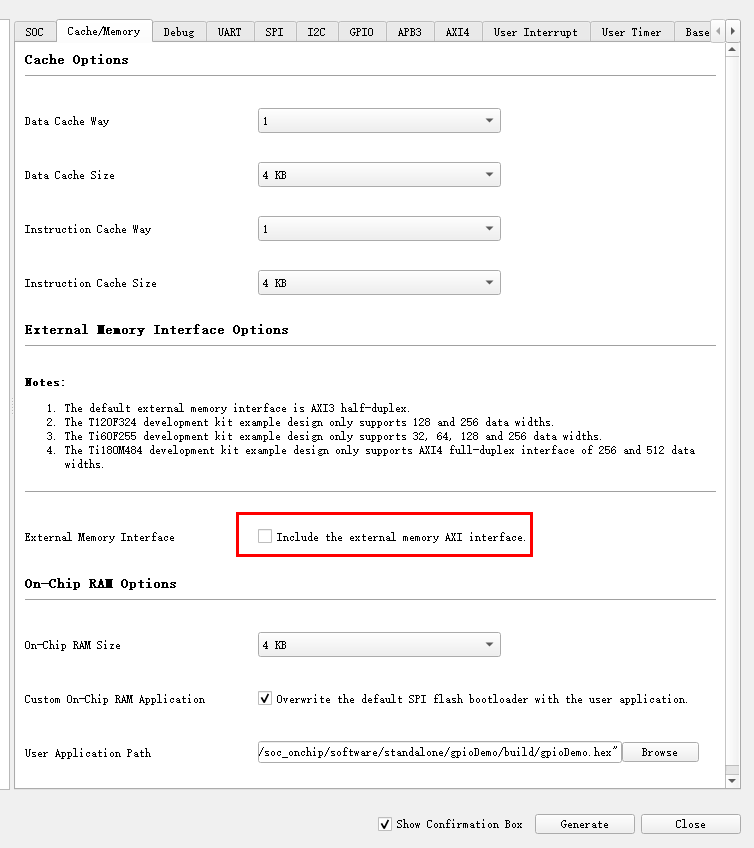

首先片上RAM啟動要在IP上關閉外部存儲,如下圖,Include the external memo....

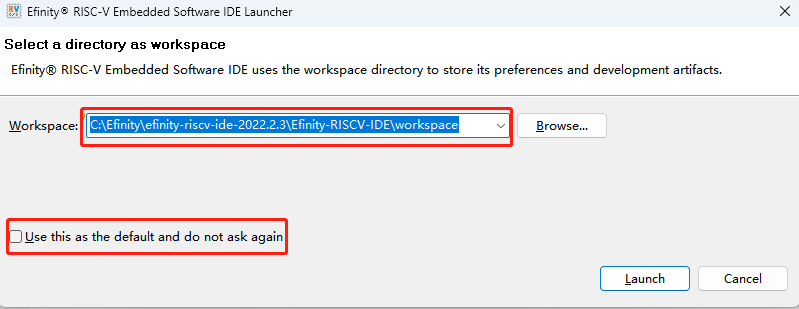

step2: Import工程。選擇Import Projectes... 或者在Project E....

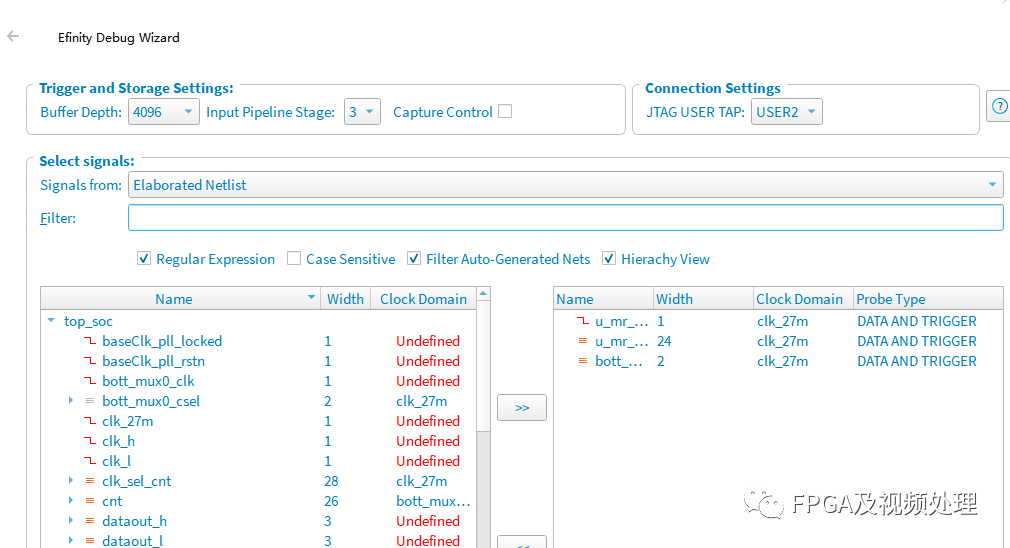

Efinity在Debug時會出現UUID mismatch錯誤。很多剛開始使用的人經常遇到。下面我....

MIPI Dsi的使用相比于CSI多了一些寄存器控制,生成的example直接仿真是可以的,但是修改....

之前在Trion上一直強調驅動PLL要走pllin管腳。但是如果在硬件設計之時沒有注意而把PLL輸入....

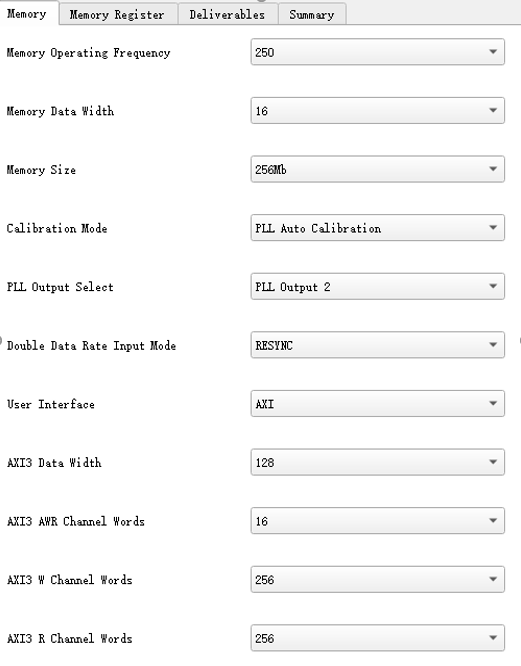

出于功耗的考慮,易靈思在存儲方面提供了對hyperram的支持。在hyperram中使用中有些需要注....

易靈思RAM在使用時可以會遇到一些問題,這里把常用的問題總結下。

在對ram進行初始化時需要指定文件路徑,這里要注意'/'的方向。

最近在幫助客戶分析MIPI的問題,所以有此總結。第一次使用MIPI的人可能不知道怎么在易靈思平臺上下....

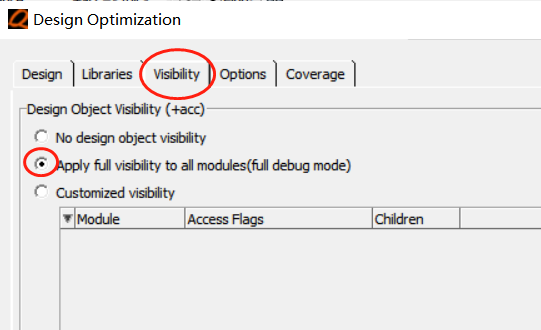

在仿真中為防止信號被優化,會在modelsim仿真的do文件中使用vsim -novopt項,但是Q....

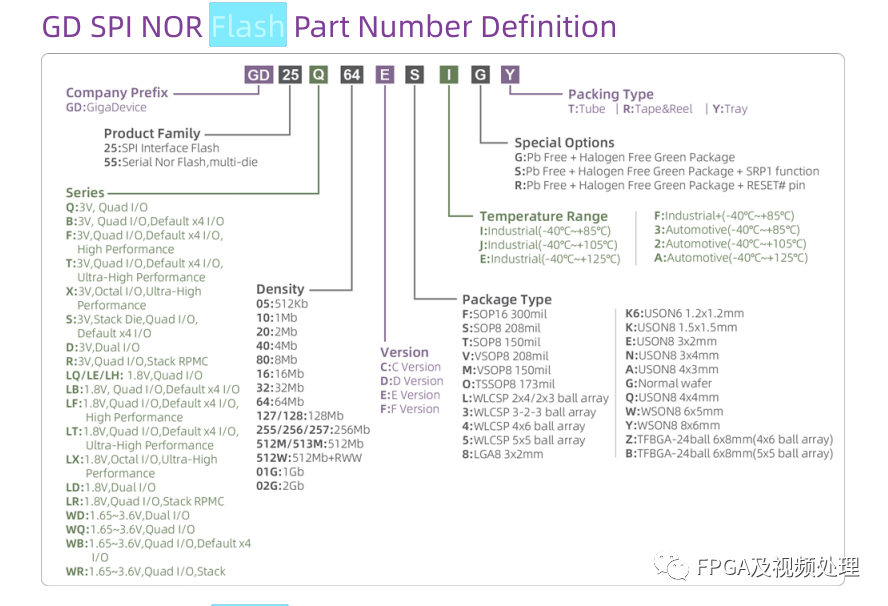

鑒于目前很多客戶有國產化的需求,最近我們安排了一次對GD falsh的測試。

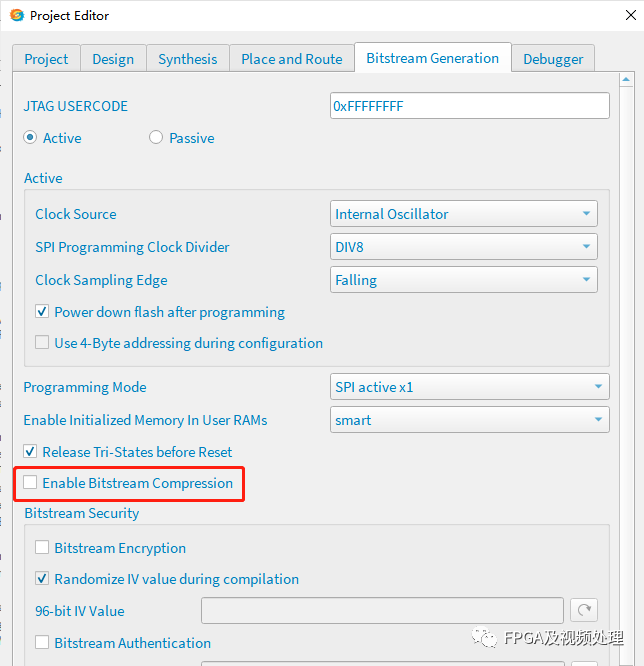

根據客戶的反饋和需求,我們做了一個Ti60壓縮與非壓縮文件的多鏡像與加載時間的驗證。

迄今為止,大家都在吐槽gtkwave debug每次彈窗都會覆蓋上一次彈窗設置好的排序和參數。下面我....

軟件支持版本:目前驗證了2021.2和2022.1,之前的版本應該也可以支持,需要自己驗證。 打開s....